Professional Documents

Culture Documents

An 911

Uploaded by

bulareanuadrianOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

An 911

Uploaded by

bulareanuadrianCopyright:

Available Formats

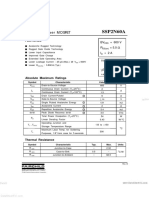

VISHAY SILICONIX

Power ICs and Power MOSFETs

Application Note 911

Power MOSFET in High-Side Operating Modes, Possible Failure Modes, and Failure Signatures

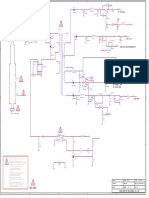

By Kandarp Pandya Power MOSFETs in high-side application can fail under any one of the following modes of operation: (a) High-impedance gate drive (b) Electro-static discharge (ESD) exposure (c) Electrical over-stressed (EOS) operation In most cases, failure analysis of the damaged MOSFET reveals a signature that can point towards a possible cause of failure. (a) High-Impedance Gate Drive A generic schematic configuration for a high-side driver with inductive load is shown in figure 1. A typical gate drive design based on an application-specific integrated circuit (ASIC) caters to the primary gate charge requirements of the MOSFET, which are on the order of a few tens to hundreds of nanocoulombs. An effort to achieve high efficiency and optimize the integration of the ASIC results in low-current (< 50 A) gate drives (V2 referenced to power supply ground) with a high output impedance (> 1 M). This basically satisfies the total gate-charge requirements of the MOSFET. However, to avoid overloading the ASIC, the external gate resistor (R2) in such a design tends to have a high ohmic value (ranging from tens of ohms to several kiloohms). The feedback resistor (R3) also usually has a high ohmic value (ranging from several kiloohms to 1 M). As a result, the source (S) of the power MOSFET (U1) is virtually floating. The effect is magnified during turn-off and recirculation of the energy stored in the inductor (L1). This approach fully satisfies the requirements for steady-state operation, where small amount of current, on the order of a few microamps, is all that is required to maintain the on state. But it can be inadequate for dynamic (transient) turn-on and turn-off operation of MOSFET. In this latter case, the MOSFET switching operation can easily occur in linear mode, which is an unstable and non-characterized area of MOSFET operation (figure 2).

VGate

IDrain 10 A/div

VGS

VSource

VDS

Fig. 2 - Floating Source and Slow Turn-Off

ASIC R2 V2 R3 G

U1

D V1

During turn-on and turn-off, switching power losses are likely to dissipate from a very small area of the active die. The resulting failure signature is high-power burn-out, with a random amount of damage located in the active area of the die. Invariably such failure is labeled as EOS. Another subtle failure evidenced during the analysis of the failed MOSFET (with a virtually floating gate circuit configuration) is in the gate-source area. A DC parameter test of the gate-source area shows out of spec readings. The failure mode is subtle insofar as the leaky device recovers even during the DC parameter test. This failure mode remains under investigation to obtain a full explanation. A failure example of a DPAK power MOSFET is shown in the figures 3, 4, and 5.

APPLICATION NOTE

+ -

+ -

L1

R1

Fig. 1 - Typical High Side Driver Document Number: 69087 Revision: 27-Apr-09 www.vishay.com 1

Application Note 911

Vishay Siliconix

Power MOSFET in High-Side Operating Modes, Possible Failure Modes, and Failure Signatures

Fig. 3 - EOS dDamage Location

Fig. 5 - Damage on Gate Poly

(b) Electro-Static Discharge (ESD) Exposures A second possible scenario arising from a virtually floating gate condition caused by the high impedance of an ASIC driver and/or high gate resistor is increased susceptibility of the gate-source area for damage from ESD or a similar event. In addition to a typical ESD event, high-energy, high-voltage transients of short duration can be generated from energy re-circulation and/or energy interruption from inductive components. With reference to figure 6, these include the low-side load (L1, R1), other parallel connected load (L2, R4), and series feed-in/harness impedance (L3, R5).

L3 U1 D R2 G S

+ -

R5

ASIC

L2 R4

Fig. 4 - Damage on BPSG

+ -

V2 R3 L1 R1

APPLICATION NOTE

V1

Fig. 6 - L1, L2, L3 Sources of Transients

www.vishay.com 2

Document Number: 69087 Revision: 27-Apr-09

Application Note 911

Vishay Siliconix

Power MOSFET in High-Side Operating Modes, Possible Failure Modes, and Failure Signatures

Failure signatures are usually located near the gate termination and in the gate-source area. An example of a DPAK power MOSFET failure is shown in figures 7, 8 and 9.

Fig. 9 - Close-up of ESD Damage

(c) Electrical Over Stressed (EOS) Operation

Fig. 7 - ESD Damage near the Gate-Source

High-energy or high-voltage short-duration transients appearing on the drain-source termination of the MOSFET (figure 6) can result in damage with a variety of signatures. Transients that are faster than the breakdown time of the body diode may produce punctures anywhere in the active area of the drain-source. Such punctures have the appearance of a pin-hole at the damage site. They may be attributed to an ESD event or an ESD-like event arising from other circuit components or parasitics. Where energy/voltage values are not too high but of a sufficient duration to break down the body diode, avalanche results. Avalanche results in extensive damage and in fact destroys the evidence that failure analysis would need to determine the root cause. These are true EOS events. EOS can also result from a mismatch of thermal management and continuous power dissipation in the device, even when the device is fully turned on. When heat-sinking is inadequate, heat can build up in the junction during continuous operation. Eventually a thermal runaway occurs. The device is completely destroyed and also classified as an EOS. D2PAK example: figures 10 to 12 are failure signatures for a D2PAK power MOSFET.

APPLICATION NOTE

Fig. 8 - ESD on the Gate Termination

Document Number: 69087 Revision: 27-Apr-09

www.vishay.com 3

Application Note 911

Vishay Siliconix

Power MOSFET in High-Side Operating Modes, Possible Failure Modes, and Failure Signatures

Fig. 10 - High Power EOS (after Decapsulation)

Fig. 12 - EOS Damage at 50 x Magnification

SO-8 dual example: figures 13 to 15 are another example of a dual SO-8 power MOSFET failure identified as EOS

Fig. 11 - EOS Signature after Removing Top Metal Layer

APPLICATION NOTE

Fig. 13 - Failure near Bond Wire

www.vishay.com 4

Document Number: 69087 Revision: 27-Apr-09

Application Note 911

Vishay Siliconix

Power MOSFET in High-Side Operating Modes, Possible Failure Modes, and Failure Signatures

Fig. 14 - EOS in Active Region

Fig. 15 - Close-up of EOS Damage

SUMMARY

Power MOSFET failures in high-side applications can often be attributed to a high-impedance gate drive creating a virtual floating gate, which in turn increases the susceptibility of the MOSFET to failure during system-generated ESD and EOS scenarios. Failure signatures are associated with: EOS-type damaged inter layer die-electric (ILD) film between the source metal and gate polysilicon ESD-type damage near the gate termination and gate-source area High energy/prolonged operation of the EOS-damaged drain-source active area

APPLICATION NOTE

Document Number: 69087 Revision: 27-Apr-09

www.vishay.com 5

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Irf7205pbf Datasheet MosfetDocument9 pagesIrf7205pbf Datasheet Mosfetnithinmundackal3623No ratings yet

- Fundamentals of Power ElectronicsDocument12 pagesFundamentals of Power ElectronicsYT ZhouNo ratings yet

- Good Book On MosfetDocument37 pagesGood Book On Mosfetabhisheksharma123100% (2)

- Pakistan General Knowledge MCQs Dogar Publishers PDF GuideDocument65 pagesPakistan General Knowledge MCQs Dogar Publishers PDF GuideFarooq HassanNo ratings yet

- 1994 Motorola Semiconductor Master Selection Guide PDFDocument778 pages1994 Motorola Semiconductor Master Selection Guide PDFtrc_wmNo ratings yet

- STF 13 NM 60 NDocument12 pagesSTF 13 NM 60 Nrafaelmattos2015No ratings yet

- UCC28880 700-V Lowest Quiescent Current Off-Line Switcher: 1 Features 3 DescriptionDocument35 pagesUCC28880 700-V Lowest Quiescent Current Off-Line Switcher: 1 Features 3 DescriptionFrancisReisNo ratings yet

- Irfp 140 NDocument9 pagesIrfp 140 NCodinasound CaNo ratings yet

- 60NF06 PDFDocument8 pages60NF06 PDFhectorsevillaNo ratings yet

- Donnees Mosfet NTMYS014N06CL - D-2319325Document8 pagesDonnees Mosfet NTMYS014N06CL - D-2319325Philippe GuillemetNo ratings yet

- AOSP21357Document5 pagesAOSP21357Carlos Roman MonkadaNo ratings yet

- 47N60 Mosfet DatasheetDocument5 pages47N60 Mosfet DatasheetBilles GatesNo ratings yet

- STK0380P: PreliminaryDocument4 pagesSTK0380P: PreliminaryHaider AliNo ratings yet

- A Hybrid-Switch-Based Soft-Switching Inverter For Ultrahigh-Efficiency Traction Motor DrivesDocument8 pagesA Hybrid-Switch-Based Soft-Switching Inverter For Ultrahigh-Efficiency Traction Motor DrivesraghuaadsNo ratings yet

- Sanyo DVD-9408 Reproductor DVD DiagramaDocument44 pagesSanyo DVD-9408 Reproductor DVD DiagramaJuan Sebastián Ledesma100% (1)

- Datasheet Irlr2905Document10 pagesDatasheet Irlr2905Alberto BritosNo ratings yet

- Unisonic Technologies Co., LTD: 20A, 650V N-CHANNEL Power MosfetDocument3 pagesUnisonic Technologies Co., LTD: 20A, 650V N-CHANNEL Power MosfetValci Filho Silva FilhoNo ratings yet

- Addendum For PCN 2004-018-A Bts 5 440 GDocument18 pagesAddendum For PCN 2004-018-A Bts 5 440 Ginvi BarrNo ratings yet

- Mosfet FDH5500Document8 pagesMosfet FDH5500Christina MullinsNo ratings yet

- Tny 279 PN ComDocument24 pagesTny 279 PN ComAnonymous gZYQAPv100% (1)

- Some Theory: Laptop Battery Charging CircuitDocument19 pagesSome Theory: Laptop Battery Charging Circuitramanand yadavNo ratings yet

- IRS2092 Stereo AmplifierDocument10 pagesIRS2092 Stereo AmplifierLuiz Clemente PimentaNo ratings yet

- M8916Document9 pagesM8916ykcorNo ratings yet

- Power IGBTDocument42 pagesPower IGBTNishant SaxenaNo ratings yet

- IRFPF50 Power MOSFET DatasheetDocument9 pagesIRFPF50 Power MOSFET DatasheetLullaby summerNo ratings yet

- Ijiip 073059jeDocument14 pagesIjiip 073059jestrumf381No ratings yet

- RadhardDocument148 pagesRadhardH SMNo ratings yet

- OZ8953 O2MicroDocument32 pagesOZ8953 O2Microluka2stojanovic-10% (1)

- 3 A Step-Down Switching Regulator: ApplicationsDocument47 pages3 A Step-Down Switching Regulator: ApplicationsPedro100% (1)

- SSP2N60A: Advanced Power MOSFETDocument7 pagesSSP2N60A: Advanced Power MOSFETJose M PeresNo ratings yet