Professional Documents

Culture Documents

363

Uploaded by

Dasari Anuroop ReddyOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

363

Uploaded by

Dasari Anuroop ReddyCopyright:

Available Formats

Int. J. Energy Technology and Policy, Vol. 3, No.

3, 2005 253

Analysis and experimental verification of a control

scheme for unified power quality conditioner

Peng-Cheng Zhu*, Xun Li, Yong Kang and

Jian Chen

Power Electronics Research Center

Department of Electrical Engineering

Huazhong University of Science and Technology

Wuhan, 430074, China

Fax: 8602787543658

E-mail: Zhu_pc1977@yahoo.com.cn

E-mail: Xunli@mail.hust.edu.cn

E-mail: Ykang@mail.hust.edu.cn

E-mail: Jchen@mail.hust.edu.cn

*Corresponding author

Abstract: Improving power quality for sensitive load by a Unified Power

Quality Conditioner (UPQC) in a distributed generation system is presented in

this paper. The power balance of a UPQC, consisting of back-to-back

connected series and shunt Active Filters (AF), is analysed. Based on the

analysis a novel control scheme is established in a 2-phase Synchronous

Rotating d-q Frame (SRF). In this control scheme the series AF is controlled as

a current source and makes the input current sinusoidal, while the shunt AF is

controlled as a voltage source and keeps the load voltage in the normal value.

With the proposed control strategy, the UPQC is capable of compensating not

only harmonic and reactive currents of the load but also grid voltage distortion.

There is no harmonic interference between harmonic-producing loads and

harmonic-sensitive loads, which are connected on the common bus. The

performance of a UPQC with the proposed control scheme under nonlinear

load and grid voltage distortion is investigated with simulation as well as

experimental works.

Keywords: UPQC; power balance; d-q frame; control.

Reference to this paper should be made as follows: Zhu, P-C., Li, X., Kang, Y.

and Chen, J. (2005) Analysis and experimental verification of a control

scheme for unified power quality conditioner, Int. J. Energy Technology and

Policy, Vol. 3, No. 3, pp.253268.

Biographical notes: Dr. Peng-Cheng Zhu is a PhD student at the Huazhong

University of Science and Technology. After gaining his bachelors degree in

Applied Electronics (1999) and MSc in Power Electronics and Electric Drive

Systems (2002), he joined the Power Electronics Research Center at the

Huazhong University of Science and Technology. Currently, Dr. Zhu is

pursuing his PhD in Electrical Engineering at the Huazhong University of

Science and Technology. His major research interests include UPS, ac drives,

FACTS, and DSP-based digital control.

Copyright 2005 Inderscience Enterprises Ltd.

254 P-C. Zhu, X. Li, Y. Kang and J. Chen

Dr. Xun Li is a PhD student at the Huazhong University of Science and

Technology. He received his bachelors degree in Applied Electronics (1998)

and is now pursuing his PhD at the Power Electronics Research Center,

Huazhong University of Science and Technology. His major research focused

on power inverter/converter systems and UPS.

Dr. Yong Kang received his BE, ME, and PhD degrees from Huazhong

University of Science and Technology, Wuhan, China, in 1988, 1991, and

1994, respectively. In 1994, he joined the Huazhong University of Science and

Technology as a lecturer. In 1996, he was promoted to Associate Professor. In

1998, he became a full Professor. His research interests focus in power

electronic converters, ac drives, and their digital control techniques. He is the

author of over 30 technical papers.

Jian Chen received his Electrical Engineering degree from the Zhengzhou

Electrical Engineering School, Zhengzhou, China in 1954 and his BE from the

Department of Electrical Engineering, Huazhong Institute of Technology,

Wuhan, China in 1958. He has been working in the Huazhong Institute of

Technology (now Huazhong University of Science and Technology) since

1958. He was promoted to Lecturer in 1963 and became Associate Professor in

1978 and became a full Professor in 1985. He studied power electronics,

microprocessors, and their applications at the University of Toronto, Toronto,

Canada as a visiting scholar from 1980 to 1982. He is an author of three

textbooks and over 60 technical papers. His main research interests include

various power electronic converters, ac drives, and power electronics

applications in electric power systems. He is an IEEE senior member.

1 Introduction

Electrical equipment made of power electronics connected to the grid cause

nonsinusoidal grid currents due to their nonlinear characteristics. The nonsinusoidal

current will cause grid voltage distortion and increase overall reactive power demanded

by the equivalent load. On the other hand, developments in digital

electronics/communications and in process control have increased the number of

sensitive loads that require ideal sinusoidal supply voltages for their proper operation. In

order to meet power quality limits proposed by standards, it is necessary to include some

sort of compensation. Modern solutions for power factor correction and harmonic current

compensation can be found in forms of shunt, TSC or active filters. But if there are

supply voltage imperfections, none of them can provide proper compensation. In the last

few years solutions based on Flexible AC Transmission Systems (FACTS) have

appeared. One of the most attractive devices is the Unified Power Quality Conditioner

(UPQC) (Hideaki and Hirofurni, 1998). An application scheme of UPQC installed in a

distributed generation system is shown in Figure 1. The UPQC acts as an interface device

that links the custom load and the distributed generator together. In this system the UPQC

provides the reactive power needed by the load and absorbs the harmonic current

generated by the nonlinear load, so no matter what kind of load it is, it is taken as a

resistor load for the distributed generator. That is very useful for a small-scale distributed

generation system.

Analysis and experimental verification of a control scheme 255

Figure 1 A general application scheme for UPQC installed in a distributed generation system

Wind

generator UPQC

Load

Distributed generation

Bus 1 Bus 2

According to the basic idea of the UPQC, it consists of a shunt and a series Active Filter

with a common DC-link. The conditioning functions of the UPQC are shared by the

series and shunt AFs. The series AF isolates harmonics between supply and load and

compensates voltage flicker/imbalance. The shunt AF realises current filtering and

negative sequence balancing as well as regulating the DC-link voltage shared by the

AFs (Dusan et al., 2000; Shat et al., 2002; Hideaki et al., 2001). In this control scheme

for UPQC the most important part is the generation of a current compensation signal

for shunt AF and a voltage compensation signal for series AF, both of which are difficult

to achieve.

In this paper, by analysing the active power balance in the UPQC system, a novel

control scheme based on a two-phase synchronous rotating frame is proposed. Different

from conventional methods, the series AF in this scheme is controlled to make the input

current sinusoidal and the shunt AF is controlled to make the output voltage sinusoidal.

Because the series AF is controlled as a sinusoidal current source, its impedance to the

utility harmonic voltage is very large. This enables the series AF to isolate the voltage

distortion from the grid. The shunt AF is controlled to be a sinusoidal voltage source and

since its impedance to the load harmonic current is very small it can absorb the load

harmonic current. Corresponding control schemes for the series AF and shunt AF are

discussed separately. Simulation and experimental results proved the effectiveness of this

control strategy.

2 Active power balance analysis

Figure 2 presents the circuit structure of a UPQC. All the variables are shown in this

figure. The circuit parameters are presented in Table 1. The active power of such a

system is analysed below:

The input active power is indicated in Equation (1),

( ) 1

= = +

in s s L c s

P v i v v i (1)

Because:

3

= +

s L

i i i , then

3 1

= = +

in s s L L L c s

P v i v i v i v i (2)

256 P-C. Zhu, X. Li, Y. Kang and J. Chen

If in the control scheme, the input power source current is controlled to ensure

Equation (3):

= +

s s L L dc

v i v i P (3)

Where indicates system loss. Then we can get:

dc

P

3 1

+ =

L c s

v i v i P

dc

(4)

Because

1 2

=

c s c c

v i v i , then

3 2 1

+ =

L c

v i v i P

dc

(5)

Equation (5) indicates that the total active power flowing into this UPQC system justly

compensates the system loss. If the system loss is neglected, then the input active power

of the two AFs is balanced.

Figure 2 Circuit configuration of a unified power quality conditioner

*

*

*

*

*

*

sa

v

sc

v

sb

v

sa

i

sb

i

sc

i

La

v

Lc

v

La

i

Lb

i

Lc

i

c

i

3

b

i

3

a

i

3

a

i

2

a

i

1 ) , , ( 2 c b a c

v

b

v

2

a

v

2

c

v

1

+ -

) , , ( 1 c b a c

v

N1

N2

b

v

1

a

v

1

N3 N4

1

L

2

L

dc

V

+

-

C

2

C

c

v

2

b

i

2

c

i

2

Lb

v

Ts

b

i

1

c

i

1

Tp

2 dc

i 1 dc

i

1 Q

2

Q

1

C

L

L

L

R

C

i

Load

Series AF Shunt AF

Table 1 Circuit parameter of the UPQC

Inductance of the series AF L

1

5 MH

Capacitance for series AF C

1

3 uF

Inductance for shunt AF L

2

0.15 mH

Capacitance for shunt AF C

2

100 uF

DC bus voltage V

dc

440 V

DC bus capacitor C 3300 uf

Series transformer turning ratio (N

1

: N

2

) 1:3.5

Parallel transformer turning ratio (N

3

: N

4

) 1:1 ( Y )

Standard output voltage

L

(line-line) 380 V

Load inductance L

L

40 mH

Load resister R

L

16

Analysis and experimental verification of a control scheme 257

Because in Equation (3), , ,

s L L

v v i and

dc

P are constant or not changeable. Only

s

i can be

controlled to ensure Equation (3). There are two methods to control

s

i ; one is by

controlling

3

i to control

s

i indirectly, the other is by controlling

s

i directly. The former

is applied in the conventional control scheme for UPQC by controlling the shunt AFs

current, and the voltage compensation is provided by the series AF. The latter is shown in

this paper by controlling the series AFs current directly, while forcing the compensating

current flowing into the shunt AF. The shunt AFs output voltage is controlled to be

sinusoidal in normal value and in phase with the grid voltage, while forcing the distortion

voltage to fall on the series transformer of series AF. The details will be discussed in the

next part.

If the system loss is neglected, it is interesting to find that the active power flowing

direction will change with the grid voltage variation. Figure 1 indicates that the active

power flowing into the series AF is

_ 2

=

series AF c c

P v i , and that the active power flowing

into the shunt AF is

_ 3

=

shunt AF L

P v i .

Under the condition of grid voltage swelling: >

s

v v

L

, then and

.

_

0 >

series AF

P

_

0 <

shunt AF

P

< Under the condition of grid voltage decline: <

s

v v

L

, then and

.

_

0

series AF

P

_

0 >

shunt AF

P

The active power flow chart is presented in Figure 3.

Figure 3 Active power flow chart in different conditions

Series

AF

Shunt

AF

Load

S

T

P

T

in

P

AF Series

P

_

AF Shunt

P

_

Load

P

'

in

P

S

v

L S

v v >

L

v

(a)

>

S L

v v

Series

AF

Shunt

AF

Load

S

T

P

T

in

P

AF Series

P

_

AF Shunt

P

_

Load

P

'

in

P

S

v

L S

v v <

L

v

(b)

<

S L

v v

258 P-C. Zhu, X. Li, Y. Kang and J. Chen

3 Proposed control strategy for UPQC

As discussed the series AF and the shunt AF are controlled to be a sinusoidal current

source and a sinusoidal voltage source separately. Some techniques that have been

applied in rectifiers/inverters can be utilised here with some adjustments. Next we will

discuss them one by one.

3.1 Control scheme for the series AF

The circuit model of the series AF is shown in Figure 2. In this circuit C

1

is combined

with L

1

to realise a low pass filter to filter out the high order harmonics contained in the

series converter PWM output. The low pass filters cut off frequency is selected to about

1/5 of the switching frequency. After filtering, the high order harmonics will not spread

to the power grid. To get proper performance, the series AFs output current should be

controlled sinusoidally and in phase with the grid voltage. That makes the input power

factor unified. Because C

1

is very small, and the current that flows into it is very small

too, it can be neglected when we analyse the series AF. The mathematical model of the

series converter can be presented in synchronous rotating d-q frame as Equation (6):

1

1

1 1 1

1 1 1 1

1

1

1

(

(

(

( (

(

( (

( (

( = + +

( (

(

(

(

( (

(

(

d

d

d

q q q

v R

di

i v L L

dt

di i v v R L

L dt L

2

2

c d

c q

(6)

where:

= d dt is the synchronous angular velocity

R is the resistance of input inductor L

1

, and can be neglected because it is

very small.

Equation (6) indicates that there is a cross coupling between the d axis and the q axis that

will influence the systems dynamic performance. Furthermore in normal conditions the

input voltages contain much harmonics and the system needs a wide responding

bandwidth to keep the input current sinusoidal. To solve this problem the state feed back

decoupling and voltage feed forward mentioned in (Zhu and Chen, 2001) are applied

here. The control diagram and the series AFs model are shown in Figure 4. After

decoupling and feed forward compensation the system in the d and q axis is independent,

the input voltage disturbance is eliminated, and the whole system can be taken as a

two-order system, which makes regulator designing easy. However PID and not the PI

regulator should be applied to increase system bandwidth and restrain 5th and 7th

harmonic currents. A detailed mathematical model for the d axis current PID controller

design is presented in Figure 5. For the q axis the current regulator is the same.

2( , , ) c a b c

v

Analysis and experimental verification of a control scheme 259

Figure 4 Decoupling control diagram for the series AF

PID -1

PID -1

+

+

+

+

+

+

+

+

*

1d

i

*

1q

i

d

i

1

q

i

1

d c

v

2

q c

v

2

d

v

1

q

v

1

Control diagram Series AF model

d c

v

2

q c

v

2

1

L

1

L

1

L

1

L

R s L +

1

1

R s L +

1

1

Figure 5 The d axis current control diagram for PID controller design

+

-

*

1d

i

d

i

1

PID regulator

1 + S

K

S

PWM

1

1

+ S

f

Object system

S

K S K S K

I P d

+ +

2

R S L +

1

1

Here 1 1 +

f

S indicates the feedback delay, 1 1 +

S

S indicates the converter delay and

indicates the converter amplification coefficient. So the object system can be

simplified to a second order continuous system, and a zero-pole placement adjustment

can be applied to design the PID regulator parameters. In the adjustment the system

bandwidth is selected as 2500 rad/s and the damping factor is selected as 0.707. The

whole systems bode diagram with a proper controller design is shown in Figure 6. The

bode diagram proves the stability of the control system.

PWM

K

The PID regulator designed in a continuous model can be transferred to a discrete

control scheme as shown in Equation (7).

( ) ( ) ( ) ( ) ( )

( ) ( ) ( )

1 2

1 1

1

= + +

+

P I P

D

U k U k K K e k K e k

K K e k K e k

(7)

Here the sampling frequency is 10 KHz and the sampling delay is considered. The

controller parameters are selected as K

P

= 78, K

I

= 2, K

D

= 2, K

1

= 40, K

2

= 39. In the

proposed control scheme to get the unity power factor, i

1q

*

is set to be zero and i

1d

*

is set

according to the discussion in the next part.

260 P-C. Zhu, X. Li, Y. Kang and J. Chen

Figure 6 The bode diagram of the series AF

3.2 DC-link voltage control and reference i

1d

*

generation

The DC link voltage must be controlled with the help of the active power flowing from

the grid. Typically the DC link capacitor is not very large. The drawback with having a

very small DC-link capacitor is that the DC link voltage ripple becomes very sensitive to

undesired variations of the active power flow. Such that if during dynamic transience

Equation (3) is not assured, there will be two conditions as below:

3 2 1

+ >

L c

v i v i P

dc

(8)

or

3 2 1

+ <

L c

v i v i P

dc

(9)

Equation (8) indicates that the total power flowing into the system is higher than the

system loss and will cause the DC capacitor voltage increase. The DC capacitor voltage

will rise at a rate that is as much faster as the capacitor is smaller. If the rise time is too

fast, protective control functions may not be able to stop the energy flow and the DC

capacitor voltage will be high enough to destroy the power semiconductors on the same

DC-link. Equation (9) indicates that the flow in power is less than the system loss and

will cause the DC capacitor voltage to decrease. In serious conditions the whole UPQC

system will break down because of the very low DC capacitor voltage. Here some kind of

active power source such as SMES, fuel cell or battery is recommended to install the

DC-link to absorb such active power flickering.

Analysis and experimental verification of a control scheme 261

Because in the proposed control strategy for UPQC the source current is controlled by

series AFs, the current reference for the series AF should make Equation (3) true. Then:

*

2 2

*

0

+ +

=

Ld Ld Lq Lq dc

sd

sd sq

sq

v i v i P

i

v v

i

(10)

dc

P indicates the system loss and can be replaced by a DC-link voltage regulator, so the

i

1d

*

calculation diagram can be achieved in Figure 7.

Figure 7 calculation diagram

*

1d

i

) , ( q d L

v

) , ( q d L

i

) , ( q d s

v

PI

+

+

+

*

dc

V

dc

V

*

1d

i

*'

sd

i

sd

i

2 2

sq sd

Lq Lq Ld Ld

v v

i v i v

+

+

*

sd

i

K

Here K is the proportion coefficient between i and and is related to the transformer

turning ratio of the series AF.

*

sd

*

1d

i

3.3 Control scheme for the shunt AF

To meet the requirement of the load, the shunt AF is controlled as a sinusoidal voltage

source, which is in phase with the input grid voltage. According to Figure 1, the

corresponding equations are presented in Equation (11) and Equation (12) in the same

d-q frame as that used for the series AF.

' '

2 3 2 2

' '

2 3 2 2

= +

= + +

Ld

d d Lq

Lq

q q Ld

dv

i i C v C

dt

dv

i i C v C

dt

(11)

' ' 2

2 2 2 2

2 ' '

2 2 2 2

= +

= + +

d

d Ld q

q

q Lq d

di

v v L i L

dt

di

v v L i L

dt

(12)

Here C C ,

'

2 2

3 =

'

2 2

3 = L L .

262 P-C. Zhu, X. Li, Y. Kang and J. Chen

The mathematical model of the shunt AF is shown graphically in Figure 8. It is clear

that there is a complex coupling relationship between the d axis and q axis that will

decrease the performance of the shunt AF greatly if we do not take care of it. Similar to

the methods applied in the series converter, a control diagram with feed back decoupling

is utilised here as shown in Figure 9. There are two loops in this control diagram,

the outer being the voltage-loop with its output taken as the reference of the inner

current-loop. Each loop has it own feed back state variables to realise cross decoupling. A

detail mathematical model for d axis, which is the same controller design for the q axis, is

presented in Figure 10.

Figure 8 Mathematical model of the shunt AF

S L

'

2

1

S L

'

2

1

'

2

L

'

2

L

+

+

+

+

+ +

d

v

2

q

v

2

d

i

2

q

i

2

d

i

3

q

i

3

Ld

v

Lq

v

'

2

1

SC

'

2

C

'

2

1

SC

'

2

C

Figure 9 Decoupling control diagram for the shunt Af

PI PI

PI PI

'

2

L

'

2

L

*

Ld

v

+

+

+

+

+

+ +

+

+

+

+

+

+

+

*

Lq

v

Ld

v

Lq

v

d

i

3

q

i

3

*

2d

i

d

i

2

*

2q

i

q

i

2

Ld

v

Lq

v

d

v

2

q

v

2

Voltage loop Current loop

'

2

C

'

2

C

Figure 10 The d axis voltage-current double loop control diagram for PI controllers design

+

-

*

2d

i

d

i

2

PI regulator

1 + S

K

S

PWM

Object system

R S L +

'

2

1

1

1

+ S

if

S

K S K

II IP

+

S

K S K

VI VP

+

1

1

+ S

vf

S C

'

2

1

*

Ld

V

+

-

Ld

V

PI regulator

Analysis and experimental verification of a control scheme 263

Similar as it is shown in Figure 10, here 1 1 +

vf

S indicates the voltage loop feedback

delay,

if

indicates the current loop feedback delay, 1

S

S

K

indicates the

converter delay and indicates the converter amplification coefficient. The inner

current loop PI controller parameter can be designed first with a zero-pole placement

adjustment, then the outer voltage loop PI controller coefficients can be achieved with the

same method while taking the inner current loop as a one-order inertia part. The current

loop and voltage loop bode diagrams are plotted in Figure 11, and the plots indicate the

robustness of the shunt converter.

PWM

1 1 + S 1 +

Figure 11 Bode diagram of the shunt AF

(a) Current loop bode diagram (b) Voltage loop bode diagram

Here the sampling frequency is 10 KHz and the sampling delay is considered. The

controller parameters are selected as K

IP

= 2.96, K

II

= 0.04 (current loop), K

VP

= 0.59,

K

VI

= 0.01 (voltage loop). And v

Lq

*

is set to be zero and v

Ld

*

is set to make output voltage

be the normal value V

R

.

L

v

4 Simulation and experimental results

To prove the proposed control scheme for a Unified Power Quality Conditioner system,

simulation works were done with Matlab/Simulink. Here the UPQC system is connected

to a 20 KVA three-phase rectify R load, with power factor 0.8, as shown in Figure 2.

The sampling and switching frequency of both the series and shunt AFs are 10 KHz.

To simulate the serious deteriorate grid voltage, the input voltage varies within the range

of 15% V

R

(V

R

= 220 V and in most practical conditions the utility voltage is about

230 V), and 5% 5th and 7th harmonics are also injected into the grid voltage. The

simulation results are shown in Figures 12 and 13. The figures indicate that whether the

utility voltage is over or under the normal value, the output voltage is always the standard

value and the input current is sinusoidal and in phase with the utility very well. The

UPQC system with the proposed control scheme not only compensates the load harmonic

current but also provides the reactive current for the load. The THD of the input current

S

is controlled less than 5%, although the load current THD is above 26%. The voltage

THD at the load terminal is less than 3%, although the input voltage THD is about 7%.

264 P-C. Zhu, X. Li, Y. Kang and J. Chen

Figure 12

s

= 0.85 V

R

, the voltage, current waveform

Figure 13

s

= 1.15 V

R

, the voltage, current waveform

Analysis and experimental verification of a control scheme 265

According to Table 1 and Figure 2, an experimental prototype of such a UPQC is

constructed. In this system DSP TMS320F240 is used as controller to realise the control

scheme. The current and voltage needed for the control scheme is sensed by a HAL

sensor. Because the power rating of the series part of the UPQC only needs to be about

1/4 of the power rating of the parallel part of the UPQC, the power switches selected for

the series converter are EUPEC IGBT module BSM75GD120DLC (75 A 1200 V) and

the power switches selected for the parallel converter are MITSUBISHI intelligent power

module PM200DSA120 (200 A 1200 V) for a 20 KVA UPQC. A RDC voltage clamp

snubber is connected to the DC bus of each converter, and for such an experimental

system that is enough. For the input of the A/D part of the TMS320F240 LM324 chips is

selected as the signal conditioner, its linearity range is 1 MHz. In a switching circuit the

switching action will cause great noise that will be transmitted especially when switching

with high voltage and current. This noise should be taken off from the control scheme

because the noise may cause wrong action of the converter, which is also the reason why

there is an additional filtering circuit on the control board.

The on board filtering circuit is shown in Figure 14. The parameters ratio was

ordinarily selected as

2

=

3

R R and

4 5

<< R R . Its transfer function is listed below, so that

this circuit can be taken as a second order filtering circuit.

1 3 2 4

1

(1 )(1 )

=

+ +

Vout Vin

SC R SC R

(13)

The filtering parameters are selected to dampen the switching noise at 5 kHz while

causing little amplitude and phase deviation at 50 Hz. Here we selected the parameters

as

1 2 3 5

20 = = = = R R R R K ,

4

100 = R ,

1 2

1 . = = nf C C Additionally, the filtering

performance is very good in the experiment. This part will be added to the paper.

Figure 14 The filtering circuit on the control board

DSP A/D

Port

+

1 R

2 R

3 R

4 R

5 R

1 C

2 C

Vin

Vout

Amplifier

The PWM signal output of the DSP LM311 chips are applied to strengthen the driving

ability; its response time is 200 ns. A Tektronix TDS210 oscilloscope is used to record

the waveform of the currents and voltages. In this prototype, to get enough running time

for the DSP programme the sampling and switching frequency is selected as

6 KHz. To absorb the active power unbalance during the transient performance, a 470 V

DC battery is installed on the DC-link. The experiment results are shown in Figures 15 up

to 18. These figures present the performance of the proposed control scheme in different

266 P-C. Zhu, X. Li, Y. Kang and J. Chen

input voltage conditions. It can be found in the figures that the output voltage will remain

220 V under various conditions, confirming the experiment results perfectly. The

Wavestar

TM

software programme is applied to analyse the voltage and current waveforms

of the experimental results. The THD analysis results are shown in Table 2.

Figure 15 Vs = 187 V, the current and voltage waveforms

(a) 1: output voltage v

LBC

158 V/div

2: load current iLa 50 A/div

(b) 1: compensation vc1a 50 V/div

2: input current isa 50 A/div

(c) 1: input voltage vsa 115 V/div

2: input current isa 50 A/div

(d) 1: output voltage v

LBC

158 V/div

2: current i3a 50 A/div

Figure 16 Vs = 220 V, the current and voltage waveforms

(a) 1: output voltage v

LBC

158 V/div

2: load current iLa 50 A/div

(b) 1: compensation vc1a 50 V/div

2: input current isa 50 A/div

(c) 1: input voltage vsa 310 V/div

2: input current isa 50 A/div

(d) 1: output voltage v

LBC

158 V/div

2: current i3a 50 A/div

Analysis and experimental verification of a control scheme 267

Figure 17 Vs = 245 V, the current and voltage waveforms

(a) 1: output voltage v

LBC

158 V/div

2: load current iLa 50 A/div

(b) 1: compensation vc1a 50 V/div

2: input current isa 50 A/div

(c) 1: input voltage vsa 310 V/div

2: input current isa 50 A/div

(d) 1: output voltage v

LBC

158 V/div

2: current i3a 50 A/div

Figure 18 Load changes from zero to 20KVA, the waveforms of output voltage, load current and

input current

(a) 1: load current of phase A 50 A/div

2: input current of phase A 50 A/div

(b) 1: output line voltage V

BC

158 V/div

2: load current of phase A 50 A/div

Table 2 The THD analysis of the voltage and current

Input voltage V

S

(V) 187 V (%) 220 V (%) 245 V (%)

Input voltage THD 6.03 4.72 3.44

Input current THD 5.27 5.29 6.11

Output voltage THD 2.95 3.11 3.39

Load current THD 25.86 25.86 25.86

268 P-C. Zhu, X. Li, Y. Kang and J. Chen

Table 2 indicates that with the proposed control scheme the current harmonics caused by

the nonlinear load are compensated and isolated form the utility, while the grid voltage

harmonics is isolated by the UPQC too. The waveform analysis also indicates that the

input power factor can be corrected to 0.995 although the load power factor is 0.85. That

means that the UPQC provide the reactive power needed by the load too.

Another interesting phenomenon can be found in both simulation and experiments,

that the phase relationship between the voltage across the series transformer and the

current flowing through it will change as the input voltage varies. This fits the discussion

in Part II very well. When the grid voltage is higher than the nominal value, the phase

difference between vc1a and isa is zero (Figure 17), and there is active power flowing

into the series AF and flowing out of the shut AF. When the grid voltage is lower than the

nominal value, the phase difference vc1a and isa is 180

(Figure 15), and there is active

power flow into the shunt AF and flow out of the series AF. When the grid voltage is

equal to the nominal value, almost only harmonic voltages fall on the series transformer

as shown in Figure 16.

The dynamic performance of the UPQC is shown in Figure 18 when the load jumps

from zero to 20 KVA. It can be seen from the figures that with the i

1d

*

generation strategy

mentioned above the input current increases as soon as the load changes. The whole

system will move into a stable state within five utility periods and the load voltage

changes will be very small.

5 Conclusion

The operation of a Unified Power Quality Conditioner system with the capability of

providing high quality electric power to sensitive loads has been illustrated in this paper.

Based on the active power balance analysis of this UPQC system, a new control scheme

is proposed by controlling the series AF as a current source and the shunt AF as a voltage

source. Simulation and experimental results indicate that with the proposed control

strategy it is able to compensate harmonics of load current and grid voltage. Also, no

harmonic interference occurs between harmonic-producing loads and harmonic-sensitive

loads, which are connected on the common bus.

References

Dusan, G., Vladimir, K. and Alfred, R. (2000) Power quality compensation using universal power

quality conditioning system, IEEE Power Engineering Review, pp.5860.

Hideaki, F. and Hirofurni, A. (1998) The unified power quality conditioner: the integration of

series- and shunt-active filters, IEEE Transaction on Power Electronics, Vol. 13,

pp.315322.

Hideaki, F., Yasuhiro, W. and Hirofunmi, A. (2001) Transient analysis of a unified power flow

controller and its application to design of the dc-link capacitor, IEEE Transaction on Power

Electronics, Vol. 16, pp.735740.

Shat, R.E.I., Kazerani, M. and Salama, M.M.A. (2002) Power quality improvement in 3-phase

3-wire distribution systems using modular active power filter, Elsevier Electric Power

Systems Research, pp.876880.

Zhu, P. and Chen, J. (2001) The power conversion system performance of a super conducting

magnetic energy storage unit, IEEE Power Electronics and Drive Systems Conference,

pp.611617.

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Soil LiquefactionDocument12 pagesSoil LiquefactionKikin Kikin PelukaNo ratings yet

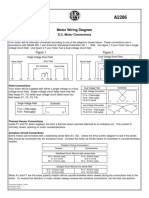

- Motor Wiring Diagram: D.C. Motor ConnectionsDocument1 pageMotor Wiring Diagram: D.C. Motor Connectionsczds6594No ratings yet

- Letter of MotivationDocument4 pagesLetter of Motivationjawad khalidNo ratings yet

- BCP-8000 User's ManualDocument36 pagesBCP-8000 User's ManualAsad PatelNo ratings yet

- Telco XPOL MIMO Industrial Class Solid Dish AntennaDocument4 pagesTelco XPOL MIMO Industrial Class Solid Dish AntennaOmar PerezNo ratings yet

- 2 - Elements of Interior DesignDocument4 pages2 - Elements of Interior DesignYathaarth RastogiNo ratings yet

- Compare Blocks - ResultsDocument19 pagesCompare Blocks - ResultsBramantika Aji PriambodoNo ratings yet

- 中美两国药典药品分析方法和方法验证Document72 pages中美两国药典药品分析方法和方法验证JasonNo ratings yet

- Phenomenological of in Church and TV WorshipDocument18 pagesPhenomenological of in Church and TV WorshipCindy TirtaNo ratings yet

- CP 343-1Document23 pagesCP 343-1Yahya AdamNo ratings yet

- Traffic Violation Monitoring with RFIDDocument59 pagesTraffic Violation Monitoring with RFIDShrëyãs NàtrájNo ratings yet

- Conjoint Analysis Basic PrincipleDocument16 pagesConjoint Analysis Basic PrinciplePAglu JohnNo ratings yet

- Interpreting Piping and Instrumentation DiagramsDocument41 pagesInterpreting Piping and Instrumentation DiagramsFredric Tun100% (2)

- 7890 Parts-Guide APDocument4 pages7890 Parts-Guide APZia HaqNo ratings yet

- Chemistry Implementation: Name: Rasheed Campbell School: Kingston College Candidate #.: Centre #: 100057Document12 pagesChemistry Implementation: Name: Rasheed Campbell School: Kingston College Candidate #.: Centre #: 100057john brownNo ratings yet

- Smart Note Taker Saves Time With Air WritingDocument17 pagesSmart Note Taker Saves Time With Air WritingNagarjuna LokkuNo ratings yet

- Troubleshooting Hydraulic Circuits: Fluid PowerDocument32 pagesTroubleshooting Hydraulic Circuits: Fluid PowerMi LuanaNo ratings yet

- HVCCI UPI Form No. 3 Summary ReportDocument2 pagesHVCCI UPI Form No. 3 Summary ReportAzumi AyuzawaNo ratings yet

- Metal Framing SystemDocument56 pagesMetal Framing SystemNal MénNo ratings yet

- Virchow TriadDocument6 pagesVirchow Triadarif 2006No ratings yet

- Direct From: 1St Quarter 2020Document23 pagesDirect From: 1St Quarter 2020JeanNo ratings yet

- Reflective Essay 4Document1 pageReflective Essay 4Thirdy AngelesNo ratings yet

- The Simple PendulumDocument5 pagesThe Simple PendulumDexter TorringtonNo ratings yet

- Antennas Since Hertz and MarconiDocument7 pagesAntennas Since Hertz and MarconiTaiwo Ayodeji100% (1)

- Clausius TheoremDocument3 pagesClausius TheoremNitish KumarNo ratings yet

- Canon imageFORMULA DR-X10CDocument208 pagesCanon imageFORMULA DR-X10CYury KobzarNo ratings yet

- GIS AccidentsDocument5 pagesGIS Accidentsali110011No ratings yet

- Digital Communication QuestionsDocument14 pagesDigital Communication QuestionsNilanjan BhattacharjeeNo ratings yet

- Background of The Study Statement of ObjectivesDocument4 pagesBackground of The Study Statement of ObjectivesEudelyn MelchorNo ratings yet

- Transport of OxygenDocument13 pagesTransport of OxygenSiti Nurkhaulah JamaluddinNo ratings yet