Professional Documents

Culture Documents

74 LVT 14 D

Uploaded by

Sriharsha KosarajuOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

74 LVT 14 D

Uploaded by

Sriharsha KosarajuCopyright:

Available Formats

74LVT14

3.3 V hex inverter Schmitt trigger

Rev. 02 25 April 2008 Product data sheet

1. General description

The 74LVT14 is a high-performance BiCMOS product designed for VCC operation at 3.3 V. It is capable of transforming slowly changing input signals into sharply dened, jitter free output signals. In addition, it has a greater noise margin than conventional inverters. Each circuit contains a Schmitt trigger followed by a Darlington level shifter and a phase splitter driving a TTL totem-pole output. The Schmitt trigger uses positive feedback to effectively speed-up slow input transitions, and provide different input threshold voltages for positive-going and negative-going inputs. The threshold differential (typically 600 mV) is determined internally by resistor ratios and is insensitive to temperature and supply voltage variations.

2. Features

I I I I I I I Different positive and negative going input threshold voltages Tolerant of slow input transitions High noise immunity TTL input and output switching levels Output capability: +32 mA/20 mA Latch-up protection exceeds 500 mA per JESD78 class II level A ESD protection: N HBM JESD22-A114E exceeds 2000 V N MM JESD22-A115-A exceeds 200 V

3. Ordering information

Table 1. Ordering information Package Temperature range Name 74LVT14D 74LVT14DB 74LVT14PW 74LVT14BQ 40 C to +85 C 40 C to +85 C 40 C to +85 C 40 C to +85 C SO14 SSOP14 TSSOP14 Description plastic small outline package; 14 leads; body width 7.5 mm plastic shrink small outline package; 14 leads; body width 5.3 mm plastic thin shrink small outline package; 14 leads; body width 4.4 mm Version SOT108-1 SOT337-1 SOT402-1 SOT762-1 Type number

DHVQFN14 plastic dual in-line compatible thermal enhanced very thin quad at package; no leads; 14 terminals; body 2.5 4.5 0.85 mm

NXP Semiconductors

74LVT14

3.3 V hex inverter Schmitt trigger

4. Functional diagram

3 1 1A 1Y 2 5 4

2A

2Y

3A

3Y

4A

4Y

8 11 10

11

5A

5Y

10 13 12

13

6A

6Y

12

Y

mna025

mna204

001aac497

Fig 1.

Logic symbol

Fig 2.

IEC logic symbol

Fig 3.

Logic diagram

5. Pinning information

5.1 Pinning

74LVT14

terminal 1 index area 14 VCC 13 6A 12 6Y 11 5A GND(1) 7 8 10 5Y 9 GND 4Y 4A 1A 2 3 4 5 6 1 1Y 14 VCC 13 6A 12 6Y 11 5A 10 5Y 9 8

001aah920

74LVT14

1A 1Y 2A 2Y 3A 3Y GND 1 2 3 4 5 6 7

2A 2Y 3A 3Y

4A 4Y

001aah921

Transparent top view

(1) The die substrate is attached to this pad using a conductive die attach material. It cannot be used as a supply pin or input.

Fig 4.

Pin conguration for SO14 and (T)SSOP14

Fig 5.

Pin conguration for DHVQFN14

74LVT14_2

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 02 25 April 2008

2 of 13

NXP Semiconductors

74LVT14

3.3 V hex inverter Schmitt trigger

5.2 Pin description

Table 2. Symbol 1A to 6A 1Y to 6Y GND VCC Pin description Pin 1, 3, 5, 9, 11, 13 2, 4, 6, 8, 10, 12 7 14 Description data input data output ground (0 V) positive supply voltage

6. Functional description

Table 3. Inputs nA L H

[1] H = HIGH voltage level; L = LOW voltage level.

Function selection Output nY H L

7. Limiting values

Table 4. Limiting values [1] In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V). Symbol VCC VI VO IIK IOK IO Tstg Tj Ptot

[1] [2] [3]

Parameter supply voltage input voltage output voltage input clamping current output clamping current output current storage temperature junction temperature total power dissipation

Conditions

[2]

Min 0.5 0.5 0.5 50 50 32 65

Max +4.6 +7.0 +7.0 64 +150 +150 500

Unit V V V mA mA mA mA C C mW

output in OFF or HIGH state VI < 0 V VO < 0 V output in LOW state output in HIGH state

[2]

Tamb = 40 C to +85 C

[3]

The performance capability of a high-performance integrated circuit in conjunction with its thermal environment can create junction temperatures which are detrimental to reliability. The maximum junction temperature of this integrated circuit should not exceed 150 C. The input and output negative voltage ratings may be exceeded if the input and output clamp current ratings are observed. For SO14 packages: above 70 C derate linearly with 8 mW/K. For SSOP14 and TSSOP14 packages: above 60 C derate linearly with 5.5 mW/K. For DHVQFN14 packages: above 60 C derate linearly with 4.5 mW/K.

74LVT14_2

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 02 25 April 2008

3 of 13

NXP Semiconductors

74LVT14

3.3 V hex inverter Schmitt trigger

8. Recommended operating conditions

Table 5. Symbol VCC VI IOH IOL Tamb t/V Recommended operating conditions Parameter supply voltage input voltage HIGH-level output current LOW-level output current ambient temperature input transition rise and fall rate in free air output enabled Conditions Min 2.7 0 20 40 0 Typ Max 3.6 5.5 32 +85 10 Unit V V mA mA C ns/V

9. Static characteristics

Table 6. Static characteristics At recommended operating conditions. Voltages are referenced to GND (ground = 0 V). Symbol Parameter VT+ VT VH VIK VIH VIL VOH positive-going threshold voltage hysteresis voltage input clamping voltage HIGH-level input voltage LOW-level input voltage HIGH-level output voltage VCC = 2.7 V to 3.6 V; IOH = 100 A VCC = 2.7 V; IOH = 6 mA VCC = 3.0 V; IOH = 20 mA VOL LOW-level output voltage VCC = 2.7 V; IOL = 100 A VCC = 2.7 V; IOL = 24 mA VCC = 3.0 V; IOL = 32 mA II IOFF ICC input leakage current power-off leakage current supply current VCC = 0 V or 3.6 V; VI = 5.5 V VCC = 3.6 V; VI = VCC or GND VCC = 0 V; VI or VO = 0 V to 4.5 V VCC = 3.6 V; VI = GND or VCC; IO = 0 A outputs HIGH outputs LOW ICC additional supply current per input pin; VCC = 3.0 V to 3.6 V; one input = VCC 0.6 V other inputs at VCC or GND VI = 0 V or 3.0 V

[2]

Conditions VCC = 3.3 V; see Figure 7 VCC = 3.3 V; see Figure 7 VCC = 2.7 V; IIK = 18 mA 1.5 0.9 0.4 1.2 2.0 2.4 2.0 -

40 C to +85 C Min Typ[1] 1.7 1.1 0.6 1.5 Max 2.0 1.3 0.8 0.2 0.5 0.5 10 1 100 0.02 3 0.2

Unit V V V V V V V V V V V A A A mA mA mA

negative-going threshold voltage VCC = 3.3 V; see Figure 7

VCC 0.2 -

CI

[1] [2]

input capacitance

pF

All typical values are measured at VCC = 3.3 V (unless stated otherwise) and Tamb = 25 C. This is the increase in the supply current for each input at the specied voltage level other than VCC or GND.

74LVT14_2

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 02 25 April 2008

4 of 13

NXP Semiconductors

74LVT14

3.3 V hex inverter Schmitt trigger

10. Dynamic characteristics

Table 7. Dynamic characteristics Voltages are referenced to GND (ground = 0 V). For test circuit see Figure 8. Symbol Parameter tPLH LOW to HIGH propagation delay Conditions nA to nY VCC = 2.7 V VCC = 3.3 V + 0.3 V tPHL HIGH to LOW propagation delay nA to nY VCC = 2.7 V VCC = 3.3 V + 0.3 V

[1] Typical values are measured at Tamb = 25 C and VCC = 3.3 V.

40 C to +85 C Min 1.0 1.0 Typ[1] 3.8 3.2 Max 6.9 5.7 4.1 4.5

Unit

ns ns ns ns

11. Waveforms

VI nA input GND t PHL VOH nY output VOL VM VM

mna344

VM

VM

t PLH

See Table 8 for measurement points. VOL and VOH are typical output voltage levels that occur with the output load.

Fig 6.

nA Input to nY output propagation delays

VO VT+ VI VT VH

VH VT VT+

VI

mna207

VO

mna208

a. Transfer characteristics Fig 7. Denition of VT+, VT and VH

b. Voltage levels

74LVT14_2

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 02 25 April 2008

5 of 13

NXP Semiconductors

74LVT14

3.3 V hex inverter Schmitt trigger

Table 8. VCC

Measurement points Input VM 1.5 V Output VM 1.5 V

2.7 V to 3.6 V

VI negative pulse 0V

tW 90 % VM 10 % tf tr tr tf 90 % VM 10 % tW VM VM

VI positive pulse 0V

VCC PULSE GENERATOR VI DUT

RT CL RL

VO

001aaf615

Test data is given in given in Table 9. Denitions for test circuit: RL = Load resistance; CL = Load capacitance including jig and probe capacitance; RT = Termination resistance should be equal to output impedance Zo of the pulse generator.

Fig 8. Table 9. Supply VCC

Load circuitry for switching times Test data Input pulse requirements VI 2.7 V Repetition rate tW 10 MHz 500 ns tr, tf 2.5 ns Load RL 500 CL 50 pF

2.7 V to 3.3 V

74LVT14_2

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 02 25 April 2008

6 of 13

NXP Semiconductors

74LVT14

3.3 V hex inverter Schmitt trigger

12. Package outline

SO14: plastic small outline package; 14 leads; body width 3.9 mm SOT108-1

A X

c y HE v M A

Z 14 8

Q A2 pin 1 index Lp 1 e bp 7 w M L detail X A1 (A 3) A

2.5 scale

5 mm

DIMENSIONS (inch dimensions are derived from the original mm dimensions) UNIT mm A max. 1.75 A1 0.25 0.10 A2 1.45 1.25 A3 0.25 0.01 bp 0.49 0.36 c 0.25 0.19 D (1) 8.75 8.55 E (1) 4.0 3.8 0.16 0.15 e 1.27 0.05 HE 6.2 5.8 L 1.05 Lp 1.0 0.4 Q 0.7 0.6 0.028 0.024 v 0.25 0.01 w 0.25 0.01 y 0.1 Z (1) 0.7 0.3

0.010 0.057 inches 0.069 0.004 0.049

0.019 0.0100 0.35 0.014 0.0075 0.34

0.244 0.039 0.041 0.228 0.016

0.028 0.004 0.012

8 o 0

Note 1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included. OUTLINE VERSION SOT108-1 REFERENCES IEC 076E06 JEDEC MS-012 JEITA EUROPEAN PROJECTION

ISSUE DATE 99-12-27 03-02-19

Fig 9.

74LVT14_2

Package outline SOT108-1 (SO14)

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 02 25 April 2008

7 of 13

NXP Semiconductors

74LVT14

3.3 V hex inverter Schmitt trigger

SSOP14: plastic shrink small outline package; 14 leads; body width 5.3 mm

SOT337-1

A X

c y HE v M A

Z 14 8

Q A2 A1 pin 1 index Lp L 1 bp 7 w M detail X (A 3) A

2.5 scale

5 mm

DIMENSIONS (mm are the original dimensions) UNIT mm A max. 2 A1 0.21 0.05 A2 1.80 1.65 A3 0.25 bp 0.38 0.25 c 0.20 0.09 D (1) 6.4 6.0 E (1) 5.4 5.2 e 0.65 HE 7.9 7.6 L 1.25 Lp 1.03 0.63 Q 0.9 0.7 v 0.2 w 0.13 y 0.1 Z (1) 1.4 0.9 8 o 0

o

Note 1. Plastic or metal protrusions of 0.25 mm maximum per side are not included. OUTLINE VERSION SOT337-1 REFERENCES IEC JEDEC MO-150 JEITA EUROPEAN PROJECTION

ISSUE DATE 99-12-27 03-02-19

Fig 10. Package outline SOT337-1 (SSOP14)

74LVT14_2 NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 02 25 April 2008

8 of 13

NXP Semiconductors

74LVT14

3.3 V hex inverter Schmitt trigger

TSSOP14: plastic thin shrink small outline package; 14 leads; body width 4.4 mm

SOT402-1

c y HE v M A

14

Q A2 pin 1 index A1 Lp L (A 3) A

1

e bp

7

w M detail X

2.5 scale

5 mm

DIMENSIONS (mm are the original dimensions) UNIT mm A max. 1.1 A1 0.15 0.05 A2 0.95 0.80 A3 0.25 bp 0.30 0.19 c 0.2 0.1 D (1) 5.1 4.9 E (2) 4.5 4.3 e 0.65 HE 6.6 6.2 L 1 Lp 0.75 0.50 Q 0.4 0.3 v 0.2 w 0.13 y 0.1 Z (1) 0.72 0.38 8 o 0

o

Notes 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included. 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included. OUTLINE VERSION SOT402-1 REFERENCES IEC JEDEC MO-153 JEITA EUROPEAN PROJECTION ISSUE DATE 99-12-27 03-02-18

Fig 11. Package outline SOT402-1 (TSSOP14)

74LVT14_2 NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 02 25 April 2008

9 of 13

NXP Semiconductors

74LVT14

3.3 V hex inverter Schmitt trigger

DHVQFN14: plastic dual in-line compatible thermal enhanced very thin quad flat package; no leads; SOT762-1 14 terminals; body 2.5 x 3 x 0.85 mm

A A1 E c

terminal 1 index area

detail X

terminal 1 index area e 2 L

e1 b 6 v M C A B w M C y1 C

C y

1 Eh 14

7 e 8

13 Dh 0

9 X 2.5 scale 5 mm

DIMENSIONS (mm are the original dimensions) UNIT mm A(1) max. 1 A1 0.05 0.00 b 0.30 0.18 c 0.2 D (1) 3.1 2.9 Dh 1.65 1.35 E (1) 2.6 2.4 Eh 1.15 0.85 e 0.5 e1 2 L 0.5 0.3 v 0.1 w 0.05 y 0.05 y1 0.1

Note 1. Plastic or metal protrusions of 0.075 mm maximum per side are not included. OUTLINE VERSION SOT762-1 REFERENCES IEC --JEDEC MO-241 JEITA --EUROPEAN PROJECTION ISSUE DATE 02-10-17 03-01-27

Fig 12. Package outline SOT762-1 (DHVQFN14)

74LVT14_2 NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 02 25 April 2008

10 of 13

NXP Semiconductors

74LVT14

3.3 V hex inverter Schmitt trigger

13. Abbreviations

Table 10. Acronym BiCMOS DUT ESD HBM TTL Abbreviations Description Integrated Bipolar junction transistors and CMOS Device Under Test ElectroStatic Discharge Human Body Model Transistor-Transistor Logic

14. Revision history

Table 11. 74LVT14_2 Modications: Revision history Release date 20080425 Data sheet status Product data sheet Change notice Supersedes 74LVT14_1 Document ID

The format of this data sheet has been redesigned to comply with the new identity guidelines of NXP Semiconductors. Legal texts have been adapted to the new company name where appropriate. Quick reference section removed. DHVQFN14 package added to Section 3 Ordering information and Section 12 Package outline. Section 13 Abbreviations added. Product specication -

74LVT14_1

19960828

74LVT14_2

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 02 25 April 2008

11 of 13

NXP Semiconductors

74LVT14

3.3 V hex inverter Schmitt trigger

15. Legal information

15.1 Data sheet status

Document status[1][2] Objective [short] data sheet Preliminary [short] data sheet Product [short] data sheet

[1] [2] [3]

Product status[3] Development Qualication Production

Denition This document contains data from the objective specication for product development. This document contains data from the preliminary specication. This document contains the product specication.

Please consult the most recently issued document before initiating or completing a design. The term short data sheet is explained in section Denitions. The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

15.2 Denitions

Draft The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information. Short data sheet A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales ofce. In case of any inconsistency or conict with the short data sheet, the full data sheet shall prevail.

malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customers own risk. Applications Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specied use without further testing or modication. Limiting values Stress above one or more limiting values (as dened in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability. Terms and conditions of sale NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/prole/terms, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conict between information in this document and such terms and conditions, the latter will prevail. No offer to sell or license Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

15.3 Disclaimers

General Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Right to make changes NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof. Suitability for use NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or

15.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

16. Contact information

For more information, please visit: http://www.nxp.com For sales ofce addresses, please send an email to: salesaddresses@nxp.com

74LVT14_2

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 02 25 April 2008

12 of 13

NXP Semiconductors

74LVT14

3.3 V hex inverter Schmitt trigger

17. Contents

1 2 3 4 5 5.1 5.2 6 7 8 9 10 11 12 13 14 15 15.1 15.2 15.3 15.4 16 17 General description . . . . . . . . . . . . . . . . . . . . . . 1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Ordering information . . . . . . . . . . . . . . . . . . . . . 1 Functional diagram . . . . . . . . . . . . . . . . . . . . . . 2 Pinning information . . . . . . . . . . . . . . . . . . . . . . 2 Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 3 Functional description . . . . . . . . . . . . . . . . . . . 3 Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 3 Recommended operating conditions. . . . . . . . 4 Static characteristics. . . . . . . . . . . . . . . . . . . . . 4 Dynamic characteristics . . . . . . . . . . . . . . . . . . 5 Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Package outline . . . . . . . . . . . . . . . . . . . . . . . . . 7 Abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Revision history . . . . . . . . . . . . . . . . . . . . . . . . 11 Legal information. . . . . . . . . . . . . . . . . . . . . . . 12 Data sheet status . . . . . . . . . . . . . . . . . . . . . . 12 Denitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Disclaimers . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Trademarks . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Contact information. . . . . . . . . . . . . . . . . . . . . 12 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section Legal information.

NXP B.V. 2008.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com Date of release: 25 April 2008 Document identifier: 74LVT14_2

You might also like

- Sonar AbsDocument2 pagesSonar AbsSriharsha KosarajuNo ratings yet

- Or CadDocument1 pageOr CadSriharsha KosarajuNo ratings yet

- Sample Bank StatementDocument1 pageSample Bank StatementMuhammad Sanaullah SanamNo ratings yet

- Tps 76325Document20 pagesTps 76325Sriharsha KosarajuNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Mabo V Queensland (No 2) ( - Mabo Case - ) (1992) HCA 23 (1992) 175 CLR 1 (3 June 1992)Document245 pagesMabo V Queensland (No 2) ( - Mabo Case - ) (1992) HCA 23 (1992) 175 CLR 1 (3 June 1992)lintang.alit141214No ratings yet

- Cortes Constitutional Foundations of Privacy in Emerging Trends in LawDocument3 pagesCortes Constitutional Foundations of Privacy in Emerging Trends in LawAce Reblora IINo ratings yet

- Remedial Law Q and ADocument17 pagesRemedial Law Q and Akonvan100% (2)

- Clutario v. CADocument2 pagesClutario v. CAKrisha Marie CarlosNo ratings yet

- MTLBDocument121 pagesMTLBKIM KYRISH DELA CRUZNo ratings yet

- CD - Holy See vs. Rosario 238 SCRA 524Document3 pagesCD - Holy See vs. Rosario 238 SCRA 524Sai Pastrana100% (2)

- Salonga Vs Cruz PanoDocument1 pageSalonga Vs Cruz PanoGeorge Demegillo Rocero100% (3)

- Brokenshire College: Form C. Informed Consent Assessment FormDocument2 pagesBrokenshire College: Form C. Informed Consent Assessment Formgeng gengNo ratings yet

- Britannia: Business Conduct (COBC) For Its Employees. This Handbook Covers The CodeDocument17 pagesBritannia: Business Conduct (COBC) For Its Employees. This Handbook Covers The CodevkvarshakNo ratings yet

- Irish Independent Rate CardDocument2 pagesIrish Independent Rate CardPB VeroNo ratings yet

- Skyline Software Systems, Inc. v. Keyhole, Inc Et Al - Document No. 74Document3 pagesSkyline Software Systems, Inc. v. Keyhole, Inc Et Al - Document No. 74Justia.comNo ratings yet

- 2 PNOC v. Court of Appeals, 457 SCRA 32Document37 pages2 PNOC v. Court of Appeals, 457 SCRA 32Aivy Christine ManigosNo ratings yet

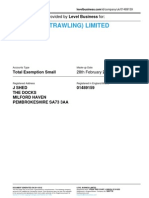

- RAWLINGS (TRAWLING) LIMITED - Company Accounts From Level BusinessDocument7 pagesRAWLINGS (TRAWLING) LIMITED - Company Accounts From Level BusinessLevel BusinessNo ratings yet

- 10 Overseas Bank Vs CA & Tapia PDFDocument10 pages10 Overseas Bank Vs CA & Tapia PDFNicoleAngeliqueNo ratings yet

- Trump Presidency 33 - May 5th, 2018 To May 14th, 2018Document513 pagesTrump Presidency 33 - May 5th, 2018 To May 14th, 2018FW040100% (1)

- April 2013 PDFDocument22 pagesApril 2013 PDFJasonSpringNo ratings yet

- CH10 Finan Acc Long Term Liab LectDocument28 pagesCH10 Finan Acc Long Term Liab LectAbdul KabeerNo ratings yet

- Fund Flow StatementDocument21 pagesFund Flow StatementSarvagya GuptaNo ratings yet

- Spouses Firme Vs BukalDocument2 pagesSpouses Firme Vs Bukalpayumomichael2276No ratings yet

- AptitudeDocument2 pagesAptitudedodaf78186No ratings yet

- Republic Vs HerbietoDocument2 pagesRepublic Vs HerbietoMichelle Vale CruzNo ratings yet

- Prophetic Graph Eng-0.17Document1 pageProphetic Graph Eng-0.17Judaz Munzer100% (1)

- Miranda V AguirreDocument15 pagesMiranda V AguirrePam RamosNo ratings yet

- Full Download Technical Communication 12th Edition Markel Test BankDocument35 pagesFull Download Technical Communication 12th Edition Markel Test Bankchac49cjones100% (22)

- Security Bank v. CADocument3 pagesSecurity Bank v. CASiobhan Robin100% (1)

- BL-5-Negotiable Instruments ActDocument46 pagesBL-5-Negotiable Instruments ActAbhishekNo ratings yet

- Revision Guide For AMD Athlon 64 and AMD Opteron Processors: Publication # Revision: Issue DateDocument85 pagesRevision Guide For AMD Athlon 64 and AMD Opteron Processors: Publication # Revision: Issue DateSajith Ranjeewa SenevirathneNo ratings yet

- Healing Verses in QuranDocument2 pagesHealing Verses in QuranBadrul Ahsan100% (1)

- Green Delta Life Insurance at Power PointDocument12 pagesGreen Delta Life Insurance at Power Pointapi-3844412100% (2)

- Phase I - Price List (Towers JKLMNGH)Document1 pagePhase I - Price List (Towers JKLMNGH)Bharat ChatrathNo ratings yet