Professional Documents

Culture Documents

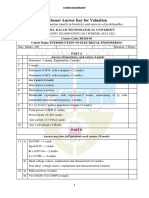

Implementation of Error Detection Mechanism Using NetSim

Uploaded by

editorijsaaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Implementation of Error Detection Mechanism Using NetSim

Uploaded by

editorijsaaCopyright:

Available Formats

IS J AA

RAKESH S, 2SOWMYA M N, 3Dr.M.SIDDAPPA M.Tech, 2nd year, CS&E dept., SSIT, Tumkur (D), Karnataka (S), India 2 Lecturer of CS&E dept, SSIT, Tumkur (D), Karnataka (S), India 3 Professor & HOD of CS&E dept,, SSIT, Tumkur (D), Karnataka (S), India rakeshs.snb@gmail.com1, sowmyamn22@rediffmail.com2, siddappa.p@gmail.com3

1 1

International Journal of Systems , Algorithms & Applications

Implementation of Error Detection Mechanism using NetSim

Abstract-- Network Simulation is a comprehensive tool for studying computer networks. NetSim features state of the art network simulation technology, and comes with additional offerings that enhance and quicken learning. NetSim is an educational network simulator and provides educators with a comprehensive and effective means of teaching computer networks. The software provides for network simulation across various protocols like Ethernet, Wireless LAN. TCP / IP, ATM and devices like routers, ATM switches. Apart from simulation NetSim also features C / C++ /JAVA programming exercises, animated basics and real time packet capture. NetSim provides network performance metrics at various abstraction level such as Network, sub-network, Node and a detailed packet trace. NetSim features a Development environment with a source code editor and a compiler. Model libraries with source code are provided for user modification. Importantly, options are not limited to the listing as it is possible to develop any type of protocol or device model with NetSims protocol editing facilities. Error detection [2] is a technique that enables reliable delivery of digital data over unreliable communication channels. Many communication channels are subject to channel noise, and thus errors may be introduced during transmission from the source to a receiver. Error detection techniques allow detecting such errors, while error correction enables reconstruction of the original data. Error detection is the detection of errors caused by noise or other impairments during transmission from the transmitter to the receiver. Key words: AWT: Abstract Window Toolkit, CRC: Cyclic Redundancy Check, LRC: Longitudinal Redundancy Check, NetSim: Network Simulation

B. Java Swing class hierarchy Swing, which is an extension library to the AWT, includes new and improved components that enhance the look and functionality of GUIs. Swing can be used to build Standalone swing GUI Apps as well as Servlets and Applets. It employs model/view design architecture. Swing being 100% Java code makes it more portable and more flexible than AWT. Swing is built on top of AWT. Swing is written entirely in Java, using AWT's lightweight component support. In particular, unlike AWT, the architecture of Swing components makes it easy to customize both their appearance and behavior. Components from AWT and Swing can be mixed, allowing you to add Swing support to existing AWT-based programs. For example, swing components such as JSlider, JButton and JCheckbox could be used in the same program with standard AWT labels, text fields and scrollbars. You could subclass the existing Swing UI, model, or change listener classes without having to reinvent the entire implementation. Swing also has the ability to replace these objects on the fly. The class JComponent, descended directly from Container, is the root class for most of. Swing components i.e. used to build a GUI. The list below shows some of the commonly used Swing components that are used in Java swing programs. To learn and understand these swing programs, AWT programming knowledge is not required. LRC [6] is a form of redundancy check that is applied independently to each of a parallel group of bit streams. The data must be divided into transmission blocks, to which the additional check data is added. CRC [1] [6] is a single-burst-error-detecting cyclic cod and non-secure hash function designed to detect accidental changes to digital data in computer networks. It is characterized by specification of a so-called generator polynomial [4], which is used as the divisor in a polynomial long division over a finite field, taking the input data as the dividend, and where the remainder becomes the result. II. PROCEDURE A. Steps for doing LRC:

I. INTRODUCTION A. Network Simulation NetSim is Network simulation software which takes in user inputs and provides output metrics. NetSim is a popular tool developed by TETCOS, in association with Indian Institute of Science, Bangalore. NetSim has also been featured with Computer Networks and Internets V edition by Dr. Douglas Comer, published by Prentice Hall. NetSim provides network performance metrics at various abstraction levels such as Network, sub-network, Node and a detailed packet trace. NetSim features a Development environment with a source code editor and a compiler. Model libraries with source code are provided for user modification. Importantly, options are not limited to the listing as it is possible to develop any type of protocol or device model with NetSims protocol editing facilities.

Volume 2, Issue ICTM 2011, February 2012, ISSN Online: 2277-2677 ICTM 2011|June 8-9,2011|Hyderabad|India

22

IMPLEMENTATION OF ERROR DETECTION MECHANISM USING NETSIM

IS J AA

International Journal of Systems , Algorithms & Applications

A block of bits is organized in a table (rows and columns). For example instead of sending 32 bits, we organize them in a table made of 4 rows and 8 columns. We then calculate the Parity bit for each column and create a new row of 8 bits which are the parity bit for the whole block. Note that the first parity bit in the 5th row is calculated based on all the first bits. The second parity bit is calculated based on all the second bits and so on.. We then attach the 8 parity bit to the original dat and send them to the receiver.

Calculate the parity bits of each of the 8 columns and create a new row of 8 bits, which will have the parity bits for the whole block [3]. The first parity bit values of the first column, second parity bit value based on second column values and so on.. After calculation of the 8 parity values it is attached to the original data and sends across to the receiver.

B. Steps for doing CRC: Steps performed by Sender: Get the raw frame. Left shift the raw frame by n bits and divide it by divisor. The remainder is the CRC bit. Append the CRC bit to the frame and transmit. Steps performed by Receiver: Receive the frame. Divide it by divisor. Check the reminder. III. MPLEMENTATION A. Concept of LRC: LRC is used for detecting the error in the transmitted data bits. The term Redundancy here means the extra information appended to the transmitted data bits. This is mainly appended at the end of each data frame transmitted. These redundancy bits are used to check the accuracy of the received data frame [6]. The input data is converted to Bit Format and the bits are divided into columns of 8 bits and rows are required (a data frame of 32-bits is converted into a table of 8 columns and 4 rows).

B. Front end design of LRC: For designing the front end of the LRC we use JPanel. We use JLabel component for creating the labels like Mode, Parity, Input, Data, Action, Help, Sample, User, Odd, Even, Data, Max. 8 characters, Original, Error and Concept, Algorithm, Flowchart. In Mode section JRadioButton component is used for selecting Sample mode or User mode and for selecting Odd or Even in Parity section. In Input section JTextField component is used to enter the digits and it is fixed to 8 characters and in Data section it is used to display original data and if any error occur during running it is also displayed. In Action section JButton component is used for selecting RUN or REFRESH action. In Help section a hyper link is creating, when click on this link it will display the information like Concept, Algorithm and Flowchart of the CRC. C. Concept of CRC: CRC is a type of function that takes as input a data stream of any length and produces an output [7]. Bit strings are treated as representation of polynomial with co-efficient of 0 and 1. The sender and receiver must agree upon the Generator polynomial in advance. The size of data must be greater than the size of the Generator polynomial to compute the checksum [7]. The computed checksum is appended to the transmitting frame. If the receiver gets the frame it tries dividing it by generator polynomial. If there is a remainder there has been a transmission error else no error [8]. The Generator polynomial for CRC-12 is given below, X12+X11+X3+X2+X1+1, the binary equivalent of CRC-12 is 1100000001111. D. Front end design of CRC: For designing the front end of the CRC we use JPanel. We use JLabel component for creating the labels like Mode, Algorithm, Condition, Input, Action, Help, Output, Sample, User, CRC-12, CRC-16, CRC-32, CRC-CCITT, Select the file, Text file(.txt), Max. 5000 bytes and Concept, Algorithm, Flowchart.

23

(Note: The front end design of LRC is changed due to space)

Volume 2, Issue ICTM 2011, February 2012, ISSN Online: 2277-2677 ICTM 2011|June 8-9,2011|Hyderabad|India

IMPLEMENTATION OF ERROR DETECTION MECHANISM USING NETSIM

IS J AA

International Journal of Systems , Algorithms & Applications

In Mode section JRadioButton component is used for selecting Sample mode or User mode and for selecting CRC-12, CRC-16, CRC-31 and CRCCCITT mode in Algorithm section and for selecting No Error and Error mode in Condition section. In Input section JTextField component is used for selecting input file. In Input section JButton component is used for browsing the input file in the system and in Action section for selecting RUN or REFRESH action. In Help section an Hyper link is create, when click on this link it will display the information like Concept, Algorithm and Flowchart of the CRC.

B. Pseudo code of CRC: Convert the data into binary format. If it is sender side append 12 0s with the binary data else add original CRC with the binary data. If the MSB is 0 then XOR binary data with the string 000000000000 else XOR with the string 1100000001111. Find the HEXA decimal format of the XOR results. If it is 0 both sender and receiver matches then there are no error else there is an error. V. CONCLUSION This paper gives the details about error detection mechanisms such as LRC and CRC and how these mechanisms can work on NetSim using front end designs of LRC and CRC. VI. ACKNOWLEDGMENT I am very thank full to my HOD Dr. M. Siddappa, SSIT, and my internal guide Sowmya M N, SSIT and also my external guide Mahendran, TETCOS, Bengaluru, for their guidance in my project work and also their guidance for preparing this paper.

REFERENCE [1]. Ritter, Terry. "The Great CRC Mystery. Dr. Dobb's Journal 11 ( 2 ):2 6 3 4 ,7 6 8 3 .h t tp : // ww w. c i p h e r sb yr i t t er . co m/ AR T S / CRCMYST.HTM. Retrieved 21 May 2009. [2]. Peterson, W. W. and Brown, D. T.. "Cyclic Codes for Error Detection". Proceedings of the IRE 49: 228. [3]. N. Cam-Winget, Nancy; R. Housley, Russ; D. Wagner, David; J. Walker, Jesse (May 2003). "Security Flaws in 802.11 Data Link Protocols". Communications of the ACM 46 (5): 3539. [4]. Stigge, Martin; Pltz, Henryk; Mller, Wolf; Redlich, Jens-Peter (May 2006). Reversing CRC Theory and Practic. Berlin: Humboldt University Berlin. pp. 24. http://sar.informatik.hu-berlin.de/research/ publications/SAR-PR-2006-05/SAR-PR-2006-05_.pdf. Retrieved 21 July 2009. [5]. Anachriz (30 April 1999). "CRC and LRC how to Reverse it. http://www.woodmann.com/fravia/crctut1.htm. Retrieved 21 January 2010. [6]. Williams, Ross N. (24 September 1996). "A Painless Guide to LRC and CRC Error Detection Algorithms V3.00. http:// www.repairfaq.org/filipg/LINK/F_crc_v3.html. Retrieved 5 June 2010. [7]. Koopman, Philip; Chakravarty, Tridib (2004). "Cyclic Redundancy Code (CRC) and Longitudinal Redundancy Code(LRC) Polynomial Selection For Embedded Networks".http://www.ece.cmu.edu/ ~koopman/roses/dsn04/koopman04_crc_poly_embedded.pdf. [8]. Greg Cook (26 March 2010). "Catalogue of parametrised LRC and CRC algorithms. http://regregex.bbcmicro.net/crc-catalogue.htm. Retrieved 5 June 2010.

(Note: The front end design of CRC is changed due to space)

IV. PSEUDO CODE A. Pseudo code of LRC: Read the content of the input file, i.e. the input data, type of parity and the error data from the Input.txt and store it in variable like the above method. After finding out the length of the data converted into bits form a table of 8 columns and depending on the data length the number of rows. If the passed flag (type of parity) is 2 then it is even parity else it is odd parity. Calculate the parity bit of each of the 8 columns and create a new row of 8 bits which with have parity bits for the whole block. The first parity bit of the first column is calculated based on all the first bit values of the first column, second parity bit value based on second column value and so on.. After the parity bit is formed, i.e. the last row has been formed which represents the parity bit of the original data and error data, they are written into the output file in each line.

Volume 2, Issue ICTM 2011, February 2012, ISSN Online: 2277-2677 ICTM 2011|June 8-9,2011|Hyderabad|India

24

You might also like

- A Comparative Study of AODV, DSR, and DYMO Routing Protocols Using OMNeTDocument5 pagesA Comparative Study of AODV, DSR, and DYMO Routing Protocols Using OMNeTEditor IJRITCCNo ratings yet

- A Study of Routing Protocols For Ad-Hoc NetworkDocument6 pagesA Study of Routing Protocols For Ad-Hoc NetworkeditorijaiemNo ratings yet

- OPNET Modeler - Introduction LTE SimulationDocument16 pagesOPNET Modeler - Introduction LTE SimulationAnonymous TTVlXoNo ratings yet

- Clustering Traffic FullDocument63 pagesClustering Traffic Fullprabhujaya97893No ratings yet

- JournalNX Lte NetworkDocument4 pagesJournalNX Lte NetworkJournalNX - a Multidisciplinary Peer Reviewed JournalNo ratings yet

- A Paper On Parallel CRC Generation For High Speed ApplicationDocument3 pagesA Paper On Parallel CRC Generation For High Speed ApplicationPidikiti Surendra BabuNo ratings yet

- Applying Regression Models To Calculate The Q FactorDocument9 pagesApplying Regression Models To Calculate The Q FactorSuriza A ZabidiNo ratings yet

- Routing Information Protocol Using OPNET: IjitkmDocument7 pagesRouting Information Protocol Using OPNET: IjitkmIrving Zuñiga RiveraNo ratings yet

- OA Notes 1Document34 pagesOA Notes 1richie053No ratings yet

- Context Likelihood of RelatednessDocument10 pagesContext Likelihood of Relatedness143davbecNo ratings yet

- Comparative Analysis of Performance of Hub With Switch Local Area Network (LAN) Using Riverbed in University of Technology (Utech), JamaicaDocument23 pagesComparative Analysis of Performance of Hub With Switch Local Area Network (LAN) Using Riverbed in University of Technology (Utech), JamaicaOla Yemi UthmanNo ratings yet

- Final Computer Network Lab Mannual (18ECL76)Document99 pagesFinal Computer Network Lab Mannual (18ECL76)Ankushh RNo ratings yet

- Monitoring and Protocol Analysis Tool For LANDocument11 pagesMonitoring and Protocol Analysis Tool For LANshaikhdanish247No ratings yet

- MT6603 DMS Unt 3 PDFDocument39 pagesMT6603 DMS Unt 3 PDFKarthi KeyanNo ratings yet

- 03 PresentationDocument38 pages03 Presentation18-QADEER AHMADNo ratings yet

- Sns College of Technology: Computer NetworksDocument27 pagesSns College of Technology: Computer NetworksgmsamyNo ratings yet

- MPEG-4 Performance Analysis For A CDMA Network-on-Chip: Manho Kim, Daewook Kim and Gerald E. SobelmanDocument4 pagesMPEG-4 Performance Analysis For A CDMA Network-on-Chip: Manho Kim, Daewook Kim and Gerald E. SobelmanraghavaNo ratings yet

- Presented By:: Esha Aslam (19-CS-02) Nosheen Rasheed (19-CS-05) Qadeer Ahmad (19-CS-18) Rehman Yasin (19-CS-35)Document34 pagesPresented By:: Esha Aslam (19-CS-02) Nosheen Rasheed (19-CS-05) Qadeer Ahmad (19-CS-18) Rehman Yasin (19-CS-35)18-QADEER AHMADNo ratings yet

- Part-A (University Questions) : Sengunthar College of Engineering, TiruchengideDocument31 pagesPart-A (University Questions) : Sengunthar College of Engineering, TiruchengideAlwarsamy RamakrishnanNo ratings yet

- Matlab Project FileDocument27 pagesMatlab Project FileHimanshu ShisodiaNo ratings yet

- Network Monitoring SystemDocument25 pagesNetwork Monitoring SystemSudhir BarwalNo ratings yet

- Abstract On Socket ProgrammingDocument33 pagesAbstract On Socket Programmingyogesh_yadav2012100% (2)

- Vertical Handoff Decision Scheme Within Heterogeneous Mobile Communication NetworksDocument5 pagesVertical Handoff Decision Scheme Within Heterogeneous Mobile Communication NetworksNuttakorn JumpawanNo ratings yet

- Assignment: Application of Graphs in Computer ProgrammingDocument11 pagesAssignment: Application of Graphs in Computer ProgrammingSaran AgarwalNo ratings yet

- Report PDFDocument11 pagesReport PDFshahNo ratings yet

- Serial Port Complete: COM Ports, USB Virtual COM Ports, and Ports for Embedded SystemsFrom EverandSerial Port Complete: COM Ports, USB Virtual COM Ports, and Ports for Embedded SystemsRating: 3.5 out of 5 stars3.5/5 (9)

- IntroductionDocument2 pagesIntroductionAkhil KumarNo ratings yet

- OPNET Modeler and Ns-2: Comparing The Accuracy of Network Simulators For Packet-Level Analysis Using A Network TestbedDocument8 pagesOPNET Modeler and Ns-2: Comparing The Accuracy of Network Simulators For Packet-Level Analysis Using A Network TestbedKamran MaqboolNo ratings yet

- Design of 8-Bit Dedicated Microprocessor For Content Matching in NIDPSDocument7 pagesDesign of 8-Bit Dedicated Microprocessor For Content Matching in NIDPSgiangNo ratings yet

- GRID NETWORKING (WWW - Ebookmaterials.blogspot - Com)Document15 pagesGRID NETWORKING (WWW - Ebookmaterials.blogspot - Com)VeerubglrKumarNo ratings yet

- Assignment 1Document5 pagesAssignment 1Parker Bollinger IIINo ratings yet

- Network ManagementDocument39 pagesNetwork ManagementDhanraj DSNo ratings yet

- A) (I) A Distributed Computer System Consists of Multiple Software Components That Are OnDocument14 pagesA) (I) A Distributed Computer System Consists of Multiple Software Components That Are OnRoebarNo ratings yet

- Programming Concepts and Embedded Programming in C and C++Document55 pagesProgramming Concepts and Embedded Programming in C and C++prejeeshkpNo ratings yet

- Snug04 Bromley Smith PaperDocument16 pagesSnug04 Bromley Smith PaperDheeraj SinglaNo ratings yet

- Module 2Document19 pagesModule 2yogeshwarkolarNo ratings yet

- Coupler Curve System PDFDocument11 pagesCoupler Curve System PDFshahNo ratings yet

- FIR FilterDocument5 pagesFIR FilterManasa UpadhyayaNo ratings yet

- Acquired Experiences With Computational Tool MS SV Used in Electronic Circuit DesignDocument12 pagesAcquired Experiences With Computational Tool MS SV Used in Electronic Circuit DesignKhadar BashaNo ratings yet

- NetworkDocument156 pagesNetworkavi0341No ratings yet

- The Art of Assembly Language Programming Using PIC® Technology: Core FundamentalsFrom EverandThe Art of Assembly Language Programming Using PIC® Technology: Core FundamentalsNo ratings yet

- CS6551 Computer Networks Two Mark With AnswerDocument35 pagesCS6551 Computer Networks Two Mark With AnswerPRIYA RAJI100% (7)

- Mimo and OFDM in Wireless CommunicationDocument5 pagesMimo and OFDM in Wireless CommunicationEditor IJRITCCNo ratings yet

- Department of Computer Science and Engineering: 2. What Is Network Software?Document44 pagesDepartment of Computer Science and Engineering: 2. What Is Network Software?anish.t.pNo ratings yet

- Vlsi Unit-VDocument41 pagesVlsi Unit-VJay SubbareddyNo ratings yet

- IOT-Assignment 2 PDFDocument5 pagesIOT-Assignment 2 PDFQusai KHNo ratings yet

- Design Flow OverviewDocument9 pagesDesign Flow OverviewJubin JainNo ratings yet

- Tarafic Based Load Balncing in SDNDocument6 pagesTarafic Based Load Balncing in SDNatalelNo ratings yet

- Ieee 5 2020Document6 pagesIeee 5 2020Lakshmi SairaghavaNo ratings yet

- ERTS Unit 3Document38 pagesERTS Unit 3mohanadevi chandrasekarNo ratings yet

- Troubleshooting Approaches and Routing ProtocolsDocument6 pagesTroubleshooting Approaches and Routing ProtocolsHussein Al-wahaibiNo ratings yet

- CN Manual Lab (R20)Document85 pagesCN Manual Lab (R20)4416 LikhithaNo ratings yet

- Network Simulation Using OPNETDocument16 pagesNetwork Simulation Using OPNETTema HassanNo ratings yet

- Experiment - 1: Aim: A Brief Introduction To Network Simulation Through The Netsim Simulation PackageDocument3 pagesExperiment - 1: Aim: A Brief Introduction To Network Simulation Through The Netsim Simulation PackageYash GuptaNo ratings yet

- Lablist of CCNDocument8 pagesLablist of CCNBHAVIKA JAINNo ratings yet

- Computer Networks Lab Manual: V SemesterDocument53 pagesComputer Networks Lab Manual: V SemesterGanesanDhandapaniNo ratings yet

- Design of A High Speed Serializer, Timing Analysis and Optimization in TSMC 28nm Process TechnologyDocument6 pagesDesign of A High Speed Serializer, Timing Analysis and Optimization in TSMC 28nm Process TechnologyEditor IJRITCCNo ratings yet

- Assessment System: Take Assessment - EWAN Chapter 8 - CCNA Exploration: Accessing The WAN (Version 4.0)Document9 pagesAssessment System: Take Assessment - EWAN Chapter 8 - CCNA Exploration: Accessing The WAN (Version 4.0)asceric4363No ratings yet

- Distributed Traffic Management Framework by Network Parameters PDFDocument5 pagesDistributed Traffic Management Framework by Network Parameters PDFijosatNo ratings yet

- Shape Reconstruction by Producing New PointsDocument4 pagesShape Reconstruction by Producing New PointseditorijsaaNo ratings yet

- Marine ReconnoiterDocument9 pagesMarine ReconnoitereditorijsaaNo ratings yet

- Vedic Algorithms To Develop Green Chips For FutureDocument3 pagesVedic Algorithms To Develop Green Chips For FutureeditorijsaaNo ratings yet

- Multimedia Data Transmission Over Wireless Networks by Exploiting The QoS ParametersDocument4 pagesMultimedia Data Transmission Over Wireless Networks by Exploiting The QoS ParameterseditorijsaaNo ratings yet

- Improvement of Transient Stability of Two Machine System Using Static VAR Compensator and Power System StabilizerDocument4 pagesImprovement of Transient Stability of Two Machine System Using Static VAR Compensator and Power System StabilizereditorijsaaNo ratings yet

- Fuzzy-Logic Based Target Classification Using DroolsDocument4 pagesFuzzy-Logic Based Target Classification Using Droolseditorijsaa100% (1)

- Radio Frequency Identification - An Enabler of Supply Chain Operations in Retail SectorDocument5 pagesRadio Frequency Identification - An Enabler of Supply Chain Operations in Retail SectoreditorijsaaNo ratings yet

- Microstructure Analysis of Effect of Welding Heat On Mild Steel The Effect of Welding Heat Due To Fourth Pass On The Plates Are Disused in Terms of MicrostructureDocument4 pagesMicrostructure Analysis of Effect of Welding Heat On Mild Steel The Effect of Welding Heat Due To Fourth Pass On The Plates Are Disused in Terms of MicrostructureeditorijsaaNo ratings yet

- Skeletal Bone Age Assessment From Elbow RadiographsDocument4 pagesSkeletal Bone Age Assessment From Elbow RadiographseditorijsaaNo ratings yet

- Implementation of Conceptual Cohesion of Classes To Predict Faults in Object Oriented SystemsDocument5 pagesImplementation of Conceptual Cohesion of Classes To Predict Faults in Object Oriented SystemseditorijsaaNo ratings yet

- Alias Free Subband Adaptive Filtering - A New ApproachDocument5 pagesAlias Free Subband Adaptive Filtering - A New ApproacheditorijsaaNo ratings yet

- Development of Design Environment For Embedded SoC ApplicationDocument5 pagesDevelopment of Design Environment For Embedded SoC ApplicationeditorijsaaNo ratings yet

- Performance Evaluation of Adaptive Filter Algorithms For EOG Signal ProcessingDocument5 pagesPerformance Evaluation of Adaptive Filter Algorithms For EOG Signal ProcessingeditorijsaaNo ratings yet

- Education Through Satellite Boom For Health Care SectorDocument5 pagesEducation Through Satellite Boom For Health Care SectoreditorijsaaNo ratings yet

- Multi-Gigabit Pattern Matching For Packet Assesment in Network SecurityDocument6 pagesMulti-Gigabit Pattern Matching For Packet Assesment in Network SecurityeditorijsaaNo ratings yet

- Smart Client For Smart Grid NetworkDocument3 pagesSmart Client For Smart Grid NetworkeditorijsaaNo ratings yet

- Performance Assessment of Feature Based Image Retrieval Using Neural NetworksDocument5 pagesPerformance Assessment of Feature Based Image Retrieval Using Neural NetworkseditorijsaaNo ratings yet

- Design of DDR3 SDRAM Controller For Achieving High Speed Read OperationDocument5 pagesDesign of DDR3 SDRAM Controller For Achieving High Speed Read OperationeditorijsaaNo ratings yet

- Design of Weighted Modulo 2n + 1 Adder Using Diminished-1 Adder With The Correction CircuitsDocument5 pagesDesign of Weighted Modulo 2n + 1 Adder Using Diminished-1 Adder With The Correction CircuitseditorijsaaNo ratings yet

- Permission Management System For Secure CloudsDocument3 pagesPermission Management System For Secure CloudseditorijsaaNo ratings yet

- Performance Evaluation of The CMOS Full Adders in TDK 90 NM TechnologyDocument5 pagesPerformance Evaluation of The CMOS Full Adders in TDK 90 NM TechnologyeditorijsaaNo ratings yet

- Extend Authentication Using Sensor TechniqueDocument4 pagesExtend Authentication Using Sensor TechniqueeditorijsaaNo ratings yet

- Analysis and Design of Non-Linear Power System For Implementing Class of Pid ControllerDocument4 pagesAnalysis and Design of Non-Linear Power System For Implementing Class of Pid ControllereditorijsaaNo ratings yet

- Fuzzy Genetic Data Mining Using K-Means ClusteringDocument7 pagesFuzzy Genetic Data Mining Using K-Means ClusteringeditorijsaaNo ratings yet

- Image Processing For Object Tracking Using Vertex - FpgaDocument4 pagesImage Processing For Object Tracking Using Vertex - FpgaeditorijsaaNo ratings yet

- Analysis of 16-Bit and 32-Bit RISC ProcessorsDocument7 pagesAnalysis of 16-Bit and 32-Bit RISC ProcessorsTestauNo ratings yet

- Seeeduino XIAO in Action Minitype Wearable Projects Step by StepDocument132 pagesSeeeduino XIAO in Action Minitype Wearable Projects Step by StepmagiciancNo ratings yet

- Y50031 DeviceNetInterfaceSpecificationDocument75 pagesY50031 DeviceNetInterfaceSpecificationJaime Arreola100% (1)

- ViBE EM1000-2000Document2 pagesViBE EM1000-2000RobertNo ratings yet

- Datasheet A HV 3U Battery BOS G V1.4Document4 pagesDatasheet A HV 3U Battery BOS G V1.4Alaa ENo ratings yet

- Scheme/ Answer Key For Valuation: Scheme of Evaluation (Marks in Brackets) and Answers of Problems/keyDocument3 pagesScheme/ Answer Key For Valuation: Scheme of Evaluation (Marks in Brackets) and Answers of Problems/keyNigil ThomasNo ratings yet

- Catalogo Completo1Document14 pagesCatalogo Completo1Maicol Lopez HidalgoNo ratings yet

- Onbase Guide Handbook Certified Admins Expectations and TipspdfDocument54 pagesOnbase Guide Handbook Certified Admins Expectations and TipspdfAlberto José Segrera FernándezNo ratings yet

- JAVA UNIT-3 Lecture NotesDocument31 pagesJAVA UNIT-3 Lecture NotesSai NikhilNo ratings yet

- AIQ Core Quickguide (ENG)Document2 pagesAIQ Core Quickguide (ENG)royNo ratings yet

- Controlling A Smart Traffic Light Using Programmable Logic Controller (PLC)Document67 pagesControlling A Smart Traffic Light Using Programmable Logic Controller (PLC)Trang NguyễnNo ratings yet

- Display Control Unit, DCU2: Engine Control, Monitoring and Diagnostics in One UnitDocument2 pagesDisplay Control Unit, DCU2: Engine Control, Monitoring and Diagnostics in One UnitEduardo TotocayoNo ratings yet

- Cse 423: Virtualization & Cloud Computing: by Mr. Ajay Kumar Badhan Assistant Professor M.Tech (CST), B.Tech (Cse)Document25 pagesCse 423: Virtualization & Cloud Computing: by Mr. Ajay Kumar Badhan Assistant Professor M.Tech (CST), B.Tech (Cse)Dhoni M.SNo ratings yet

- Why Upgrade 12-13-16Document23 pagesWhy Upgrade 12-13-16ArturoNo ratings yet

- C++ WorkshopDocument47 pagesC++ WorkshopSheeba DhuruvarajNo ratings yet

- Comandos para Nuevo NetworkerDocument4 pagesComandos para Nuevo NetworkererickNo ratings yet

- 2Document5 pages2ihavedreams2017No ratings yet

- Module 2Document42 pagesModule 2DhananjayaNo ratings yet

- ADAM 4541 ManualDocument4 pagesADAM 4541 ManualFelipe MonteiroNo ratings yet

- Block Diagram: X555LD Repair GuideDocument7 pagesBlock Diagram: X555LD Repair GuideGustavo GarciaNo ratings yet

- JAVA Development: OOP, Classes, Encapsulation, StaticDocument48 pagesJAVA Development: OOP, Classes, Encapsulation, StaticCosmin GrosuNo ratings yet

- GD Sbom TypesDocument4 pagesGD Sbom TypesSANTHOSH KUMAR VOOTNURINo ratings yet

- Java 7-15marks QuestionsDocument1 pageJava 7-15marks QuestionsSai KrishNo ratings yet

- Module - 4 Number System and CodesDocument20 pagesModule - 4 Number System and CodesAshok KumarNo ratings yet

- PDB Hex Manual 1Document3 pagesPDB Hex Manual 1Sandro SiagianNo ratings yet

- Unit2 - CPU SchedulingDocument84 pagesUnit2 - CPU Schedulingkaushik prajapatiNo ratings yet

- LG W1943SSDocument32 pagesLG W1943SSRuben RiveroNo ratings yet

- 004 - Chimdesa - Gedefa - CORBA Architecture and Primary Elements at DuDocument17 pages004 - Chimdesa - Gedefa - CORBA Architecture and Primary Elements at Duchimdesa infosaNo ratings yet

- Infineon Infineon TLE8080EM DS v01 02 enDocument38 pagesInfineon Infineon TLE8080EM DS v01 02 enYael AlcaNo ratings yet

- Building Big Data Pipelines With Apache Beam Use A Single Programming Model For Both Batch and Stream Data Processing (Jan Lukavsky)Document342 pagesBuilding Big Data Pipelines With Apache Beam Use A Single Programming Model For Both Batch and Stream Data Processing (Jan Lukavsky)Bryan RojasNo ratings yet