Professional Documents

Culture Documents

Tema 2

Uploaded by

JorgeCeferinoValdezOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Tema 2

Uploaded by

JorgeCeferinoValdezCopyright:

Available Formats

Universidad de Murcia

Facultad de Informtica

TTULO DE GRADO EN

INGENIERA INFORMTICA

Estructura y Tecnologa de Computadores

Tema 2: Sistemas Digitales - Circuitos Secuenciales

Apuntes

CURSO /

VERSIN 2.0

Departamento de Ingeniera y Tecnologa de Computadores

rea de Arquitectura y Tecnologa de Computadores

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

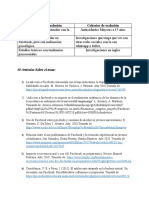

ndice general

2.1. Introduccin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2.2. Biestables (ip-ops) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2.2.1. Cerrojo tipo S-R . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2.2.2. Cerrojo tipo D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.2.3. Flip-op tipo D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2.2.4. Flip-op tipo S-R . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.2.5. Flip-op tipo J-K . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.2.6. Flip-op tipo T . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.3. Registros . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.4. Memorias SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.5. Memorias DRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.6. Diseo/sntesis de un circuito secuencial . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.6.1. Estructura general de un circuito secuencial . . . . . . . . . . . . . . . . . . . . . . . 15

2.6.2. Fases en el diseo/sntesis de un circuito secuencial . . . . . . . . . . . . . . . . . . . 16

2.6.3. Ejemplo de diseo/sntesis de un circuito secuencial . . . . . . . . . . . . . . . . . . 17

A2.Apndices 22

A2.1. Construccin fsica de una celda de memoria . . . . . . . . . . . . . . . . . . . . . . . . . . 22

B2. Boletines de prcticas 25

B2.1. Normas sobre la entrega de prcticas . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

B2.2. Implementacin de un Archivo/Banco de Registros con TkGate . . . . . . . . . . . . . . . . . 25

B2.2.1. Objetivos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

B2.2.2. Prerequisitos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

B2.2.3. Plan de trabajo . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

B2.2.4. Archivo/Banco de Registros . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

B2.2.5. Ejercicios . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

E2. Ejercicios 28

E2.1. Sistemas Digitales: Circuitos Secuenciales . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

E2.2. Solucin a ejercicios seleccionados . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

2.1. Introduccin

Todos los circuitos que vimos en el tema anterior se caracterizan porque la salida en cada instante depende

nica y exclusivamente de las entradas en ese mismo instante. En este sentido, se dice que los circuitos com-

binacionales carecen de memoria. Pero existe otro tipo de circuitos en los cuales nos interesa que, de alguna

manera, el circuito posea la capacidad de recordar su historia anterior, es decir, la secuencia de operaciones a

la que ha sido sometido

1

. El ejemplo ms tpico es la propia memoria de un computador: puede que queramos

almacenar un dato en una determinada posicin para poder recuperarlo en otro instante posterior. A este otro

tipo de circuitos, que poseen esta capacidad de recordar, se les denomina circuitos secuenciales. Estudiaremos

los ms importantes en este apartado, comenzando por los elementos de memoria ms sencillos, capaces de

almacenar un bit: los biestables, tambin conocidos como ip-ops.

1

En general, ninguno de los circuitos que veremos almacena literalmente la secuencia de operaciones a la que ha sido sometido.

Sin embargo, la informacin que almacenan es siempre consecuencia de dichas operaciones.

1

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

2.2. Biestables (ip-ops)

Antes de estudiar los biestables, estudiaremos previamente unos circuitos ms elementales, denominados

cerrojos, que sern utilizados como bloques bsicos en la construccin de aquellos. Comenzamos con los

cerrojos de tipo S-R.

2.2.1. Cerrojo tipo S-R

El primer circuito secuencial que estudiaremos es capaz de almacenar un bit, de manera que pueda ser

recordado con posterioridad, cuando dejen de estar activas las entradas que provocaron su escritura. La gura 1

muestra dicho circuito, al que se le llama cerrojo S-R (cerrojo Set-Reset), construido a partir de dos puertas

NOR cuyas salidas son realimentadas a las entradas.

R

Q

S

Q

(a)

Q

Q

S

R

(b)

Figura 1: Implementacin (a) y diagrama lgico (b) de un cerrojo S-R.

Las salidas Q y Q representan el valor del estado almacenado y su complemento. Cuando S y R estn a

0, las puertas NOR actan como inversores y almacenan los valores anteriores de Q y Q. Por ejemplo, si la

salida Q es 1, entonces el inversor inferior produce una salida 0, que es Q, y viceversa.

Veamos ahora cmo escribir en el cerrojo: si S vale 1 la salida Q es 0 y Q es 1 (Set). Si R es 1 la salida Q

es 0 y Q es 1 (Reset). Cuando S y R toman el valor 1 simultneamente, la situacin del circuito es inestable y

las salidas oscilan. Esta ltima situacin, pues, debe evitarse puesto que no est controlada.

La tabla de excitacin 1 resume el funcionamiento lgico del cerrojo S-R (Q

indica el valor del estado

siguiente, frente al estado actual Q).

Entradas de Estado Estado

excitacin actual siguiente

S R Q Q

0 0 0 0

0 0 1 1 No cambia

0 1 0 0

0 1 1 0 Puesta a cero

1 0 0 1

1 0 1 1 Puesta a uno

1 1 0 X

1 1 1 X No permitido

Tabla 1: Tabla de excitacin del cerrojo S-R.

La tabla de excitacin es simplemente la tabla de estados del cerrojo y muestra las transiciones de estado

para cada combinacin de entradas de excitacin. Las columnas S y R son las entradas aplicadas al cerrojo.

La columna rotulada Q es el estado del cerrojo S-R antes de aplicar una combinacin de entradas a S y R.

La columna rotulada como Q

es el estado del cerrojo despus de aplicar las entradas al cerrojo. Por tanto, la

columna Q es el estado actual y la columna Q

es el estado siguiente. Esta tabla puede expresarse tambin

2

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

mediante una ecuacin lgica, denominada ecuacin caracterstica del cerrojo S-R:

Q

= S +R Q

que se obtiene simplicando la salida Q

en funcin de las entradas S, R y Q.

Resulta interesante ver cmo es posible incluir una seal de control C, que determinar en qu momentos

el cerrojo har caso de sus entradas. Para ello basta emplear dos puertas AND, como se muestra en la gura 2.

Slo cuando la seal de control C est a 1, ser posible cambiar el estado del cerrojo mediante S y R.

Q

Q

C

R

S

Figura 2: Cerrojo S-R con seal de control.

2.2.2. Cerrojo tipo D

Pasamos ahora a modicar el cerrojo S-R para hacer ms sencillo el almacenamiento de los datos. Ne-

cesitamos un dispositivo que transera un valor lgico de su entrada de excitacin, que denominaremos D, a

la celda de almacenamiento con acoplamiento cruzado de un cerrojo. La gura 3 muestra el diagrama de un

cerrojo D. Un cerrojo D almacena el valor de la seal de la entrada de datos en la memoria interna y posee dos

entradas y dos salidas. Las entradas son: el valor de datos que se va a almacenar, denominado D, y una seal

de control, llamada C, que determina en qu momento el cerrojo debe almacenar el valor de la entrada D en

la estructura acoplada. Cuando C vale 1 el cerrojo est abierto y el valor de salida Q se convierte en el valor

de entrada D. Cuando C vale 0, el cerrojo est cerrado y el valor de salida Q es el valor que fue almacenado la

ltima vez que se abri el cerrojo.

Figura 3: Cerrojo D, controlado por la seal C.

Cuando tratamos con circuitos secuenciales, puesto que su comportamiento depende de su evolucin en el

tiempo, es til representar de algn modo esta evolucin temporal. Para ello se emplean los cronogramas, que

no son ms que diagramas donde, en el eje horizontal se representa el tiempo, mientras que en el eje vertical

se muestra el valor lgico de determinadas seales (y que, por tanto, pueden tomar los valores cero o uno).

En el siguiente cronograma, por ejemplo, se muestra el funcionamiento de un cerrojo D si suponemos que la

salida inicialmente tiene el valor cero. Obsrvese cmo el estado almacenado, Q, toma el valor de la entrada D

(justo tras un pequeo retardo) en el momento en que la seal C vale 1. Slo si C vale 1 el cerrojo es sensible

a dicha entrada D. A menudo, no obstante, en la representacin temporal de las seales se desprecia el valor

de dichos retardos, y se muestran los cambios de modo instantneo en el valor de las mismas.

3

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Figura 4: Operacin de un cerrojo D suponiendo que la salida est inicialmente a 0.

Entrada de Entrada de Estado

control excitacin siguiente

C D Q

0 X Q Retencin

1 0 0 Almacenar 0

1 1 1 Almacenar 1

Tabla 2: Tabla de excitacin del cerrojo D.

En la tabla 2 se observa la tabla de excitacin del cerrojo D en forma resumida que da lugar a la ecuacin

caracterstica:

Q

= D C +C Q

2.2.3. Flip-op tipo D

El cerrojo de la gura 3 es la base para otro elemento de memoria ligeramente ms complejo que tambin

nos permite almacenar datos y que llamaremos ip-op tipo D.

A diferencia del caso de los cerrojos, las seales de entrada que recibe un ip-op slo tienen efecto

durante un instante de tiempo, en lugar de a lo largo de un intervalo largo de tiempo como ocurra con la seal

C de los cerrojos.

Una seal peridica, denominada reloj, ser la encargada de determinar en qu momento concreto el

circuito ser sensible a su entrada y podr escribirse en l. La seal de reloj oscilar tomando peridicamente

valores alternando entre cero y uno. A cada cambio de esta seal se le denomina anco. Un anco se denomina

ascendente, positivo o de subida si el cambio es de 0 a 1; y descendente, negativo o de bajada en caso contrario.

Aunque, por simplicidad en los diagramas, suponemos que las transiciones de las seales de 0 a 1 o de 1

a 0 ocurren de forma instantnea y, por tanto, dibujamos lneas verticales para representarlas, esto no es as

en la realidad. En unos cronogramas ms precisos, las transiciones seran casi verticales (pero no del todo)

y transcurrira un corto periodo de tiempo desde que la seal comienza a cambiar hasta que se estabiliza en

su nuevo valor. Durante este corto tiempo, y slo entonces, es necesario que la seal cuyo valor se quiera

almacenar en el ip-op se mantenga estable.

El estado almacenado en el ip-op podr cambiarse slo durante uno de los dos ancos y se dir que el

ip-op es activo en anco descendente o en anco ascendente, dependiendo de en qu momento el circuito

es sensible a la entrada. El cronograma de la gura 5 ejemplica el comportamiento deseado para un ip-op

de tipo D activo en el anco ascendente. En este cronograma se supone que los retardos son despreciables.

Un modo sencillo de implementar la funcionalidad deseada es mediante la conexin en serie de dos cerro-

4

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Figura 5: Cronograma de operacin de un ip-op D disparado por anco de subida.

Figura 6: Flip-op D maestro-esclavo, y smbolo lgico correspondiente: (Superior) Sin seal adicional de

escritura. (Inferior) Despus de aadirle dicha seal.

5

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

jos. En la gura 6 (superior) podemos ver el esquema de un ip-op D maestro-esclavo disparado por anco

de bajada (que la activacin se produce por anco se expresa colocando un tringulo en la entrada C del bloque

lgico, y si adems incluimos un pequeo circulo estamos indicando que el anco activo es el descendente). El

primer cerrojo, llamado maestro, se abre y sigue a la entrada D cuando la entrada de reloj C vale 1. Cuando la

entrada de reloj C cae, el primer cerrojo se cierra, pero el segundo cerrojo, llamado esclavo, se abre y obtiene

su entrada de la salida del primer cerrojo maestro. Hacer el ip-op sensible al anco de subida, en lugar de

al de bajada sera trivial, cambiando el inversor para que afectase al cerrojo maestro, en lugar de al esclavo.

En la gura inferior se ha aadido, adems, una seal adicional de permiso de escritura (W), para poder

controlar que no se realice la escritura en todos los ancos activos de la seal de reloj, sino slo en aquellos en

los que nos interese (cuando la seal W valga 1). Esta seal, como veremos, ser de gran importancia cuando

construyamos el camino de dato de la CPU multiciclo en el tema 4.

La tabla de excitacin de un ip-op D (sin permiso de escritura) es similar a la de un cerrojo D, la

diferencia radica en la temporizacin. Mientras que en un cerrojo el estado cambia siempre que las entradas

adecuadas cambien y la seal de control tenga valor 1, en un ip-op el estado cambia nicamente en un anco

de reloj (ascendente o descendente), o sea, un ip-op est gobernado por una seal de reloj (ver tabla 3 para

el caso de un ip-op D disparado por anco descendente). La ecuacin caracterstica queda muy sencilla,

puesto que el estado simplemente se actualiza con el valor de la entrada D en el anco correspondiente:

Q

= D.

Entrada de Entrada de Estado

reloj excitacin siguiente

C D Q

1 0 0 0 Almacenar 0

1 0 1 1 Almacenar 1

Tabla 3: Tabla de excitacin del ip-op D disparado por anco descendente.

De modo anlogo se puede razonar para el caso de tener la entrada de activacin W. En ese caso, la tabla

quedara como se muestra en 4 y la ecuacin caracterstica sera: Q

= D W +Q W.

Entrada de Permiso de Entrada de Estado

reloj escritura excitacin siguiente

C W D Q

1 0 0 0 Q Retener estado

1 0 1 0 0 Almacenar 0

1 0 1 1 1 Almacenar 1

Tabla 4: Tabla de excitacin del ip-op D disparado por anco descendente con seal de permiso de escritura.

2.2.4. Flip-op tipo S-R

Los ip-op tipo D son los ms importantes, puesto que constituyen el mtodo ms cmodo para el alma-

cenamiento de datos en los computadores. En los apartados que siguen veremos cmo utilizarlos para construir

registros, cierto tipo de memorias, etc. Sin embargo, no son la nica alternativa. Pueden construirse tambin

otro tipo de ip-ops, con comportamientos ligeramente distintos, que pueden resultar tiles en algunos ca-

sos. El ip-op S-R, por ejemplo, puede construirse a partir de dos cerrojos S-R con una seal de control. Las

seales de activacin de los dos cerrojos son controladas por versiones complementarias de una seal de reloj.

Cuando la seal de reloj C es cero, el cerrojo maestro est abierto y el esclavo cerrado. El cerrojo maestro

procesa sus entradas S y R. Cuando la seal de reloj es uno ambos ip-ops intercambian sus papeles de

6

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

forma que el maestro est cerrado y el esclavo abierto. El esclavo est abierto, enviando la salida del cerrojo

maestro a la salida Q del ip-op, mientras que el cerrojo maestro permanece cerrado ignorando cualquier

cambio posterior en sus entradas. El ip-op S-R de la gura 7 se activa por anco ascendente y tiene como

ecuacin caracterstica: Q

= S +R Q, obtenida a partir de la tabla de excitacin 5

Figura 7: (Izquierda) Flip-op S-R. (Derecha) Smbolo lgico del ip-op S-R.

Entrada de Entradas de Estado

reloj excitacin siguiente

C S R Q

0 1 0 0 Q Retener estado

0 1 0 1 0 Puesta a 0

0 1 1 0 1 Puesta a 1

0 1 1 1 X No permitido

Tabla 5: Tabla de excitacin del ip-op S-R disparado por anco ascendente.

2.2.5. Flip-op tipo J-K

Figura 8: Smbolo lgico del ip-op J-K.

Otro tipo de ip-op es el ip-op J-K. Puede considerarse como una extensin de un ip-op S-R, a

cuyas entradas se asigna J = S y K = R. Sin embargo, mientras que en aquel la combinacin S = R = 1 no

est permitida, el ip-op J-K utiliza este caso particular para agregar un modo de operacin muy til. La

caracterstica adicional del dispositivo J-K es que su estado se alterna; es decir, cambia del 0 al 1 1 al 0

cuando J = K = 1. La ecuacin caracterstica de este ip-op es Q

= K Q + J Q, obtenida a partir de la

tabla de excitacin 6.

2.2.6. Flip-op tipo T

Por ltimo, el ip-op T se utiliza con frecuencia para la construccin de mdulos contadores. Tiene una

nica entrada de excitacin llamada T. La funcin de este dispositivo consiste en cambiar su estado cada vez

7

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Entrada de Entradas de Estado

reloj excitacin siguiente

C J K Q

1 0 0 0 Q Retener estado

1 0 0 1 0 Puesta a 0

1 0 1 0 1 Puesta a 1

1 0 1 1 Q Alternancia

Tabla 6: Tabla de excitacin del ip-op J-K disparado por anco descendente.

que as lo indique la seal de reloj. La tabla 7 resume el comportamiento de un ip-op T activado por anco

descendente cuya ecuacin caracterstica es: Q

= Q T +Q T

Figura 9: Smbolo lgico del ip-op T.

Entrada de Entrada de Estado

reloj excitacin siguiente

C T Q

1 0 0 Q Retener estado

1 0 1 Q Alternancia

Tabla 7: Tabla de excitacin del ip-op T disparado por anco descendente.

2.3. Registros

Puesto que los ip-ops de tipo D sirven para almacenar un bit, un modo sencillo de implementar un

registro que contenga un dato de varios bits, como un byte o una palabra, consiste simplemente en concatenar

varios ip-ops que comparten la misma seal de reloj y de permiso de escritura. La gura 10 muestra el

esquema y el diagrama lgico de un registro de n bits. Obsrvese que es completamente anlogo a un ip-op

sencillo (con una sola entrada de reloj y una sola entrada de permiso de escritura), slo que en este caso tanto

el dato ledo (D

out

) como el dato a escribir (D

in

) son seales de n bits de ancho:

2.4. Memorias SRAM

Los registros y archivos de registros (que se implementar como prctica de este tema), se utilizan como

bloques constructivos para memorias de pequeo tamao, donde la prioridad es obtener un tiempo de acceso

muy pequeo. Las memorias mayores, sin embargo, se construyen utilizando las llamadas SRAM (Static Ran-

dom Access Memory, memoria esttica de acceso aleatorio) y las DRAM (Dynamic Random Access Memory,

memoria dinmica de acceso aleatorio). En este apartado estudiaremos las particularidades de las primeras,

dejando las DRAM para el siguiente.

8

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Figura 10: Implementacin y diagrama lgico de un registro de n bits usando ip-ops tipo D.

Estructura de una memoria SRAM

Las memorias SRAM se presentan como circuitos integrados que son arrays de memoria (divididos en

posiciones, a cada una de las cuales le corresponde una direccin), su principal caracterstica principal es que

el tiempo de acceso es muy corto, por ello se emplean principalmente en el diseo de memorias cach.

Las SRAM tienen un tiempo de acceso jo para cualquier dato, aunque las caractersticas de acceso de

lectura y escritura pueden a veces variar. Un chip de SRAM tiene una conguracin especca en funcin

del nmero de posiciones direccionables, as como de la anchura del dato almacenable en cada posicin. La

gura 11 muestra el diagrama lgico de una SRAM de 32K posiciones de 8 bits cada una (32K8 = 32KB),

y por tanto necesita 15 lneas para ser direccionada (2

15

= 32768). Cada elemento tendr 8 bits, por lo tanto,

tendemos 8 lneas de entrada de datos y 8 lneas de salida de datos. Otras alternativas seran una SRAM de

256K x 1, con la misma capacidad, pero con diferente nmero de elementos (18 lneas de direccin) de 1 bit

(una lnea de entrada de datos y otra de salida); o bien, una SRAM de 16K x 16 (14 lneas de direccin, 16 de

entrada y 16 de salida). Dejaremos la explicacin de las lneas de seleccin de chip (chip select), habilitacin

de salida (output enable) y habilitacin de escritura (write enable) para ms adelante.

Figura 11: SRAM de 32K x 8 : 15 lneas de direccin, 8 lneas de entrada de datos, tres lneas de control y 8

lneas de salida de datos.

Al igual que en una memoria ROM, el nmero de posiciones direccionables se denomina altura y el

nmero de bits por unidad de memoria se llama anchura. Por diversas razones tcnicas, las SRAM ms

modernas y rpidas suelen estar disponibles en conguraciones delgadas, habitualmente 1 y 4 (1 y 4

bits de anchura, respectivamente).

Podramos pensar en construir una memoria SRAM de forma similar a un banco de registros, pero este

planteamiento presenta algunos inconvenientes. En un archivo de 32 registros, como el anteriormente visto,

necesitbamos dos multiplexores de 32 a 1, mientras que en una SRAM 32K x 8, usar un multiplexor de 32K

a 1 resulta totalmente impracticable. Para solucionar este primer inconveniente, las SRAM utilizan lneas de

salida compartidas, llamadas lneas de bits, que permiten que mltiples fuentes compartan una sola lnea de

9

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

datos. Para consentir que varias fuentes controlen una misma lnea se utiliza un buffer de tres estados (buffer

tri-estado).

Un buffer de tres estados es como una puerta lgica un tanto especial, con dos entradas (data y enable)

y una salida (out). Las entradas son la seal de datos y habilitacin de salida, respectivamente, y la salida

es igual a la seal de entrada si la lnea habilitacin de salida est activa; en otro caso, permanece en un

estado de alta impedancia, con lo que los otros buffers cuya seal de habilitacin de salida est activa, podr

usar la lnea compartida. La gura 12 muestra cuatro buffers de tres estados que comparten una nica lnea

de salida. Como vemos, esta estructura puede sustituir a un multiplexor de 4 a 1 (para ello, slo una de

las cuatro entradas de seleccin puede estar activa en un momento determinado, lo cual se consigue con un

decodicador). Esta implementacin es ms eciente (es mucho menos costosa en lo que se reere al nmero

de transistores necesarios) y, por tanto, ms escalable (es decir, aumentable a mayor nmero de entradas).

Figura 12: Cuatro buffers triestado para formar un multiplexor 4 a 1.

Estos buffers de tres estados pueden incorporarse a los ip-ops que forman las celdas bsicas de la

SRAM permitiendo as que aquellas celdas que corresponden a una misma salida compartan una sola lnea.

La gura 13 muestra una pequea SRAM de 4x2, donde cada cerrojo (obsrvese que en este caso se usan

cerrojos en lugar de ip-ops) tiene una lnea de habilitacin (Enable) que controla el buffer de tres estados

y, por tanto, el acceso a las lneas de salida. La seal de habilitacin de escritura, debidamente combinada con

las salidas del decodicador, decide si la palabra seleccionada es escrita con el dato colocado en las lneas de

entrada, D

in

.

Con este diseo hemos eliminado la necesidad de usar multiplexores; sin embargo, todava se requiere

la utilizacin de un gran decodicador a la entrada, para memorias con muchas posiciones direccionables.

Para eliminar este inconveniente, las grandes memorias se organizan como arrays rectangulares (bidimensio-

nales) y utilizan un proceso de decodicacin de dos pasos. La gura 14 muestra como podra conseguirse

tal disposicin construyendo una memoria SRAM 8x8 en base a 8 bloques 4x2 (descrito en la gura 13). El

primer decodicador genera la direccin para los 8 bloques de 4x2 a partir de los 2 bits ms signicativos de

la direccin. Despus un conjunto de multiplexores se utiliza para seleccionar un bit de cada conjunto de 2

bits a partir del bit menos signicativo de la direccin. Este diseo es ms eciente que una decodicacin de

un solo paso que necesitara un decodicador de 3 a 8 o un multiplexor de 8 a 1.

Veamos ahora cmo se realizan las lecturas y escrituras en las SRAM, para lo que tendremos que explicar

el uso de las dos lneas de control que an no hemos utilizado. La seal de seleccin de chip (Chip Select)

sirve para seleccionar si el chip se conecta o no a los buses de entrada (D

in

) y de salida (D

out

). En caso de

que valga 0, el chip queda completamente aislado de dichos buses y signica que no va a utilizarse en ese

momento, ni para leer ni para escribir. Este aislamiento se consigue tambin con buffers triestado controlados

por dicha seal. Esta lnea de seleccin tiene utilidad a la hora de construir memorias de mayor capacidad

utilizando varios bloques de menor tamao.

En el caso de las lecturas, debe estar a 1, adems de la lnea mencionada, la lnea de habilitacin de

salida (Output Enable). Esto resulta til cuando se conectan mltiples memorias a un solo bus de salida,

10

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Figura 13: SRAM de 4 x 2. Por simplicidad se omiten las entradas de habilitacin de salida y seleccin de

chip.

Figura 14: SRAM 8 x 8 como un array de 8 elementos de 4 x 2.

11

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

ya que permite determinar la memoria que controla el bus en cada momento. Para cada escritura, debemos

suministrar a la memoria el dato a escribir y la direccin, as como las seales que hacen que se efecte la

escritura. Cuando la seal de habilitacin de escritura (Write Enable) y la seal de seleccin de chip son

verdaderas, el dato en las lneas de entrada de datos se escribe en la celda determinada por la direccin.

2.5. Memorias DRAM

En una memoria SRAM, el valor que se almacena en cada celda se mantiene en el cerrojo correspondiente

de forma indenida mientras que haya alimentacin elctrica. El problema es que una celda para un solo

bit necesita bastantes transistores (unos seis, habitualmente). En los casos en los que se desea un alto nivel

de integracin y bajo consumo, aunque se penalice con velocidades de trabajo menores, se recurre a las

celdas dinmicas. Bsicamente, el diseo consiste en reducir el nmero de transistores que componen la

celda, consiguiendo las caractersticas citadas, obteniendo diferentes conguraciones a cada cual ms sencilla,

hasta llegar al mximo de simplicidad consistente en construir una celda con un nico transistor. Dado que

una DRAM usa un nico transistor por cada bit almacenado, son mucho ms baratas y densas por bit que

las SRAM. Sin embargo, este tipo de memorias presenta el inconveniente de que al estar la informacin

almacenada en un condensador, ste se va descargando internamente con el tiempo, de modo que debe ser

refrescada peridicamente (por este motivo se llama almacenamiento dinmico). Para refrescar la celda, se lee

su contenido y se vuelve a escribir. Este proceso de refresco se lleva a cabo normalmente a travs de la propia

circuitera del chip DRAM.

Estructura de una memoria DRAM

Las celdas de memoria se organizan en una matriz bidimensional con objeto de multiplexar las lneas de

seleccin de cada una de las dimensiones y ahorrar costes y espacio en la fabricacin de los diferentes chips

que componen un mdulo de memoria. Esto obliga al controlador de memoria a descomponer cada direccin

de acceso a una palabra de memoria en dos coordenadas, donde primero se selecciona la la de una celda en

la matriz y luego su columna. Dicho controlador de memoria proporciona las seales de control necesarias,

RAS (Row Address Strobe) y CAS (Column Address Strobe), que gobiernan la temporizacin. Por lo tanto,

las DRAM utilizan la misma idea de la decodicacin en dos niveles introducida en el apartado anterior.

En la gura 15 se muestra un chip de DRAM de 16 megabits, congurada como 2M x 8. Las celdas estn

organizadas en forma de matriz de 4K x 4K. Las 4096 celdas de cada la se dividen en 512 grupos de 8

celdas, de manera que una la puede memorizar 512 bytes de datos. Se requieren pues 12 bits de direccio-

nes para seleccionar una la. Otros 9 bits son necesarios para especicar el grupo de 8 bits dentro de la la

seleccionada. Por tanto, para acceder a un byte de esta memoria se necesitan 21 bits de direcciones. Los 12

bits ms signicativos, y los 9 bits de orden inferior, constituyen respectivamente las direcciones de la y de

columna de un byte. Durante una operacin de lectura o de escritura, se aplica en primer lugar la direccin de

la la. sta se carga en el cerrojo (latch) de direcciones de las como consecuencia de un pulso de seal en la

entrada de validacin de direccin de la RAS. Se inicia entonces una operacin de lectura en la que se leen

y refrescan todas las celdas de la la seleccionada. El contenido de las columnas de la la seleccionada pasa

a almacenarse en el conjunto de circuitos de deteccin/escritura. Inmediatamente despus de haber cargado

la direccin de la, se carga la direccin de columna en el cerrojo de direcciones de columnas bajo el control

de la seal de validacin de direccin de columnas CAS. La informacin de este cerrojo es decodicada para

seleccionar el grupo apropiado de 8 circuitos de deteccin/escritura. Si la seal de control R/W indica una

operacin de lectura, los valores de los circuitos seleccionados son transferidos a las lneas de datos, D

70

.

Para una operacin de escritura, la informacin de las lneas D

70

se transere a los circuitos seleccionados.

Esta informacin se utiliza para sobreescribir el contenido de las celdas seleccionadas. El esquema de direc-

cionamiento de dos niveles, junto con la circuitera interna necesaria, hace que los tiempos de acceso a las

DRAM sean mucho mayores que los tiempos de acceso de las SRAM.

12

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Figura 15: DRAM 2M x 8.

Debido a su alta densidad y coste reducido, las DRAM se usan ampliamente en las memorias de los

computadores. Para disponer de la suciente exibilidad al disear sistemas de memoria, se fabrican chips

con organizaciones diversas. Por ejemplo, un chip de 64 Mbits puede estar organizado como 16M x 4, 8M x

8 o 4M x 16.

A menudo es interesante que, para minimizar el nmero de patillas de un chip de memoria RAM, las lneas

de entrada y salida de datos estn compartidas. En ese caso, si el tamao de palabra utilizado en las memorias

es de n bits, el chip tendr n lneas de entrada/salida, Din/Dout

1..n

, en lugar de las n de entrada Din

1..n

,

y n de salida Dout

1..n

. Para poder hacer esto, es necesario que separemos las funciones de entrada y salida

de dichas lneas, para evitar su uso simultneo. Esto se consigue de nuevo a travs de buffers triestado, tal y

como se indica en la gura 16, controlados por una seal L/E, que determinar si se est usando la memoria

para leer o para escribir en ella. Si L/E=1, estaremos leyendo de la memoria, y en ese caso los buffers triestado

de la entrada dejarn aisladas de la salida a las seales Din

1..n

. Si L/E=0, entonces estaremos escribiendo, y

sern los buffers de la salida los que aislen a las seales Dout

1..n

.

Como hemos visto, un acceso a memoria supone un acceso de la seguido por un acceso de columna.

Primero se enva al chip la direccin de la y, a continuacin, la direccin de columna. Por ltimo, la memoria

pone en el bus de datos el elemento deseado. Por tanto, en un acceso a memoria se dedica ms tiempo a

localizar el dato que a transmitirlo.

Si leemos varios datos que estn consecutivos en memoria, slo es necesario especicar la direccin para

el primero de ellos, los dems nos vendrn dados por aadidura siempre que se encuentren en la misma la.

Supongamos que el ancho de nuestra memoria es de 64 bits, que cada la consta de 256 bits y que deseamos

leer 4 bloques de 64 bits cada uno (que supondremos que estn en la misma la). Basta con enviar a la memoria

la direccin del primer bloque para que se seleccione la la que lo contiene que, adems, incluye los otros tres

bloques que buscamos. De esta forma el acceso a los otros tres bloques ser ms rpido porque no necesitamos

proporcionar su direccin, y porque tampoco hace falta seleccionar ninguna la nueva. Esta forma de acceder

a la memoria se conoce como acceso en modo rfaga. Para especicar el nmero de ciclos empleados en

el acceso a memoria en un chip en modo rfaga, se utiliza la siguiente nomenclatura: x-y-y-y. El primer

13

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Figura 16: RAM con puerto compartido de lectura/escritura (bidireccional). Por simplicidad, se omiten las

seales de direccin, seleccin de chip, etc.

nmero, x, representa el nmero de ciclos de reloj necesarios para efectuar la primera lectura de un bloque

de 64 bits, mientras que el segundo nmero representa el nmero de ciclos necesarios para los tres accesos

subsiguientes. Un ejemplo sera 5-2-2-2, que signica 11 ciclos para leer una la completa (4 bloques de 64

bits), de los cuales 5 se emplean en el primer acceso y 2 en cada uno de los siguientes.

Cuando se accede a la DRAM de 2M x 8 de la gura 15, se detecta el contenido de las 4096 celdas de

la la seleccionada, pero slo se colocan 8 bits en las lneas de datos D7-0. Este byte es seleccionado por los

bits de la direccin de columna. Si aadimos un cerrojo a la salida del circuito detector de cada columna, de

manera que la aplicacin de una direccin de la haga que se carguen los cerrojos correspondientes a todos los

bits de la la seleccionada, entonces slo se requiere aplicar distintas direcciones de columna para transferir

los diferentes bytes a las lneas de datos.

Por ltimo, la memoria, como todos los circuitos vistos hasta ahora, es un dispositivo de almacenamiento

electrnico, y como tal es susceptible de cometer errores, devolviendo informacin diferente a la que fue

almacenada originalmente. La memoria DRAM, adems, almacena los bits en pequeos condensadores que

son refrescados continuamente para asegurar que la informacin no se pierde, y ello la hace ms propensa a

la posible generacin de errores eventuales.

Tradicionalmente, los mdulos de memoria han estado disponibles con y sin paridad. Los mdulos de

memoria sin paridad contienen exactamente un bit por cada bit de datos almacenado. Los mdulos de memoria

con paridad aaden un bit extra por cada 8 bits de datos almacenados que se utiliza para la deteccin y

correccin de errores. Este bit adicional puede usarse como bit de paridad, o bien, en un esquema de deteccin

y correccin de errores denominado Error Correction Code o ECC. La memoria ECC utiliza el algoritmo de

Hamming, que permite no slo detectar, sino tambin corregir errores en un bit dentro de bloques de 64 bits.

La memoria con paridad o ECC es ms cara y difcil de encontrar que la convencional, y adems ralentiza

ligeramente los accesos a memoria. Sin embargo, la utilizacin de algn tipo de mecanismo de deteccin de

errores aumenta la abilidad del sistema y facilita la localizacin de errores que con frecuencia son atribuidos

a la memoria. Por ello, es habitual su uso en ordenadores servidores cuya abilidad es crtica dentro de alguna

14

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

institucin (tales como bancos, grandes empresas, etc). Para saber si un mdulo de memoria dispone o no de

paridad, basta contar el nmero de chips que el mdulo posee. Si el nmero no es potencia de dos, entonces

se trata de un mdulo con paridad.

2.6. Diseo/sntesis de un circuito secuencial

En este apartado estudiaremos el diseo de un circuito secuencial genrico, es decir, aquel en el que la

salida en un instante dado no depende slo de las entradas en ese momento, sino tambin del estado en el que

se encuentra el circuito. ste, a su vez, depende de la historia de las entradas que hasta ese momento el sistema

ha recibido. Puesto que, como vemos, es necesario que estos circuitos posean una capacidad de memorizar su

estado, ser necesario que en su construccin empleemos cerrojos o ip-ops. Estos sern los encargados de

codicar el estado en el que se encuentra el circuito en cada momento.

2.6.1. Estructura general de un circuito secuencial

La gura 17 muestra la estructura general de un circuito secuencial. En l se observan sus componentes

ms importantes, que se detallan a continuacin:

Entrada: se trata de los n bits de entrada del circuito.

Salida: son los m bits de salida producidos por el circuito.

Estado actual: es la parte genuinamente secuencial del circuito, puesto que est encargada de codicar

el estado en el que se encuentra ste. Est compuesta por k circuitos elementales de memoria, cerrojos

o ip-ops, capaces de almacenar hasta 2

k

estados diferentes (puesto que cada uno puede almacenar un

0 o un 1).

Funcin de transicin: se trata de una funcin combinacional (en realidad es una multifuncin formada

k funciones elementales, puesto que tiene k bits de salida) que determina, a partir del estado y la entrada

actuales cul es el estado siguiente al que debe pasar el circuito. Es, por tanto, la parte encargada de

determinar la evolucin en el estado del mismo.

Funcin de salida: es otra funcin combinacional (otra multifuncin con m bits de salida), que depende

del estado del circuito (y quiz tambin de las entradas; en seguida volveremos sobre este punto), y que

determina la salida del circuito en cada instante.

Figura 17: Esquema lgico general de un circuito secuencial. Tambin se muestra la diferencia esencial entre

los circuitos de Moore y los de Mealy.

15

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

A la hora de hablar de circuitos secuenciales, suele hacerse una clasicacin en dos tipos principales,

segn el modo en que se calculan las salidas en funcin del estado y de las entradas. A estos dos tipos de

circuitos se les denomina, respectivamente, de Moore y de Mealy. En los circuitos de Moore, la salida en cada

instante puede computarse nica y exclusivamente a partir del estado del circuito, sin necesidad de tener en

cuenta las entradas. As, las entradas provocan los cambios de estado, y slo a travs de este cambio inuyen

en las salidas. En los de Mealy, por el contrario, en cada instante la salida depende simultneamente del

estado del circuito y del valor de las entradas. En la gura 17 se resume la diferencia entre ambos tipos de

circuitos: como puede observarse, slo en los circuitos de tipo Mealy la funcin de salida tambin depende de

las entradas.

Otra clasicacin de los circuitos secuenciales depender del tipo de cerrojos o ip-ops con los que se

implementen. Si se implementan con cerrojos (es decir, carecen de seal de reloj), entonces se denomina-

rn asncronos. Si, por el contrario, se implementan con ip-ops que comparten una misma seal de reloj,

entonces se denominarn sncronos.

2.6.2. Fases en el diseo/sntesis de un circuito secuencial

Por cuestiones temporales nos centraremos en el diseo de circuitos utilizando nicamente autmatas de

Moore que a la postre son iguales de potentes que los autmatas de Mealy, ya que para cualquier autmata

de Mealy existe un autmata de Moore equivalente (y viceversa). En general, cuando abordemos el diseo

de un sistema digital, lo haremos en una serie de pasos, que a continuacin resumimos y que posteriormente

aclararemos con un ejemplo:

1. Especicacin verbal: se trata de resumir con palabras el funcionamiento deseado para el circuito. Es

la especicacin previa de los requisitos que queremos que cumpla.

2. Especicacin del autmata: una vez especicado el comportamiento deseado verbalmente, tenemos

que formalizarlo. Para ello se utiliza un diagrama de estados especial, denominado autmata (en con-

creto, el denominado autmata nito determinista o AFD). Este autmata, bsicamente, sirve para re-

presentar grcamente los posibles estados del sistema, la funcin de transicin (es decir, los cambios

de estado ante cada combinacin de estado y entrada actuales) y la funcin de salida (es decir, el valor

de la salida correspondiente a cada estado, en el caso de tratarse de un autmata de Moore).

3. Minimizacin del autmata obtenido: puede ocurrir que la especicacin inicial del autmata sea

correcta (es decir, lleve a cabo la tarea a realizar perfectamente), pero pueda conseguirse el mismo com-

portamiento con un autmata equivalente con menor nmero de estados. En ese caso, nos interesar

hallar el AFD mnimo equivalente, con el n de reducir la circuitera que posteriormente ser necesaria.

Dejaremos el estudio de las tcnicas de minimizacin de autmatas para cursos posteriores, puesto que

en este curso trabajaremos con autmatas lo sucientemente simples como para no tener que preocu-

parnos por su minimizacin.

4. Codicacin de estados: una vez que conocemos el total de estados distintos en los que se podr

encontrar nuestro circuito, podemos decidir el nmero de ip-ops necesarios para codicarlos. En

concreto, si el autmata tiene M estados, necesitaremos n = log

2

M ip-ops. En esta etapa a cada

estado le asociaremos una combinacin de n bits. Esta asignacin de estados se puede hacer al azar

o buscando que el nmero de puertas necesarias en el circuito resultante sea mnimo a travs de un

conjunto de reglas que no veremos por falta de tiempo.

5. Minimizacin de la funcin de transicin: una vez que tenemos codicados los estados, minimizamos

la funcin de transicin (que ya es una funcin booleana combinacional normal y corriente). Con ello

obtenemos la expresin con la que implementaremos dicha parte del circuito.

16

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

6. Minimizacin de la funcin de salida: seguidamente haremos lo propio con la funcin de salida, que

en nuestro caso (al tratarse un autmata de Moore) depende nica y exclusivamente de la codicacin

de cada estado. Con ello obtenemos otra expresin booleana mnima, que usaremos para implementar

lo que nos queda del circuito.

7. Implementacin del circuito: nalmente, slo nos queda utilizar los n ip-ops (que estarn todos

conectados a una misma seal de reloj) y las expresiones obtenidas en los pasos 5 y 6 para dibujar el

circuito nal, siguiendo la estructura de la gura 17.

2.6.3. Ejemplo de diseo/sntesis de un circuito secuencial

En este apartado disearemos un circuito de ejemplo siguiendo el procedimiento indicado en el aparta-

do anterior. Elegiremos disear un circuito detector de una determinada secuencia de bits que le llegan por

una lnea serie, que podra utilizarse en una aplicacin de comunicaciones (por ejemplo, para detectar un

determinado carcter con un signicado especial en la conexin).

Especicacin verbal

Disear un circuito secuencial con una nica lnea de entrada X y una nica lnea de salida S. El circuito

debe ser capaz de detectar la aparicin de tres unos consecutivos (es decir, durante tres ciclos de reloj) en su

lnea de entrada X. En ese caso deber mostrar un uno en la salida S. En caso contrario deber producir un

cero. Si el circuito mostr un uno en la salida en el ltimo paso, entonces debe volver a comenzar a contar

unos en la entrada, y no volver a mostrar otro uno en la salida hasta que cuente otros tres unos en la entrada.

Realizar dos diseos, uno utilizando biestables J-K y otro utilizando biestables D, en ambos casos disparados

por anco ascendente.

Especicacin del autmata

En este caso el autmata de Moore que recoge el funcionamiento deseado para el circuito es el mostrado

en la gura 18. Obsrvese el empleo de crculos para cada estado Est

i

, la especicacin de la salida asociada

a cada estado, por tratarse de un autmata de Moore (funcin de salida) y la especicacin mediante echas

de las transiciones entre estados asociadas a cada entrada (funcin de transicin). En la tabla E2.1 se recoge

la misma informacin que en el diagrama pero mostrada en forma tabular.

Figura 18: Autmata nito determinista del circuito detector de secuencias de tres unos.

Codicacin de estados

Calculamos el nmero de ip-ops necesarios y asignamos una combinacin de bits a cada estado. En

este caso, al haber 4 estados, es suciente con dos ip-ops cuyas salidas sern Q

0

y Q

1

. Utilizaremos la

17

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Estado Siguiente Salida

Estado Actual X=0 X=1 S

Est

0

Est

0

Est

1

0

Est

1

Est

0

Est

2

0

Est

2

Est

0

Est

3

0

Est

3

Est

0

Est

1

1

Tabla 8: Tabla de transicin entre estados y funcin salida para el ejemplo explicado.

codicacin en binario natural (Est

0

= 00, Est

1

= 01, Est

2

= 10, Est

3

= 11).

Minimizacin de la funcin de transicin y de la funcin de salida

Una vez realizada la codicacin de estados el siguiente paso es reescribir dicha tabla haciendo uso de

la codicacin elegida tal y como se muestra en la tabla E2.2. Obsrvese que diferenciamos el estado futuro

(Q

i

) del actual (Q

i

) utilizando un asterisco.

Q

1

Q

0

Salida

Q

1

Q

0

X=0 X=1 S

00 00 01 0

01 00 10 0

10 00 11 0

11 00 01 1

Tabla 9: Tabla de transicin entre estados y funcin de salida con los estados ya codicados para el ejemplo

explicado.

Una vez realizada dicha codicacin debemos determinar qu valores deben de tener las entradas de los

biestables para que dicha transicin se realice en la salida. Para el caso de biestables tipo D el valor de la

entrada se corresponde con el que deseamos en la salida, pero en el caso de biestables tipo J-K debemos de

calcularlos en funcin del estado actual y del estado siguiente del biestable como se muestra en la tabla 10.

Q Q

J K

0 0 0

0 1 1

1 0 1

1 1 0

Tabla 10: Determinacin del valor de la entrada de un biestable J-K en funcin del estado actual y del estado

deseado.

La tabla 11 muestra el clculo de las entradas de excitacin cuando utilizamos biestables J-K mientras que

la tabla 12 hace lo mismo con biestables D. Obsrvese que no es necesario realizar una nueva tabla sino que

se puede aadir nuevas columnas a la tabla E2.2 en donde se calcule los valores de las entradas de excitacin

de los biestables a usar en la sntesis del circuito. La simplicacin para el caso de utilizar biestables J-K se

muestra en la gura 19, mientras que en 20 se muestra la simplicacin cuando utilizamos biestables tipo D.

Con biestables tipo J-K, el resultado de la simplicacin sera:

J

1

= Q

0

X; K

1

= X +Q

0

; J

0

= X; K

0

= X +Q

1

; S = Q

1

Q

0

Con biestables tipo D, el resultado de la simplicacin sera:

D

1

= Q

1

Q

0

X +Q

1

Q

0

X; D

0

= Q

1

X +Q

0

X; S = Q

1

Q

0

18

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Q

1

Q

0

J

1

K

1

J

0

K

0

Q

1

Q

0

X=0 X=1 X=0 X=1 X=0 X=1

00 00 01 0 0 0 1

01 00 10 0 1 1 1

10 00 11 1 0 0 1

11 00 01 1 1 1 0

Tabla 11: Clculo de los valores de las entradas de excitacin de los dos biestables tipo J-K.

0

1

1

3

-

7

-

5

0

0

0

2

-

6

-

4

0

1

00 01 11 10

X

Q

1

Q

0

(a) Simplicacin de J

1

-

1

-

3

1

7

0

5

-

0

-

2

1

6

1

4

0

1

00 01 11 10

X

Q

1

Q

0

(b) Simplicacin de K

1

1

1

-

3

-

7

1

5

0

0

-

2

-

6

0

4

0

1

00 01 11 10

X

Q

1

Q

0

(c) Simplicacin de J

0

-

1

1

3

0

7

-

5

-

0

1

2

1

6

-

4

0

1

00 01 11 10

X

Q

1

Q

0

(d) Simplicacin de K

0

0

1

1

3

0

0

0

2

0

1

0 1

Q

0

Q

1

(e) Simplicacin de S

Figura 19: Simplicacin de las entradas de los biestables JK y de la funcin de salida.

Q

1

Q

0

D

1

D

0

Q

1

Q

0

X=0 X=1 X=0 X=1

00 00 01 00 01

01 00 10 00 10

10 00 11 00 11

11 00 01 00 01

Tabla 12: Clculo de los valores de las entradas de excitacin de los dos biestables tipo D.

0

1

1

3

0

7

1

5

0

0

0

2

0

6

0

4

0

1

00 01 11 10

X

Q

1

Q

0

(a) Simplicacin de D

1

1

1

0

3

1

7

1

5

0

0

0

2

0

6

0

4

0

1

00 01 11 10

X

Q

1

Q

0

(b) Simplicacin de D

0

0

1

1

3

0

0

0

2

0

1

0 1

Q

0

Q

1

(c) Simplicacin de S

Figura 20: Simplicacin de las entradas de los biestables D y de la funcin de salida.

19

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Implementacin del circuito

Ya slo nos queda implementar el circuito con ip-ops y puertas lgicas. La gura 21 muestra cmo

queda dicha implementacin, en la que se han utilizado ip-op tipo D activos en anco ascendente (se deja

para el alumno la implementacin con biestables J-K por ser la misma directa a partir de las ecuaciones

obtenidas en el apartado anterior).

Figura 21: Implementacin del circuito utilizando biestables tipo D (la implementacin con biestables JK

sera similar).

Finalmente, en la gura 22 mostramos un cronograma de ejemplo de funcionamiento del circuito, para

una determinada secuencia de entrada. Si miramos los valores binarios de las seales, superpuestos sobre el

cronograma, podemos observar cmo el valor de la entrada se lee en los instantes marcados por los ancos

activos de la seal de reloj (en este caso el ascendente), mientras que los valores del estado y la salida pueden

leerse a lo largo de todo el ciclo que comienza en ese momento, hasta que posiblemente cambien en el siguiente

anco activo. Por simplicidad, en el cronograma se supone un retardo nulo para todos los componentes del

circuito.

Es tambin instructivo reexionar sobre la frecuencia mxima de operacin de un circuito de estas ca-

ractersticas. En principio, esta frecuencia mxima depender directamente del retardo introducido por sus

componentes. La mejor manera de verlo es con un ejemplo. Si suponemos retardos despreciables para las co-

nexiones, de 10 ns para las puertas lgicas AND y OR, y 20 para los ip-ops tipo D, observando el diagrama

del circuito de la gura 21 nos daremos cuenta de que, como mnimo, desde que comienza un nuevo ciclo las

seales de la entrada actual y el estado anterior atravesarn un nivel de ip-ops, un nivel de puertas AND y

otro de puertas OR para que las entradas de los biestables queden de nuevo estables (nuevo estado siguiente).

Las distintas puertas y ip-ops de cada tipo operan en paralelo entre s. La salida, al calcularse con un solo

nivel AND que opera en paralelo con los anteriores, no introduce retardo adicional. As, el retardo total para

actualizarse el estado ser: 20 ns (ip-op) + 10 ns (AND) + 10 ns (OR) = 40 ns.

Este es el tiempo mnimo que debemos dejar transcurrir antes de que llegue el prximo anco activo de

la seal de reloj, puesto que si no la actualizacin del estado no se realizar de forma correcta. Por tanto, la

frecuencia mxima de operacin sera de: 1/(40 ns) = 1/(4010

9

s) = 0,02510

9

Hz = 2510

6

Hz = 25 MHz.

20

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Figura 22: Cronograma de ejemplo mostrando el funcionamiento dinmico del circuito.

21

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Apndices

A2.1. Construccin fsica de una celda de memoria

En este apndice analizaremos las distintas alternativas de diseo de una celda de memoria, tanto en su

versin esttica (SRAM) como dinmica (DRAM).

Celda SRAM

Figura A2.1: Implementacin con transistores MOS de una celda de memoria SRAM: Esquemtico (izq) y

microfotografa (der).

La caracterstica principal de las memorias SRAM es que el tiempo de acceso es muy corto, por ello se

emplean principalmente en el diseo de memorias cach.

En la gura A2.1 se muestra el diseo de una celda bsica de memoria SRAM utilizando transistores

NMOS. Como vemos, se dispone de una patilla de seleccin de celda WL y de las lneas de datos BL y BL.

Partimos de dos inversores acoplados (Q

1

Q

3

y Q

2

Q

4

) y se aaden otros dos (Q

5

Q

6

) para habilitar

la lectura/escritura. Con este diseo, supondremos que se almacena un 1 cuando Q

1

est conduciendo y Q

2

est cortado. El funcionamiento sera el siguiente:

Seleccin de celda: la seleccin de celda se producir introduciendo un nivel alto (1) en WL, pro-

vocando que los transistores Q

5

y Q

6

conduzcan y que, por lo tanto, se pueda leer o escribir en la

celda.

Lectura: tras seleccionar la celda con WL, Q

5

y Q

6

conducirn y, por lo tanto, los valores de los puntos

A y B aparecern en las lneas BL y BL, respectivamente.

Escritura: se empieza seleccionando la celda mediante WL e introduciendo el dato que queremos

almacenar (nivel lgico 1) por BL y BL. Por ejemplo, supongamos que se quiere introducir un 0;

para ello, activaremos WL e introduciremos un 0 por BL y un 1 por BL. Un 0 en BL provoca

que la puerta de Q

2

se polarice a 0V y, por lo tanto, corte y la V

DS

= V

DD

. Dicha tensin se aplica a la

puerta de Q

1

y por lo tanto V

GS1

= V

DD

. Esto provoca que Q

1

conduzca y, por lo tanto, su V

DS

= 0V ,

reforzando y memorizando el nivel inicialmente introducido de 0V.

22

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Finalmente, es importante darse cuenta que el circuito mostrado en la gura A2.1 no es sino la implemen-

tacin fsica de un cerrojo tipo D, como el mostrado en la gura 3, en donde WL desempea el papel de la

entrada C, y BL y BL equivalen a las lneas Q y Q, respectivamente.

Celda DRAM

(a) Implementacin con 4 transistores (b) Implementacin con 1 transistor. (a) Solucin mnima que

provoca lectura destructiva. (b) Alternativa vlida. (c) Formas

de onda durante la lectura y la escritura.

Figura A2.2: Celda de Memoria DRAM.

En la gura A2.2(a) se puede apreciar un primer diseo de celda DRAM. Si se compara con la celda

esttica se aprecia que se han eliminado dos transistores y que el elemento almacenador de informacin son

los condensadores C

1

y C

2

. Estos condensadores no se implementan explcitamente en la celda, sino que son

las capacidades parsitas de los propios transistores las que sirven como elementos almacenadores. Para evitar

la prdida de carga de estos condensadores se introduce un sistema de refresco a travs de los transistores Q

11

y Q

12

que hace que la informacin de salida se vuelva a meter en la entrada.

El paso siguiente es pasar de cuatro a tres transistores. Se consigue en base a eliminar la redundancia

de almacenamiento, ya que hasta este momento se almacena la informacin deseada y su complementaria.

Como ahora la clula de almacenamiento es la capacidad parsita del transistor MOS, no es necesaria dicha

redundancia y por lo tanto se puede eliminar la mitad de la celda. La ltima reduccin del tamao de celda en

la RAM dinmica consiste en utilizar un nico transistor y su capacidad parsita como elemento almacenador

tal y como se aprecia en la gura A2.2(b).

Su funcionamiento es sencillo, basta un transistor que permita la entrada y salida de carga al condensador.

Durante el ciclo de escritura se habilita la celda mediante WL y se introduce el nivel en la entrada BL; al

conducir Q

1

, dicha carga se introduce en C

1

y queda almacenada. Para su lectura, simplemente se habilita la

celda mediante WL, provocando que Q

1

conduzca y que, por lo tanto, el valor de C

1

aparezca en BL.

Para nalizar, en la gura A2.3(arriba) se observa la evolucin de las celdas DRAM conforme ha sido ne-

cesario reducir su tamao para conseguir mayor capacidad de integracin. Finalmente, en la gura A2.3(abajo)

se muestra una microfotografa de una celda de la primera memoria, con una capacidad de un 1 Mbit, en donde

se utiliz condensadores de zanja (trench capacitor) que permiten una mayor capacidad de integracin.

23

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Figura A2.3: Evolucin de la tecnologa DRAM (arriba) y microfotografa del la primera memoria con con-

densadores de zanja (abajo).

24

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Boletines de prcticas

B2.1. Normas sobre la entrega de prcticas

Ser necesario seguir las siguientes reglas para entregar las prcticas:

Las prcticas se entregarn mediante la opcin de contenidos del alumno en SUMA.

Se entregar un nico archivo comprimido en formato .tar.gz o .zip que contendr la memoria en formato

PDF, los circuitos y programas que se hayan generado (cdigo fuente) y cualquier otro chero que se

considere oportuno. El nombre del archivo ser prcticas-DNI-BOLETIN.FORMATO (por ejemplo:

prcticas-12345678-B2.3.tar.gz).

La memoria incluir, al menos, la siguiente informacin en un solo documento PDF:

Nombre y DNI del autor o autores de la prctica.

Descripcin de los cheros y directorios contenidos en el archivo entregado.

Contestacin a las preguntas planteadas en los boletines. La respuesta a cada pregunta debe ser

independiente, y debe estar clramente identicada.

Explicacin de las pruebas realizadas para comprobar la correccin de la prctica entregada e

instrucciones para su reproduccin. Cuando sea posible, se incluirn los cheros utilizados en

dichas pruebas.

Explicacin del trabajo realizado y cualquier aclaracin que el alumno considere pertinente.

Lista de bibliografa y otras fuentes de informacin consultadas.

No se corregir ninguna prctica que no se cia estrictamente a los formatos especicados anteriormente.

B2.2. Implementacin de un Archivo/Banco de Registros con TkGate

B2.2.1. Objetivos

El objetivo de esta sesin es que el alumno disee un Archivo/Banco de Registros, elemento secuencial

fundamental en el diseo de un procesador tal y como veremos en temas posteriores, utilizando la herramienta

TkGate.

B2.2.2. Prerequisitos

Haber ledo los apuntes de teora.

B2.2.3. Plan de trabajo

El plan de trabajo de esta sesin ser el siguiente:

1. Lectura por parte del alumno de la seccin B2.2.4.

2. Realizacin individual del ejercicio propuesto en el boletn (con supervisin del profesor).

25

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

B2.2.4. Archivo/Banco de Registros

Un archivo/banco de registros no es ms que un conjunto de registros que pueden ser ledos y escritos

selectivamente, a travs de unas entradas y salidas que denominaremos, respectivamente, puertos de escritura

y de puertos de lectura. La implementacin se realiza mediante una serie de registros construidos mediante

ip-ops tipo D, y usando multiplexores y decodicadores para seleccionar el/los registros concretos que se

leen/escriben en los puertos de lectura y escritura, respectivamente. Como al leer un registro no cambia ningn

estado, solamente necesitamos dar como entrada un nmero de registro (podemos pensar en este nmero como

en una direccin), y en el puerto de salida correspondiente aparecer el dato contenido en ese registro. Para

escribir en un registro indicado por su nmero (o direccin) necesitaremos tres entradas: el nmero de registro,

el dato a escribir y una seal de control de escritura que, junto con el reloj, controle el momento en el que se

desea escribir el dato. En la gura B2.1 puede verse el esquema genrico de un archivo de M registros de n

bits con dos puertos de lectura y uno de escritura. A la derecha aparece el bloque lgico de un archivo de 32

registros de 32 bits, con dos puertos de lectura y uno de escritura, como el que se emplear en la construccin

del camino de datos del MIPS en el tema 4.

Figura B2.1: (Izquierda) Archivo de registros con 2 puertos de lectura y 1 puerto de escritura. (Derecha)

Archivo de registros que usaremos en el camino de datos del MIPS.

B2.2.5. Ejercicios

Para cada ejercicio, el portafolios deber incluir una explicacin de cmo se ha resuelto el mismo, los

cheros con los diferentes mdulos/circuitos y, para cada uno de ellos, un cronograma en donde se mues-

tre el funcionamiento del mismo bajo diferentes situaciones con el n de que se pueda apreciar el correcto

funcionamiento del circuito.

1. Construir el mdulo denominado BufferTriestado8. Se trata de un buffer triestado en donde la entrada

y salida es de 8 bits y que utilizaremos para implementar un multiplexor.

2. Utilizando como base el buffer triestado del apartado anterior y un decodicador de 3 a 8, cree un

mdulo denominado Multiplexor8 que implemente un multiplexor de 8 a 1 con entradas y salidas de

8 bits. Compruebe el funcionamiento del circuito resultante mediante un cronograma en el que se pueda

observar la respuesta del circuito ante diversos valores de las seales de entrada.

3. Utilizando 8 registros tipo D, disee un archivo de registros con 2 puertos de lectura y 1 de escritura

capaz de dar acceso a los 8 registros mencionados. El archivo de registros poseer adems una entrada

adicional, CLR, activa en alta que permita poner a cero el contenido de todos los registros. Encapsule

26

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

el circuito resultante en el mdulo "BancoRegistros8". El encapsulado resultante debera ser similar al

que se muestra en la gura B2.2.

Designer:

Site:

Date:

Document:

Page:

Module:

Antonio Flores Gil,,,

Earth

October 26, 2010

BancoRegistros.v

1 of 1

main TKGate 2.0b10

8

8

3

on

off

1

ON

OFF

P = 1000 = 0 D = 50

16

16

2

ON

OFF

0

ON

OFF

1

ON

OFF

on

off

CLR Reloj

DatoaEscribir

RegEscritura

RegLectura1

RegLectura2

Escribir

DatoLeido1

DatoLeido2

BancoRegistros8

Figura B2.2: Banco de 8 registros con dos puertos de lectura, uno de escritura y seal de clear.

4. Compruebe el funcionamiento del circuito mediante un cronograma en el que se pueda observar diver-

sas operaciones de lectura y escritura (al menos 5). Determine la frecuencia mxima a la que puede

funcionar este circuito.

27

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Ejercicios

E2.1. Sistemas Digitales: Circuitos Secuenciales

1. Disear un circuito secuencial sncrono, utilizando ip-ops tipo J-K, con 1 variable de entrada X, tal

que tenga como salida Z un 1 si y slo si los dos ltimos bits de entrada recibidos valan igual (dos ceros

o dos unos).

2. Obtener la tabla de estados del circuito de la gura. Realiza la funcin de algn circuito conocido?

3. Dibujar el cronograma y obtener la secuencia de cuenta del contador de la gura:

Cul es la frecuencia mxima de funcionamiento si el retraso de un biestable es de 40 ns?

4. Disear un circuito secuencial sncrono, utilizando ip-ops tipo D, sin variables de entrada (excepto el

reloj), tal que tome como salida, sucesivamente, los valores 0, 1, 2 y 3 en binario natural (es decir, 00,

01, 10 y 11; es un contador sncrono de 2 bits, o lo que es lo mismo, de 4 estados).

5. Disear un circuito, con el mnimo nmero de componentes, que proporcione a sus 3 salidas el equi-

valente binario de la secuencia 5 - 2 - 4 - 1, en cuanto reciba una orden de activacin por su entrada

START. Cuando esta orden cese, el circuito quedar con el estado en que se encontrase en ese instante,

esperando a que se produzca de nuevo la activacin de START para comenzar a generar la secuencia.

Utilizar biestables tipo S-R.

6. Se desea activar un circuito de toma de datos cuando la informacin presente en 3 lneas de los buses del

28

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

circuito bajo test evolucionan del siguiente modo: 000 - 001 - 010 - 100. Realizar el diseo utilizando

ip-ops tipo T.

7. Disear un contador sncrono con biestables J-K que cuente segn la secuencia: 0 - 1 - 6 - 7 - 2 - 3 - 4 -

5 - 0. Calcular la mxima frecuencia de funcionamiento, si el retraso de un biestable J-K es de 50 ns y

el de una puerta AND/OR 10 ns.

8. Dibujar el cronograma y obtener la secuencia de cuenta del contador de la gura:

Cul es la frecuencia mxima de funcionamiento si el retraso de un biestable es de 40 ns, el de una

puerta AND 20 ns y el de una XOR 25 ns?

9. dem para la gura:

Cul es la frecuencia mxima de funcionamiento si el retraso de un biestable es de 40 ns, el de una

puerta AND 20 ns y el de una XOR 25 ns?

10. El autmata de Moore de la siguiente gura expresa el funcionamiento requerido para un circuito se-

cuencial sncrono que implementar un contador ascendente/descendente de tres estados. Se observa

que el circuito debe tener dos entradas, S y B (de Sube y Baja, respectivamente), y como salida un valor

binario natural de dos bits, X

1

y X

0

.

29

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

Cuando las entradas S y B valgan ambas cero, el circuito no cambia de estado. Cuando S valga uno y

B cero, entonces el nmero de estado se aumenta en una unidad, salvo que ya estemos en el estado ms

alto (de 00 se pasa a 01, de 01 a 10, y si estamos en 10 permanecemos en l). Si B vale uno y S cero,

entonces el estado se decrementa, salvo que ya estemos en el estado ms bajo (de 10 se pasa a 01, de 01

se pasa a 00, y si estamos en 00 permanecemos en l). La entrada S=B=1 no est permitida.

Construir el circuito secuencial sncrono simplicado que implemente dicho autmata, utilizando

ip-ops tipo T, activos en el anco descendente.

Rellenar el siguiente cronograma de funcionamiento:

11. El siguiente autmata de Moore expresa el funcionamiento requerido para un circuito secuencial sn-

crono que implementa un controlador de un sistema de tres luces (L1 L2 L3) que se van encendiendo

sucesivamente de izquierda a derecha y de derecha a izquierda, del modo indicado. Se observa que el

autmata tiene una sola entrada E, que hace la funcin de reset, de modo que mientras vale 0 el sistema

opera en el modo cclico habitual anteriormente indicado, pero que cuando vale uno fuerza al sistema a

colocarse en su estado inicial (L1 encendido y L2 y L3 apagados).

Se pide construir el circuito secuencial sncrono simplicado que implemente dicho autmata, utilizan-

do ip-ops tipo J-K, activos en el anco descendente.

12. Repetir el ejercicio anterior, pero cambiando el controlador para un sistema de 4 luces (en lugar de 3),

que siga la misma regla de funcionamiento (de izquierda a derecha y viceversa, tambin con una seal

de reset). Utilizar biestables tipo T en lugar de J-K.

30

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

13. Disee un circuito secuencial sncrono con biestables tipo D disparados por anco ascendente y usando

un autmata de Moore que tenga tres entradas (E

2

, E

1

y E

0

) y una salida (S). La salida se activar si

el valor de las tres entradas ha coincidido durante los tres ltimos ciclos. Es decir, si E

i

(t) es el valor

de la entrada E

i

al comienzo del ciclo t, S valdr 1 en el ciclo t si y slo si E

0

(t) = E

1

(t) = E

2

(t) ,

E

0

(t 1) = E

1

(t 1) = E

2

(t 1) y E

0

(t 2) = E

1

(t 2) = E

2

(t 2).

a) Dibuje el autmata que modela el comportamiento del circuito, incluyendo para cada estado el valor

de la salida.

b) Realice la asignacin de estados que crea conveniente y obtenga las expresiones minimizadas de las

funciones de transicin y de salida.

c) Dibuje el circuito que implementa el autmata usando solo puertas NAND y biestables tipo D.

d) Calcule la frecuencia mxima a la que puede operar el circuito resultante. El retardo de las puertas

NAND es de 15 ns y el de los biestables es de 50 ns.

e) Se podra implementar la funcin de transicin mediante un PLA? Si se puede: cules seran las

dimensiones de dicho PLA?. Si no se puede: por qu?

14. Obtener los estados del registro de 5 bits mostrado (inicialmente 0000), para las seales de reloj (CLK)

y entrada de datos (IN) indicadas.

15. Hacer un diagrama de tiempos de un registro de desplazamiento con entrada serie y 4 salidas paralelas

(A-B-C-D), suponiendo que est compuesto de biestables tipo D con entrada de reloj activa en anco

de bajada y que la entrada serie aplicada es la mostrada a continuacin. Qu dato se obtendra tras 6

ciclos de reloj?

31

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

16. Determinar el estado en cada pulso de reloj de un registro de desplazamiento universal bidireccional de

4 bits en el que se aplican las seales de entrada y de control mostradas (sincronizacin con anco de

subida del reloj). Suponer que solo CLR es asncrona y que las seales de control S0-S1 codican el

siguiente comportamiento: S0=S1=1, carga paralela (D0-D3); S0=S1=0, no hay cambios; S0=0 y S1=1,

desplazamiento a la izquierda; y S0=1 y S1=0, desplazamiento a la derecha. SR-ser y SL-ser son las

entradas de datos serie derecha e izquierda respectivamente.

A continuacin se muestra un esquema de la implementacin del desplazador y el cronograma que se

debe completar.

Clk

Q D

Clr

Pr

0

l

2

3

S

l

S

0

PR

CLR

CLK

Q

3

Q

3

Q

2

R

lN

D

3

Clk

Q D

Clr

Pr

0

l

2

3

S

l

S

0

PR

CLR

CLK

Q

2

Q

2

Q

l

Q

3

D

2

Clk

Q D

Clr

Pr

0

l

2

3

S

l

S

0

PR

CLR

CLK

Q

l

Q

l

Q

0

Q

2

D

l

Clk

Q D

Clr

Pr

0

l

2

3

S

l

S

0

PR

CLR

CLK

Q

0

Q

0

L

lN

Q

l

D

0

S

l

S

0

=0l (Despl. dcha)

S

l

S

0

=00 (Hold)

S

l

S

0

=ll (carga sncronaparalelo)

S

l

S

0

=l0 (Despl. izqda)

R

lN

D

3

D

2

D

l

D

0

L

lN

S

l

S

0

=0l (Despl. dcha)

S

l

S

0

=00 (Hold)

S

l

S

0

=ll (carga sncronaparalelo)

S

l

S

0

=l0 (Despl. izqda)

R

lN

R

lN

D

3

D

2

D

l

D

0

D

3

D

3

D

2

D

2

D

l

D

l

D

0

D

0

L

lN

L

lN

32

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

17. Disee el circuito secuencial sncrono con una entrada X y un bit de salida (S) que vendra especicado

por el siguiente autmata nito determinista, utilizando ip-ops T disparados por anco descendente:

Est

1

/0 Est

2

/1

Est

3

/0 Est

4

/0

X=0

X

=

1

X

=

0 X

=

1

X

=

0

X

=

1

X

=

0

X=1

18. Implementar, utilizando biestables tipo D disparados por anco descendente, un circuito capaz de de-

33

Tema 2: Sistemas Digitales - Circuitos Secuenciales Estructura y Tecnologa de Computadores

tectar un retraso de un ciclo entre dos seales de un bit. El circuito tendr dos entradas, A y B, y una

salida, S, que se pondr a 1 siempre que la entrada B se corresponda con la A del ciclo anterior. En el

momento en que esta condicin no se cumpla la salida quedar jada a 0 hasta que una seal de Reset,

activa en baja, vuelva a iniciar el proceso de comprobacin. En el primer ciclo de reloj, donde la sali-

da todava no tiene sentido, supondremos que se cumple la condicin. (Pista: Observad que solamente

necesito saber si hasta el momento se est cumpliendo la condicin y el valor anterior de A para poder

implementar el circuito.)

19. Dado el sistema secuencial sncrono que se muestra a continuacin se pide:

D0

Q0

Q0

Reloj

J

1

Q1

Q1

Y

A

K1

a) Rellenar el siguiente cronograma:

Reloj

A

J

1

Q

1

D

0

Q