Professional Documents

Culture Documents

Lab3.Design Project - Ee140.s12.v1

Uploaded by

frankongOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lab3.Design Project - Ee140.s12.v1

Uploaded by

frankongCopyright:

Available Formats

EE 140

ANALOG INTEGRATED CIRCUITS CMOS Operational Amplifier Design Problem

SPRING 2012 C. Nguyen

Issued: Tuesday, March 20, 2012 Due: Friday, May 4, 2012

CMOS operational amplifiers have become an integral part of many integrated circuit chips fabricated today in a number of application areas. These amplifiers offer a number of advantages in terms of power dissipation, die area, and compatibility with digital circuits when compared with their bipolar counterparts. Therefore, it is important that anyone taking EE 140 have an in-depth understanding of the tradeoffs and issues involved in the design of these op amps. This understanding is best acquired by actually designing an op amp from beginning to end. Thus, in this lab you are asked to design and simulate a CMOS operational amplifier that can satisfy the set of specifications given. You do not need to create a layout for the amplifier. However, you may have to perform some analysis in order to estimate the source/drain areas and perimeters of the transistors to calculate junction capacitances. Make sure that you follow the guidelines listed below: 1- You are to work on this design project individually. Although you can discuss generalities with other students in the class, you are not to perform the design in teams or groups. The chances of any two people coming up with the same exact design are very slim. Therefore, we expect to see different designs from each one of you. 2- You are not required to do a layout for this amplifier. However, you do need to make sure that you take into account all the important layout effects and parameters. In particular, all the parasitic capacitances from pn junctions should be included. This means that you need to specify the areas and relevant perimeters of the drain and source for each transistor. You should estimate these areas based on design rules (where the lengths of the drains and sources are 5) and on the designed dimensions of the individual transistors. (Note that this is not the same as the LAMBDA parameter in SPICE model definitions; its just an unfortunate coincidence that they have the same name. Also note that design rules were covered in the first few lectures of this course.) Note that your SPICE device models automatically compute source/drain areas and perimeters, so you need not include them specifically in your spice netlist. However, you do need to compute source/drain areas and perimeters and account for them in your hand analysis. 3- You are not necessarily supposed to use any design tool other than SPICE. You can use any version of SPICE you like, so long as we have access to your SPICE code. Be aware, however, that HSPICE is preferred. 4- Assume that = 65 nm for the technology to be used for this design. This means that every dimension used must be a multiple of 65 nm, and that the minimum feature size in this technology is 2 = 130 nm. In other words, the minimum drawn gate length is 130 nm. In addition, the lengths of the transistor drains and sources are 5 = 325 nm. Use this information to determine drain and source areas and perimeters for your calculations. Note that you do not need to perform a detailed layout; a realistic estimation of areas and relevant perimeters is sufficient. It is suggested that you use a minimum width of 3 = 195 nm for the transistors in your circuit. This will minimize circuit performance variations due to integrated circuit fabrication process variations. 5- Although you can use a resistor in your VBIAS-generator (but not an excessively large one), do not use physical resistors in your op amp. If you need a resistor, use an MOS resistor.

CTN 3/20/12

EE 140

ANALOG INTEGRATED CIRCUITS

SPRING 2012 C. Nguyen

6- Your design approach should be outlined in your final report on this project. It is suggested that you use the following approach: a- Start with a circuit topology and perform hand calculations to come up with the estimates of the various parameters; b- Confirm the operation of the circuit using SPICE; c- Include all parasitics and important layout characteristics and redo simulations; d- Iterate design and re-simulate until all specs are met; e- Write your report. 7- Your final report should be concise and complete. The report should be typewritten, and should be divided into the following sections (with page limits strictly observed using 12pt font sizes and reasonably-sized figures): Overview (1-2 pages): Complete schematic and basic description of circuit operation (including biasing). Your schematic should include device sizes next to each transistor. This section should not contain design discussion. Design (1-3 pages): A brief discussion of your design approach, specifically identifying important constraints. Note that you may have to provide some basic and important equations used in your design. Transistor and Bias Summary (1 page): A table listing for each transistor, the dimensions, drain bias current, the magnitude of the gateto-source voltage, the transconductance, and the output conductance; Performance (1 page): A table comparing the simulated performance with the design objectives. This table should be as complete as possible and should include all the op-amp performance specifications. Discussion (<10 pages, plus figures): A discussion of circuit performance with special attention paid to unique areas in your design which helped/hurt your attempts to meet the specifications. This is the most important section, in that it provides the validation for your design. Each of the performance specifications listed below should be validated in a subsection. You may want to include a diagram of the circuit you used, the justification for its use, and the simulation results or output data showing that it has met the needed specifications. Note that you should show simulation results for all the specifications. For each, select an appropriate circuit topology (i.e., input sources, current measuring sources, etc.) for measurement. Conclusion (1 page): A summary of your design experience. You should summarize the overall op amp characteristics, and should describe your overall experience and what you learned in doing this design. It would be good to get some feedback from you, both good and bad. Tell me if the design problem was worth the effort. (Your comments here will not adversely affect your grade.) You should try your best to achieve the following design specifications. If after all attempts you fail to meet all the design specifications, describe your optimum and final design and describe in your report what you consider to have been the most restrictive and problematic spec to meet. Also discuss how that particular spec could be improved, i.e., discuss tradeoffs between various parameters, etc. Your report should indicate that you have tried many different techniques and have not been able to achieve any particular specification. Note that normally many students do a decent job in the design of the op-

CTN 3/20/12

EE 140

ANALOG INTEGRATED CIRCUITS

SPRING 2012 C. Nguyen

amp. Therefore, the quality of the report, both in terms of technical contents and presentation, will be very important in determining your final project grade. The grade sheet to be used for grading the reports is provided at the end of this document so you can see how the project grade is distributed. If you are able to design the following op-amp, satisfying all specifications, then make sure that your report describes your overall design approach and procedure.

The design specifications for the CMOS operational amplifier are given below:

Parameter Lmin Wmin DC Gain Common-Mode Input Range Output Swing Power Dissipation (includes Biasing) Unity Gain Frequency Settling Time for Unity Gain Buffer (0.4 V Input Step) CMRR at DC PSRR Load Capacitance Supply Voltage Specification 130 nm 195 nm 1000 0.5V (inside the output swing range) Within 0.15 V of supply Minimize (less than 1.5mW) 800 MHz 8 nsec to 0.1% for both rising and falling inputs 75 dB 60 dB at DC 50 dB at 1 MHz 2 pF V = 1.2 V, V = 0 V

DD SS

The following device parameters are to be used in your circuit simulation: SPICE PARAMETERS FOR USE WITH OP-AMP DESIGN AND SIMULATION Parameter Level VTO U0 GAMMA LAMBDA (@ L=130nm) TOX LD LDIFF HDIFF PHI (=2f) CJ MJ CJSW MJSW NMOS 2 0.3V 250cm2/Vs 0.2 V

-1

PMOS 2 -0.3V 100cm2/Vs 0.2 V

-1

0.2 V 2.6 nm 0.025m 65 nm 130 nm 0.6V 800 F/m 0.5 8 pF/m 0.5

2

0.15 V 2.6 nm 0.025m 65 nm 130 nm 0.6V 800 F/m 0.5 8 pF/m 0.5

2

CJGATE

80 pF/m

80 pF/m

CTN 3/20/12

EE 140

ANALOG INTEGRATED CIRCUITS

SPRING 2012 C. Nguyen

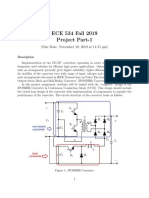

You will be provided with the model file. The device models are encapsulated in a sub-circuit in order to automatically account for the channel length modulation effect. You must use the prefix x instead of m when instantiating a device. For example: x1 d g s b nmos w=1u l=130n x2 d g s b pmos w=1u l=130n The meanings of the parameters HDIFF and LDIFF are illustrated in the figure below. CJGATE is the zero-bias gate-edge sidewall bulk junction capacitance.

The following grading scheme will be used to grade the design project reports. Note that you should make sure that all the components that were mentioned above are included in your report even though they are not specifically mentioned in the table below. Write the best report you can because the distribution is typically very tight on the project reports and a few points can make all the difference.

Evaluation of Reports On CMOS Op-Amp Design Project

Maximum Report Preparation and Presentation Overview Design Summary Discussion Conclusions Overall Presentation Design Techniques and Results Hand Design Simulation Results and Techniques Design Issues and Tradeoffs Achievement of Specs Minimization of Power Consumption Overall Effort TOTAL 110 (8) 5 5 15 5 10 10 20 10 15 10 5 Your Grade

Note from the table that power consumption should be less than 1.5 mW, but should also be minimized. In other words, the lower the power consumption, the higher the grade for this part.

CTN 3/20/12

You might also like

- High-Performance D/A-Converters: Application to Digital TransceiversFrom EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNo ratings yet

- Design Project: (Due: Friday, December 8, 2006, 5pm PT)Document6 pagesDesign Project: (Due: Friday, December 8, 2006, 5pm PT)Ibrahim MuhammedNo ratings yet

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsFrom EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsNo ratings yet

- Design Report Format BSCS KfueitDocument16 pagesDesign Report Format BSCS KfueitMaryam AsadNo ratings yet

- Lab1 Ee140 s13 v1Document6 pagesLab1 Ee140 s13 v1Mohd YasirNo ratings yet

- 2011 5333 Harjani ProjectDocument4 pages2011 5333 Harjani ProjectfammafNo ratings yet

- Class AbDocument7 pagesClass Abdemos2011No ratings yet

- Isscc2022 000002CLDocument16 pagesIsscc2022 000002CLdashuai huaNo ratings yet

- Project Format and Weightage: Analog Subsystem Design, EEE C443 February 6, 2012Document3 pagesProject Format and Weightage: Analog Subsystem Design, EEE C443 February 6, 2012Anurag LaddhaNo ratings yet

- Hspice UseDocument28 pagesHspice Useprasanna810243No ratings yet

- Isscc2022 000046CLDocument16 pagesIsscc2022 000046CLdashuai huaNo ratings yet

- Cadence Tutorial - Analog Design FlowDocument57 pagesCadence Tutorial - Analog Design FlownarashimarajaNo ratings yet

- ADVD Analog Assignment - 2023ssDocument36 pagesADVD Analog Assignment - 2023ssNimit JainNo ratings yet

- FVofDiffOpAmp WPDocument51 pagesFVofDiffOpAmp WPmarius260No ratings yet

- Analog Assignment ADVDDocument24 pagesAnalog Assignment ADVDRajeevDuttNo ratings yet

- AP0107 Impedance-Controlled RoutingDocument6 pagesAP0107 Impedance-Controlled RoutingdrakenhavenNo ratings yet

- EE 214 Design Project: 1 Problem Definition and Design GoalsDocument5 pagesEE 214 Design Project: 1 Problem Definition and Design GoalsSeda ToyNo ratings yet

- NFE2159 Assignment Brief 17-18 Embedded SystemDocument11 pagesNFE2159 Assignment Brief 17-18 Embedded SystemShaikh Bilal Mehmood0% (1)

- Frequency Response of A CMOS Common-Source Amplifier: Experiment # 5Document10 pagesFrequency Response of A CMOS Common-Source Amplifier: Experiment # 5Md. Sadique SheikhNo ratings yet

- Analog Design Assignment: Analog and Digital VLSI Design - EEE C443 February 1, 2012Document9 pagesAnalog Design Assignment: Analog and Digital VLSI Design - EEE C443 February 1, 2012srishaharidasNo ratings yet

- You Should Try To MinimizeDocument5 pagesYou Should Try To MinimizeSunwoo LeeNo ratings yet

- Designing Multi-Stage Class C Amplifiers For Pulsed Radar ApplicationsDocument8 pagesDesigning Multi-Stage Class C Amplifiers For Pulsed Radar ApplicationsA. VillaNo ratings yet

- Esign Hapter Pdates: A, M - S RF S DT T CDocument5 pagesEsign Hapter Pdates: A, M - S RF S DT T Cochie_loverNo ratings yet

- Analog & Digital VLSI Design Practice QuestionsDocument24 pagesAnalog & Digital VLSI Design Practice QuestionsAbhinav MishraNo ratings yet

- Thesis On Pipeline AdcsDocument6 pagesThesis On Pipeline Adcsamyholmesmanchester100% (2)

- Massachusetts Institute of Technology Department of Electrical Engineering and Computer ScienceDocument7 pagesMassachusetts Institute of Technology Department of Electrical Engineering and Computer ScienceFernando Sánchez HernándezNo ratings yet

- Reaction Timer Lab Report GuideDocument2 pagesReaction Timer Lab Report GuideMichael FiorelliNo ratings yet

- EEE 52: Electronic Circuits Laboratory I Project: Multi-Stage Amplifier With Adjustable GainDocument3 pagesEEE 52: Electronic Circuits Laboratory I Project: Multi-Stage Amplifier With Adjustable GainJaniessy ZozobradoNo ratings yet

- ECE 534 Project 1 F19Document6 pagesECE 534 Project 1 F19JAY CHHEDANo ratings yet

- Top-Down, Constraint-Driven Design Methodology Based Generation of N-Bit Interpolative Current Source D/A ConvertersDocument4 pagesTop-Down, Constraint-Driven Design Methodology Based Generation of N-Bit Interpolative Current Source D/A ConvertersImen Ben MansourNo ratings yet

- Microwave Amplifier Design and Smith Chart Utility For Z Matching Network Using ADSDocument29 pagesMicrowave Amplifier Design and Smith Chart Utility For Z Matching Network Using ADSZeeshan AhmedNo ratings yet

- Isscc2022 000109CLDocument16 pagesIsscc2022 000109CLdashuai huaNo ratings yet

- ESE 570 Cadence Lab Assignment 2: Introduction To Spectre, Manual Layout Drawing and Post Layout Simulation (PLS)Document7 pagesESE 570 Cadence Lab Assignment 2: Introduction To Spectre, Manual Layout Drawing and Post Layout Simulation (PLS)Parul TrivediNo ratings yet

- Isscc2022 000016CLDocument17 pagesIsscc2022 000016CLdashuai huaNo ratings yet

- EEE3602 AssignmentDocument5 pagesEEE3602 AssignmentUmair NazeerNo ratings yet

- Lab IV Lecture 2: Step 1 Review Introduce Step 2 Course Web PageDocument38 pagesLab IV Lecture 2: Step 1 Review Introduce Step 2 Course Web PageKulanthaivelu RamaswamyNo ratings yet

- Attachment 2Document5 pagesAttachment 2Brandon WanyonyiNo ratings yet

- Vlsi Laboratory: List of ExperimentsDocument49 pagesVlsi Laboratory: List of ExperimentssantoshNo ratings yet

- PDN Analyzer Demonstration GuideDocument24 pagesPDN Analyzer Demonstration GuideLuis PerdomoNo ratings yet

- Digital Oscilloscope With FPGADocument36 pagesDigital Oscilloscope With FPGAAhmed YasserNo ratings yet

- Design of Branchline Coupler PDFDocument4 pagesDesign of Branchline Coupler PDFSudharshan BabuNo ratings yet

- Mentorpaper ADCDocument3 pagesMentorpaper ADCredbookmanNo ratings yet

- April 21 LabProject - PG2023Document5 pagesApril 21 LabProject - PG2023RustyNo ratings yet

- Pipeline Adc Thesis PDFDocument7 pagesPipeline Adc Thesis PDFlauratorrestucson100% (2)

- Assignment MANIFOLD FinalDocument17 pagesAssignment MANIFOLD FinalMohamed SaeedNo ratings yet

- Experiment # 3 Amplitude Modulation and Demodulation: 1 PurposeDocument9 pagesExperiment # 3 Amplitude Modulation and Demodulation: 1 PurposeGeorgeNo ratings yet

- EE477L-Final Project Phase 3Document3 pagesEE477L-Final Project Phase 3Amandeep VaishNo ratings yet

- Ee382M - Vlsi I: Spring 2009 (Prof. David Pan) Final ProjectDocument13 pagesEe382M - Vlsi I: Spring 2009 (Prof. David Pan) Final ProjectsepritaharaNo ratings yet

- VLSI Project DescriptionDocument4 pagesVLSI Project DescriptionKishoreNo ratings yet

- Assignment 3Document1 pageAssignment 3Aayush ShrivastavaNo ratings yet

- Signal Intagrity Simulation of PCIE PDFDocument5 pagesSignal Intagrity Simulation of PCIE PDFvijithacvijayanNo ratings yet

- Op Amp Design ThesisDocument5 pagesOp Amp Design Thesismaryburgsiouxfalls100% (2)

- Vlsi Interview QuestionsDocument26 pagesVlsi Interview Questionschintu333No ratings yet

- 6.012 ST13 Design ProjectDocument5 pages6.012 ST13 Design Projectarthur5689791No ratings yet

- Lab 1 Introduction and Top-SPICE DemoDocument10 pagesLab 1 Introduction and Top-SPICE Demochrisdp23No ratings yet

- Practical Guide To High Speed PCB Layout by by John ArdizzoniDocument6 pagesPractical Guide To High Speed PCB Layout by by John ArdizzoniblekstenaNo ratings yet

- Analog: Section 5: Design PracticesDocument56 pagesAnalog: Section 5: Design PracticesBianca CopelandNo ratings yet

- MoveInSync Native Android Mobile AppDocument12 pagesMoveInSync Native Android Mobile AppRismaNo ratings yet

- Entrepreneurial BehaviourDocument16 pagesEntrepreneurial Behaviournonalyn tomboconNo ratings yet

- Project Report: MES Dental College and HospitalDocument28 pagesProject Report: MES Dental College and HospitalAnurtha AnuNo ratings yet

- Heat ExchangerDocument5 pagesHeat Exchangersara smithNo ratings yet

- Restrictions AOP30 enDocument1 pageRestrictions AOP30 enRicardo RamirezNo ratings yet

- Waste Heat BoilerDocument7 pagesWaste Heat Boilerabdul karimNo ratings yet

- Kelompok CKD - Tugas Terapi Modalitas KeperawatanDocument14 pagesKelompok CKD - Tugas Terapi Modalitas KeperawatanWinda WidyaNo ratings yet

- Comparison of Plate Count Agar and R2A Medium For Enumeration of Heterotrophic Bacteria in Natural Mineral WaterDocument4 pagesComparison of Plate Count Agar and R2A Medium For Enumeration of Heterotrophic Bacteria in Natural Mineral WaterSurendar KesavanNo ratings yet

- Description: Super Thoroseal Is A Blend of PortlandDocument2 pagesDescription: Super Thoroseal Is A Blend of Portlandqwerty_conan100% (1)

- Cutting Aws C5.3 2000 R2011Document33 pagesCutting Aws C5.3 2000 R2011Serkan AkşanlıNo ratings yet

- DPL MDDocument3 pagesDPL MDCoy IngramNo ratings yet

- Interplater 85/125P HDX: Setting New Processing Standards For High-End UsersDocument2 pagesInterplater 85/125P HDX: Setting New Processing Standards For High-End Usershackko24No ratings yet

- Configuration Diagrams: Group 80ADocument24 pagesConfiguration Diagrams: Group 80ASaHdo AbdelHamid100% (1)

- GS Ep Tec 260 enDocument61 pagesGS Ep Tec 260 enCesarNo ratings yet

- Biogas Technology Suppliers Directory 2018: Internati NalDocument6 pagesBiogas Technology Suppliers Directory 2018: Internati NalRazvan PetricaNo ratings yet

- El Nido RW 33 Headwind 1120 + CLWDocument2 pagesEl Nido RW 33 Headwind 1120 + CLWRanny LomibaoNo ratings yet

- AutoCAD 2006 Installing Network License Manager0Document12 pagesAutoCAD 2006 Installing Network License Manager0gurugovindanNo ratings yet

- 翻译件 2021 The - Early - Life - of - Marx's - "Mode - 【彩云小译】Document61 pages翻译件 2021 The - Early - Life - of - Marx's - "Mode - 【彩云小译】James BNo ratings yet

- Cloudworx Pdms UsDocument2 pagesCloudworx Pdms Usguru4lifegmailcomNo ratings yet

- Metascope An/Pas-6 (5855-790-6197) : Technical ManualDocument38 pagesMetascope An/Pas-6 (5855-790-6197) : Technical ManualDens VillaNo ratings yet

- Understanding ISO 9001 Calibration RequirementsDocument6 pagesUnderstanding ISO 9001 Calibration RequirementsAldrin HernandezNo ratings yet

- (Fanuc Lad 0I-Mc) Ladder Diagram 1Document160 pages(Fanuc Lad 0I-Mc) Ladder Diagram 1Ujang NachrawiNo ratings yet

- 65° Panel Antenna: General SpecificationsDocument2 pages65° Panel Antenna: General SpecificationsAnnBliss100% (2)

- Detail Project Report: (Heidelberg Cement Group)Document42 pagesDetail Project Report: (Heidelberg Cement Group)saravananNo ratings yet

- Mahmoud Darwish TMADocument15 pagesMahmoud Darwish TMABassant Ayman Ahmed Abdil Alim100% (1)

- En 10143-1993Document7 pagesEn 10143-1993Eduardo TeixeiraNo ratings yet

- PSY502 OLd PapersDocument6 pagesPSY502 OLd Paperscs619finalproject.com100% (4)

- COCapplication08rev Working SampleDocument34 pagesCOCapplication08rev Working SampleTanya HerreraNo ratings yet

- SIP Project ProposalDocument2 pagesSIP Project ProposalDeep SutariaNo ratings yet

- FC Exercises3Document16 pagesFC Exercises3Supertj666No ratings yet