Professional Documents

Culture Documents

Analysis and Design of A Multiple Feedback Loop Control Strategy For Single Phase Voltage Source UPS Inverters

Uploaded by

FelipeFalconiOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Analysis and Design of A Multiple Feedback Loop Control Strategy For Single Phase Voltage Source UPS Inverters

Uploaded by

FelipeFalconiCopyright:

Available Formats

532

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 11, NO. 4, JULY 1996

Analysis and Design of a Multiple Feedback Loop Control Strategy for Single-phase Voltage- Source TJPS Inverters

Naser M. Abdel-Rahim, Student Member, IEEE, and John E. Quaicoe, Senior Member, IEEE

Abstract- This paper presents the analysis and design of a multiple feedback loop control scheme for single-phase voltagesource uninterruptihle power supply (UPS) inverters with an L-C filter. The control scheme is based on sensing the current in the capacitor of the load filter and using it in an inner feedback loop. An outer voltage feedback loop is also incorporated to ensure that the load voltage is sinusoidal and well regulated. A general statespace averaged model of the UPS system is first derived and used to establish the steady-steady quiescent point. A linearized small signal dynamic model is then developed from the system general model using perturbation and small-signal approximation. The linearized system model is employed to examine the incremental dynamics of the power circuit and select appropriate feedback variables for stable operation of the closed-loop UPS system. Experimental verification of a laboratory model of the UPS system under the proposed closed-loop operation is provided for both linear and nonlinear loads. It is shown that the control scheme offers improved performance measures over existing schemes. It is simple to implement and capable of producing nearly perfect sinusoidal load voltage waveform at moderate switching frequency and reasonable size of filter parameters. Furthermore, the scheme has excellent dynamic response and high voltage utilization of the dc source.

To overcome this drawback, a real-time feedback control scheme using dead-beat control was proposed [ 5 ] , [ ] This 6. technique employs the capacitor voltage and its derivative in a control algorithm to calculate the duration of the ON/OFF states of the inverter switching devices such that the capacitor voltage is exactly equal to the reference voltage at the next sampling time. Although this technique has been successfully implemented for single- and three-phase applications, it has the following drawbacks: 1) it is complex to implement; 2) it is sensitive to parameter variations; and 3) its control algorithm requires the estimation of the load parameters [7]. In order to achieve a control scheme that overcomes the above disadvantages, a current regulated control scheme for dc/ac applications was proposed in [8]. In this technique, the current in the filter capacitor is used as the feedback variable in a two-switch inverter circuit topology to achieve a sinusoidal capacitor current. An outer voltage control loop is also incorporated for load voltage regulation and compensation for imperfections in the implementation of the current control loop. Although the technique results in a sinusoidal capacitor I. INTRODUCTION current, the power circuit configuration and the switching NINTERRUPTIBLE POWER supplies (UPSS) are used scheme used to implement the technique produce a load to interface critical loads such as computers and commu- voltage that is sinusoidal with dc offset. For UPS applications, nication systems to the utility system. The output voltage of the the presence of the dc voltage offset is unacceptable. UPS inverter is required to be sinusoidal with minimum total This paper investigates the suitability of a current-regulated harmonic distortion. This is usually achieved by employing a voltage-controlled strategy for a single-phase voltage-source combination of pulse-width modulation (PWM) scheme and a half-bridge inverter with a second-order filter. The scheme second-order filter at the output of the inverter. incorporates an inner capacitor current loop, an outer capacitor One way of achieving a clean sinusoidal load voltage is by voltage loop, a fixed switching frequency, and variable duty using a sine pulse width modulation (SPWM) scheme [ 1J, [2]. cycle approach to produce sinusoidal output voltage with In this technique, the load voltage is compared with a reference minimum harmonic distortion. The fixed switching frequency sinusoidal voltage waveform and the difference in amplitude approach produces a defined frequency spectrum at the inverter is used to control the modulating signal in the control circuit output, which makes it easier to design an electromagnetic of the power inverter. A more advanced technique employs interference filter to prevent interference with communication a programmed optimum PWM scheme that is based on the circuits. harmonic elimination technique [ 3 ] ,[4]. These schemes have The paper is organized as follows: Section I1 provides been shown to perform well with linear loads. However, with the steady-state performance of the UPS system under opennonlinear loads the PWM scheme does not guarantee low loop control. A procedure for selecting appropriate feedback distortion of the load voltage. variables that result in a stable operation of the closedloop system is provided in Section 111. The proposed control Manuscript received July 1, 1994; revised February 19, 1996. This work was supported in part by the Natural Sciences and Engineering Research strategy is proposed in Section IV. Section V presents a Council (NSERC). design procedure for selecting the gains of the inner and outer The authors are with the Faculty of Engineering and Applied Science, feedback loops. The control block of the proposed control Memorial University of Newfoundland, St. Johns A l B 3x5,Canada. Publisher ltem Identifier S 0885-8993(96)05164-2. strategy, its principle of operation, computer simulation, and

0885-8993/96$05,00 0 1996 IEEE

ABDEL-RAHIM AND QUAICOE: ANALYSIS AND DESIGN OF A MULTIPLE FEEDBACK LOOP CONTROL STRATEGY

533

Fig. 1. The single-phase half-bridge UPS inverter.

experimental verification are presented in Section VI. Finally, conclusions are drawn in Section VII.

time-dependent duty cycle dl ( t ) [9], as

11. ANALYTICAL MODEL OF THE OPEN-LOOP

SYSTEM: STEADY -STATEPERFORMANCE

Fig. 1 shows the circuit diagram of the single-phase halfbridge voltage-source UPS inverter. It consists of a load filter ( L f and C f ) and an R-L load. The system differential equations can be written in statespace form as

where V, is the amplitude of the carrier waveform. For a modulating signal given by

vm(t)= V, sin(w,t)

(3)

-3

-

-1

the system state-space averaged continuous equation can be obtained by substituting the discontinuous switching function, S;,in (1) by its average value in ( 2 ) and (3). The resultant system equation is obtained as

d dt

Lf

Zl(t)

0

-

?

L1 0

-3 0

dt

=

_-1

Lf

- Cf

- Cf

0 1

C f

-1 L1

R 1

?

L1

[?!:; ]

vc(t)

(4)

where S; = 1 when SIis ON and Sf= 0 when SIis OFF. Equation (1) is discontinuous due to the presence of the switching function S . One way of studying the system T performance and characterizing its behavior is to solve (1) numerically and simulate the system behavior at various operating points and system parameters. This method has the disadvantage of being computationally intensive and provides little insight into the operation of the system. On the other hand, an averaged time-continuous model of the UPS system can be obtained for (1) by assuming that the inverter switching frequency, f s , is much higher than the , frequency of the modulating signal, v ( t ) .Consequently, the discontinuous switching function Sf can be replaced by its

M=-.

V,

v,

(5)

The first row of (4) indicates that the averaging process replaces the effect of the inverter switching function with a controllable sinusoidal voltage source of magnitude M V&.It should be noted that (4) is valid only through the linear range of operation, i.e., M 5 1.0. Assuming that the resistance associated with the filter inductor is negligibly small, the equivalent circuit of the averaged UPS system is as shown in Fig. 2.

534

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 11, NO. 4, JULY 1996

Ynn

Fig. 2.

Equivalent circuit of the averaged UPS system.

The system steady-state variables are obtained from Fig 2. using the following phasor analysis

v)

2000 . . . . .

. . . . .

.- 1000. . . . . . . . . . . . . . . . . .: . . . . . . . . . . ! . . . . . . X 0 .................a.. .............; .......

E -1000.

-3000

. . . . . . . . . . . . . . . . :.. . . . . . . . . . :.. . . ...

-2000,. . . . . . . . . . . . . . . . . .

and

(9)

where is the p h a s y reyresytati2n of the modulating signal M sin(w,t) andl,, , V, , I,, . I,, are the steady-state , variables of the inverter output current, capacitor voltage and current, and load current at the modulating signal frequency, U,, respectively

+

n ?

9nM

L" ""

E U z

,,-, inML

I .

l ' 0

I

1

ZL,

- XLmXcfm

+ XZfm(Xcfm R +J ( X I , l

-

-&L)

+ I&

-

(XZfm & f m ) (10)

Xcfm)

rT

-

XI,

- X c f m - 3R1Xcfm

2000 . . . . . .

Equations (6)-(9) give the system steady-state variables in terms of the load parameters and filter components and represent the steady-state quiescent operating point of the system.

; . . . . . . ..: . . . . . . . . . . ;. . . . .

s

v)

1000 . . . . . . .! . . . . . .

....... j . .

................

o,

0 ..........................................

...

....................

I . . .....

g -1000

-3000

111. STABILITY ANALYSIS THE UPS SYSTEM OF

In order to ensure that the UPS system will produce the nominal load voltage, irrespective of disturbances such as variations in the input supply voltage, perturbations in the switching times, and the load, a real-time feedback control scheme is proposed. However, to successfully implement the real-time feedback control scheme, the power circuit incremental dynamics are examined with a view to selecting the appropriate feedback variables. It is assumed that the incremental variation in the control signal is much slower

- 2 m . . . . . . .' ............ .:. . . . . . . . . . .

Fig. 3 . Locus of the roots of the power circuit incremental dynamics for a load impedance of 10 R at 0.7 power factor lagging loads, L f = 5.0 mH. C f = 100 pF, and Vd, = 100.0 V.

than the bandwidth of the control loop. Hence, a quasistatic approach is used to carry out the investigation [lo], [ l l ]

ABDEL-RAHIM AND QUAICOE: ANALYSIS AND DESIGN OF A MULTIPLE FEEDBACK LOOP CONTROL STRATEGY

535

The system equation given by ( ) though time contin4, uous, is nonlinear. The nonlinearity arises from the terms (q( t ) / l l ( t ) ) &t ) ( uc(t)/ll( t ) , and m(t)vd,(t). In order to ( , ) develop a dynamic model of the UPS system, the system equations are first linearized around a nominal steady-state operating point. This is carried out using perturbation technique and small-signal approximation. The resulting small-signal dynamic model can be written as

capacitor current is, chosen as the feedback variable for the closed-loop operation of the UPS system. Although choosing the capacitor current as the feedback variable results in a stable operation of the closed loop UPS system and ensureis sinusoidal capacitor current, it does not guarantee sinusoidal capacitor (load) voltage, especially when the inverter output voltage is nonsinusoidal (i.e., PWM). Therefore, in order to achieve sinusoidal capacitor voltage and current, an outer capacitor voltage feedback loop is also used. IV. THE PROPOSED UPS CONTROL SYSTEM

The resultant configuration of the proposed control scheme offers many advantages for UPS system applications. The inner current loop] provides an inherent peak current limit in the power circuit, especially during "cold" start of the system. In addition, since the capacitor current represents the rate of change of the load voltage, the control scheme is (12) capable of predicting and correcting near-future variations in the load voltage and thus providing a fast dynamic response. Gc, 5, indicate incremental changes in the inverter Furthermore, the outer voltage loop regulates the load voltage output current, capacitor voltage, and current, resp_ectively,as and produces a stiff ac voltage supply as well as ensures a a result of incremental changes in the duty cycle, d and hence sinusoidal load voltage within the acceptable total harmonic the modulation index, f i [see (2)].Equation (12) shows that distortion (THD). the location of the system poles is dependent on the input Fig. 4 shows the UPS system with an inner current loop and dc voltage ( V d c ) , the system parameters ( L l ,Rl, L f and C f ) , an outer voltage loop. The error signal e ( t ) is obtained from and the incremental change in the modulation index, 6 or 1 successive comparison of the capacitor voltage and current implicitly, the duty cycle, 2. with their respective reference signals. The inverter switching Fig. 3(a) shows the locus of the roots of the incremental pattern is then obtained from a comparison of e ( t ) and a fixed dependence of the capacitor voltage due to 10% incremental high-frequency (4.0 kHz) triangular waveform. The resultant change in the modulation index 7 j i . The figure shows that switching pattern, which has a fixed switching frequency with employing the capacitor voltage as the feedback variable variable duty cycle, produces a sinusoidal load voltage with makes the system dominant poles move along the imaginary low harmonic content. axis of the s-plane. The figure also shows that the location of the system poles are not only dependent on the system v. I~NALYSISAND DESIGNOF THE parameters, but they are also time varying. For the circuit FE~EDBACK CONTROL SCHEME parameters given in Fig. 3, it can be seen that the frequency of the dominant poles can be as high as 4530 radls. This has In order to achieve a UPS system with fast dynamic the effect of producing high-frequency oscillations in the load response and small steady-state error between the load voltage voltage. Such behavior is not acceptable for UPS applications. and its reference waveform, both regulators of the feedback As a result, the capacitor voltage cannot be employed as the loop have to be carefully designed. The open-loop transfer feedback variable for the closed-loop operation of the UPS function of the inner current loop, G,,(s), is obtained from system. the third row of (12) as Fig. 3(b) shows that closing the loop around the inverter output current makes the system poles move farther into the left half of the s-plane, resulting in stable closed-loop operation of the UPS system. However, in order to generate s s the reference waveform for the feedback control of the inverter output current, the instantaneous value of the load current must be known. This will require an additional current sensor. From the point of view of cost, this control scheme is not attractive. 3) Fig. 3(c) shows the locus of the roots of the incremental dependence of the capacitor current due to incremental changes Fig. 5 shows thle Bode plot of the inner current loop for in the modulation index. The figure shows that closing the various load conditions. The figure shows that the inner loop around the capacitor current results in moving the system current loop exhibits a band-pass filter-like characteristics. poles farther into the left half of the s-plane. This has the effect The figure also shows that the bandwidth of the inner current of providing active damping to any oscillation that may take loop is not affected by the load variations. It can be seen place in the power circuit. Consequently, a stable operation from the figure that the loop possesses a phase margin of of the closed-loop control scheme is achieved. Therefore, the 270' and 90" and a theoretical gain margin of infinity.

i+

536

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 11, NO. 4, JULY 1996

Fig. 4. The proposed control scheme of the single-phase UPS inverter.

4

-50

50

1oo

10'

1 o2

Frequency in rad/sec

1o3

1' 0

1os

1o6

Frequency in rad/sec

Fig. 5 .

Bode diagram of the open-loop transfer function of the inner current loop of the UPS system: L f = 5.0 mH. C f = 100.0 pF, and

2 = 8.8 fl,Vijc = 100.0 V. 1

The closed-loop transfer function of the inner current loop for unity and 0.7 power factor lagging loads is shown in Fig. 6. The figure shows that the loop possesses a relatively narrow bandwidth with a significant phase error in both cases. The loop bandwidth can be widened by employing proportional controller in the feed-forward path of the inner current loop. However, to avoid excessive gain in the inner current loop and produce a system that is immune to switching noise, kpc is chosen such that the gain of the closed-loop transfer

(5.)

function of the inner current loop exhibits near-unity gain from w G 200 radls up to half the inverter switching frequency (i.e., w G 12 500 rad/s). And, since the bandwidth of the inner current loop is slightly wider for 0.7 power factor lagging loads (see Fig. 6), the choice of k,, is carried out for this condition (i.e., worst-case scenario). It can be shown that for kpc = 2.0, the gain of the closed-loop transfer function is 0.94 at w = 12500 rad/s. The Bode diagram of the closed-loop transfer function of the inner current loop with kpc = 2.0 is shown in Fig. 7. The figure also shows that the loop

ABDEL-RAHIM AND QUAICOE: ANALYSIS AND DESIGN OF A MULTIPLE FEEDBACK LOOP CONTROL STRATEGY

531

.Frequency in radlsec

10'

1OB

1oo

1ciz 10' Frequency in rawsec

1o6

Frequency in rad/sec

Frequency in radsec

Fig. 6. Bode diagram of the closed-loop transfer function of the inner current loop of the UPS system ( I C p c = 1.0): L f = 5.0 mH, Cf = 100.0 p F , and 2 = 8.8 Q,&, = 100.0 V. 1

m

U

.z

.-

-20

d

10' 10 ' 1o3

Frequency in rad'sec

lOOL

U)

I0 '

1os

1o6

...................................... py;;;;;;;. . . . . . . . . .

..... i i;;;;;;; 1 ::;;;;;; 1;;;;:;; ; . . . . . .. .. .. . . . . . . .. . . . . . . . .. .. .. .. .. .. .. .. . . . . .. .. .. .. .. .. .. ... ... ... ... ... ....... .. .. .. .. . . . . , . . .. . . .

. . . . . . . . .

' .

10'

I' O

1o6

Frequeq-in rad'sec

Fig. 7. Bode diagram of' the closed-loop transfer function of the inner current loop of the UPS system with k,, = 2.0. L f = 5.0 mH; Cf = 100.0 p F , and 2 = 8.8 f l at 0.7 power factor lagging, v d c = 100.0 V. 1

bandwidth has been increased and the error in the phase over the frequency range of interest (w E 200 to 12500 rad/s) has been reduced. The small-signal open-loop transfer function of the outervoltage feedback loop is obtained in terms of the open-loop

transfer function of the inner current loop as

1 kpcGic(s) G,c(s) = .Cf 1 k,cGi,(s)

538

IEEE TMNSACTIONS ON POWER ELECTRONICS, VOL. 11, NO. 4, JULY 1996

50

-50

1oa

10'

1o2

1oJ

10'

1os

1OB

Frequency in radsec

\

......... . . . .. .. . . . . . .. ...... .. .. ....... .. . . . . . . . . .. . .

.........

I n m

a

1oo

i

10 '

1' 0 1o* Frequency i rad'sec n

10'

1oe

Fig. 8. Bode diagram of the open-loop transfer function of the outer-voltage loop of the UPS system with k p c = 2.0, L f = 5.0 mH, Cf = 100.0 pF, and 2 = 8.8 n,Vdc = 100.0 V. 1

w

1

I

I

1.5

25 .

3

kPV

3.5

4.5

0.1 1

'

1.5

2.5

3

kPv

3.5

4.5

I 5

Fig. 9. Error in the magnitude and phase of the capacitor voltage with respect to its reference waveform with IC,, and 2 = 8.8 Cl,,l<iL = 100.0 V. 1

= 2.0. L f = 5.0 mH, C f = 100.0 pF.

where G,,(s) is given by (13). The Bode plot of G,,.,(s) is shown in Fig 8. The figure shows that the loop has a phase margin of 74.5" and a gain margin of 87.1 dB. In order to reduce the steady-state error between the capacitor voltage and its reference waveform, a proportional-plusintegral (PI) controller may be used in the feed-forward path

of the outer capacitor voltage feedback loop. However, since the capacitor voltage is sinusoidally varying, a PI controller will introduce phase errors and deteriorate the effectiveness of the control scheme. Consequently, a proportional controller, k p u , is employed in the outer voltage loop. It can be seen from Fig. 8 that using a proportional controller of high gain

ABDEL-RAHIM AND QUAICOE: ANALYSIS AND DESIGN OF A MULTIPLE FEEDBACK LOOP CONTROL STRATEGY

539

TABLE I

THD

OF THE

LOAD VOLTAGE

AS THE

LOAD AND FILTER PARAMETERS CHANCE

TABLE I1 THD OF THE FILTER c:APACITOR VOLTAGE WITH A BRIDGE RECTIFIER AS 120AD ( v d c = 100.0 v, Xlfm = 0.15 pU) THE NONLINEAR

Z,=lO.O R (1.0 pu) at lagging power factor of

0.6

0.7 power factor lagging load with Zi

4.0 pu

R in pu d

1.0

X,f,,=0.88 PU THD '% X,fm=0.fi6 PU THD '% X,fm=0.53 PU THD '%

0.8

1.0

1 2.0 pu 1

0.42

1.33 pu

2.0

3.0

4.0

Xlf,=0.18 pu X,/,=2.50 pu

THD %

X+&=O.l pu X,fm=3.0 pu THD % X,,,=O.l pu X,f7,,=5.0 pu

0.44

0.41

0.40

0.40

0.41

5.22 3.48 4.62 4.07 2.99

2.78 2.22 2.41 1.96 1.76

4.71

3.52

2.19

3.62

3.46

3.28

2.53 2.01

THD

7 %

11.16

12.23

5.14

12.32

10.71

11.93

Trig

OV

CH 1

To inverter switches

Fig. 10. The proposed UPS with a bridge rectifier as the nonlinear load (Cd = 2500 pF, Rd = 20.0 n).

value shifts the system cross-over frequency to a higher value, thus reducing the available gain and phase margin of the outer voltage loop. Hence, the value of k,, is chosen such that the steady-state error between the capacitor voltage and its reference waveform is within an acceptable value (chosen to be less than 2%). Fig. 9 shows the effect of kp, on the steady-state error between the capacitor voltage and its reference waveform for the closed-loop operation of the UPS system (shown in Fig. 4). The figure shows that the error decreases with increasing values of IC,, and for k,, 2 2.75, the error is less than 2.0%. Thus, ICp, is chosen as 2.75. The performance of the proposed UPS system was investigated by simulating its behavior at various loading conditions. The input capacitor voltage of 100 V is chosen as 1.0 pu, while the load impedance of magnitude 10 s1 is chosen the base value for impedances. Table I shows the effect of changing the magnitude and phase angle of the load on the THD of the load voltage for various values of filter series inductive reactance, X l f m l and The table shows that filter shunt capacitive reactance, X,,,. for Xlf, = 0.18 pu and X,f, = 2.5 the THD of the load voltage is very small. Also, it can be shown that the filter ratingkost for these values is minimum. The performance of the proposed control scheme under nonlinear load conditions was also investigated. The nonlinear load was chosen as a bridge rectifier with an output dc filter, Cd, and a resistive load as shown in Fig. 10.

50V

system.

20mV

5ms

Fig. 11. Experimental results of the transient response of the proposed UPS

Trig

5V

CH 1

50V

50mV

5ms

SAVE

Fig. 12. Experimental results of the steady-state response of the proposed UPS system.

Table I1 shows the effect of varying the load resistance on the THD of the load voltage for various values of X,fm. The table shows that with larger filter capacitor a load voltage within the acceptabllc THD can be obtained at adverse loading conditions.

540

IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 11, NO. 4, JULY 1996

Trig

65mV

CH2

VERT

:V

5ms

SAVE

Fig. 14. Experimental results of the proposed UPS system feeding a full-bridge rectifier with an R-L load.

5ov

5OmV (b)

5mr

Fig. 13. Experimental results of the dynamic response of the proposed UPS system for a 100% step change in the load: (a) 100% application of the load and (b) 100% removal of the load.

The figure shows that the system exhibits very fast dynamic response with excellent load voltage regulation from no-load to full-load and with very little change in the load voltage at the point of applying the full load, indicating that the control scheme ensures a stiff load voltage. The system performance with nonlinear loads is shown in Fig. 14. The nonlinear load was chosen as a full-bridge rectifier feeding an R-L load (R = 20.0 R and L = 16.0 mH). The load current was recorded by observing the voltage drop attenuation oscilloscope across the load resistance using probe. Figs. 12-14 show that the proposed control scheme is capable of supplying both linear and nonlinear loads with excellent voltage regulation and minimum distortion in the load voltage.

&

VI. EXPERIMENTAL RESULTS A prototype experimental module of the proposed UPS (Fig. 4) was built to verify the operation of the control strategy. Both the actual capacitor voltage and current in the power circuit were sensed, filtered, and used as the control variables. Fig. 11 shows the transient response from cold start to full load of the proposed UPS system. The upper trace shows the capacitor voltage and the lower trace shows the capacitor current. The capacitor current was recorded by observing the voltage drop across a current shunt of 10.0 mR resistance. The figure shows that the system takes about a quarter cycle to reach the steady-state values of the capacitor voltage and current. The steady-state load voltage and current waveforms of the UPS system are depicted in Fig. 12. The figure shows that the control strategy is capable of producing a nearly perfect sinusoidal load voltage at moderate switching frequency. The total harmonic distortion of the capacitor (load) voltage was measured as 2%. Fig. 13 shows the dynamic response of the UPS system for 100% step change in the load from no load to full load.

VII. CONCLUSION

A multiple feedback loop control strategy for a single-phase voltage-source UPS system has been described in the paper. The system performance under open-loop control strategy was first studied to obtain the steady state performance of the UPS system. The power circuit incremental dynamics was then investigated to assess the system stability and select appropriate feedback variables for the closed-loop control of the system. The stability analysis showed that a feedback control system with an inner capacitor current control loop and an outer capacitor voltage feedback loop results in a successful operation of the UPS system. The proposed control strategy offers many features that are attractive for UPS applications. In addition to the basic features of most feedback control systems, such as insensitivity to parameter variations and robustness, the scheme is capable of producing nearly perfect sinusoidal load voltage at any load power factor with excellent load voltage regulation. The scheme also possesses very fast dynamic response and lends itself to both linear and nonlinear load applications.

ABDEL-RAHIM AND QUAICOE. ANALYSIS AND DESIGN OF A MULTIPLE FEEDBACK LOOP CONTROL STRATEGY

541

REFERENCES

111 P. D. Ziogas, Optimum voltage and harmonic control PWM techniques

for three-phase static UPS inverters, IEEE Truns. Ind. Applicat., vol. IA-16, no. 4, pp. 542-546, July/Aug 1980. P. D. Ziogas, S. Manias, and E. P. Wiechman, Applications of current source inverters in UPS systems, IEEE Trans. Ind. Applicut., vol. 25, no. 3, pp. 408418, May/June 1989. M. Boost and P. D. Ziogas, State of the art PWM techniques: A critical evaluation IEEE Trans. Ind. Applicat., vol. 24, pp. 271-280, Mar./Apr. 1988. P. Enjeti, J. F. Lindsay, P. D. Ziogas, and M. H. Rashid, New current control scheme for PWM inverters, Prvc. IEE, vol. 135, pt. B., no. 4, July 1988. A. Kawamura, T. Haneyoshi, and R. G. Hoft, Dead beat controlled PWM inverter with parameter estimation using only voltage sensor, in IEEE Power Electronics Specialists Cvn$ (PESC), 1986, pp. 576-583. A. Kawamura and K. Ishihara, High-frequency deadbeat control of three-phase PWM inverte used for uninterruptible power supply, in IEEE Power Electronics Specialists Con$ (PESCJ,Koyoto, Japan, Apr. 1988, pp. 644649. A. Kawamura and T. Yokoyama, Comparison of five different approaches for real-time digital feedback control of PWM inverters, in IEEEInd. Appl. Soc. Ann. Meet., Seattle, WA, Oct. 1990, pp. 1005-1011. N. R. Zargari, P. D. Ziogas, and G. Joos, A two switch high performance current regulated DC/AC converter module, in Proc. IEEE Industry Applicutivns Society Ann. Meet., 1990, pp. 929-934. R. Wu, S. B. Dewan, and G. R. Slemon, Analysis of an ac-todc Voltage-Source Converter Using PWM With Phase and Amplitude Control, IEEE Trans. Ind. Applicat., vol. 27, pp. 355-364, Mar./Apr. 1991. M. F. Schlect, A line interfaced inverter with active control of the output current waveform, in Power Electronics Specialists Con$ (PESC), 1980, pp. 234-241. C. Hsu Stability analysis of a switched mode inverter using Cuk converter, in IEEE Power Electronics Specialists Conf (PESCJ,Taipie, Taiwan, June 1994, pp. 785-795.

PI

131 141

Naser M. Ahdel-Rahim (S87) was born in Cairo, Egypt. He received the BSc. Eng (Hons.) degree in electrical engineering from Zagazig University, Shoubra, Egypt in 1984, and the M.Eng. and Ph.D. degrees from Memorial University of Newfoundland, St. Johns, Canada, in 1989 and 1995, respectively. From 1984 to 1986 he worked as an Associate Lecturer at Zagazig University, where he is currently an Assistant Professor in electrical engineering. His current research interests are in the area of modulation and contr 01 of inverters for uninterruptible power supplies and utility interface applicaltions.

John E. Quaicoe (S7S-M76-SM93) was born in

Tarkwa, Ghana. He received the B.Sc. (Eng.) degree from the University of Science and Technology, Kumasi, Ghana in 1973, and the M.A.Sc. and Ph.D. degrees from the University of Toronto, Canada, in 1977 and 1982, respectively. From 1973 to 1974 he worked as an Assistant Lecturer at the University of Science and Technology, where he was responsible for the development of a number of undergraduate laboratories. After working as a Postdoctoral Fellow at the University of Toronto for a short time, he joined Memorial University of Newfoundland, where he is presently the Chairman of the Electrical Engineering Department. His research interests are in the area of static power converters and motor drives. Dr. Quaicoe is a member of the Association of Professional Engineers and Geoscientists of Newfoundland.

171 [81 191

[IO]

[ll]

You might also like

- Gobind KSR Conf PaperDocument7 pagesGobind KSR Conf PaperRagul DuraisamyNo ratings yet

- On FACTSDocument33 pagesOn FACTSAravind Babu100% (1)

- Modeling and Simulation of A Three-Phase Inverter With Rectifier-Type Nonlinear LoadsDocument10 pagesModeling and Simulation of A Three-Phase Inverter With Rectifier-Type Nonlinear LoadsTuấn DũngNo ratings yet

- Uninterruptible Power Supply Multiloop Control Employing Digital Predictive Voltage and Current RegulatorsDocument9 pagesUninterruptible Power Supply Multiloop Control Employing Digital Predictive Voltage and Current RegulatorsPhạm Văn TưởngNo ratings yet

- Analysis and Design of A Multiple Feedback Loop Control Strategy For Single-Phase Voltage-Source UPS InvertersDocument10 pagesAnalysis and Design of A Multiple Feedback Loop Control Strategy For Single-Phase Voltage-Source UPS InvertersMary NdhlovuNo ratings yet

- PSSEDocument6 pagesPSSESyed Faizan AliNo ratings yet

- Power Flow Analysis of Power System Embedded With Upfc Using Psasp ProgramDocument5 pagesPower Flow Analysis of Power System Embedded With Upfc Using Psasp ProgramMahesh ShirsatNo ratings yet

- Simulation of Upqc FileDocument11 pagesSimulation of Upqc FiledineshprocksNo ratings yet

- Power Quality Impacts of An Electric Arc Furnace and Its CompensationDocument8 pagesPower Quality Impacts of An Electric Arc Furnace and Its CompensationPudhur Kannan ManiNo ratings yet

- 2011 - Control of A DCDC Converter by Fuzzy Controller For A Solar Pumping System - Paper N. Mazouz, A. MidounDocument8 pages2011 - Control of A DCDC Converter by Fuzzy Controller For A Solar Pumping System - Paper N. Mazouz, A. MidounBoruziaNo ratings yet

- Wcecs2009 - pp545-549 Computer LoadsDocument5 pagesWcecs2009 - pp545-549 Computer LoadsYogesh MsdNo ratings yet

- A Voltage-Mode PWM Buck Regulator With End-Point PredictionDocument5 pagesA Voltage-Mode PWM Buck Regulator With End-Point PredictionWen DwenNo ratings yet

- Distinctive Study of UPFC and Fault Analysis Under Simulated EnvironmentDocument5 pagesDistinctive Study of UPFC and Fault Analysis Under Simulated EnvironmentXahid YousafNo ratings yet

- Simulation Modelling Practice and Theory: Yuanjie Rong, Chunwen Li, Qingqing DingDocument12 pagesSimulation Modelling Practice and Theory: Yuanjie Rong, Chunwen Li, Qingqing DingMelissa MillerNo ratings yet

- Jerald in e 2012Document5 pagesJerald in e 2012Amir AramNo ratings yet

- A New ISPWM Switching Technique For THD Reduction in Custom Power DevicesDocument7 pagesA New ISPWM Switching Technique For THD Reduction in Custom Power DevicesBharathkumars89No ratings yet

- Complex Vector Control of A Unified Power Flow ControllerDocument8 pagesComplex Vector Control of A Unified Power Flow ControllerpongpumNo ratings yet

- Filter Design Method For A PWM Feedback Inverter System: C. C. KosmatopoulosDocument9 pagesFilter Design Method For A PWM Feedback Inverter System: C. C. KosmatopoulosSuvra PattanayakNo ratings yet

- Improved Power Quality For Renewable Power Generation Systems Presence of Non-Linear LoadsDocument6 pagesImproved Power Quality For Renewable Power Generation Systems Presence of Non-Linear LoadsPhanikumar Bellam KondaNo ratings yet

- 9609 PDFDocument13 pages9609 PDFnaghamNo ratings yet

- Modeling, Simulation and Control of D-Statcom Using Atp/EmtpDocument4 pagesModeling, Simulation and Control of D-Statcom Using Atp/EmtpKalyan SrinivasNo ratings yet

- Algorithm Allocation: System Security Improvement Differential EvolutionDocument6 pagesAlgorithm Allocation: System Security Improvement Differential EvolutionPiyush AgnihotriNo ratings yet

- Analysis and Design of A Multiple Feedback Loop Control Strategy For 1P Voltage-Source UPS Inverters (IEEE-TPE)Document10 pagesAnalysis and Design of A Multiple Feedback Loop Control Strategy For 1P Voltage-Source UPS Inverters (IEEE-TPE)Al Bajad MamadNo ratings yet

- Applications of Artificial Neural Networks in Power ElectronicsDocument5 pagesApplications of Artificial Neural Networks in Power ElectronicsnarakribNo ratings yet

- Comparison of Three Phase Shunt Active Power Filter Algorithms Under Non-Ideal Mains VoltagesDocument9 pagesComparison of Three Phase Shunt Active Power Filter Algorithms Under Non-Ideal Mains Voltagesiman145No ratings yet

- Upfc PDFDocument5 pagesUpfc PDFHarish KumarNo ratings yet

- Sensitive Load Voltage Compensation Performed by A Suitable Control MethodDocument6 pagesSensitive Load Voltage Compensation Performed by A Suitable Control MethodSanjivee SachinNo ratings yet

- PWM PHA M Inve Ase Hi Erter High Q Ers Fo Qual or ST Lity P Tand-Powe - Alon Er Ge Ne Sin Enera Ingle Ation E - NDocument6 pagesPWM PHA M Inve Ase Hi Erter High Q Ers Fo Qual or ST Lity P Tand-Powe - Alon Er Ge Ne Sin Enera Ingle Ation E - Nron1234567890No ratings yet

- Yamada 2014Document11 pagesYamada 2014Bhargav ReddyNo ratings yet

- An Adaptive Hy Steresis-Band Current Control Technique of A Voltage-Fed PWM Inverter For Machine Drive SystemDocument7 pagesAn Adaptive Hy Steresis-Band Current Control Technique of A Voltage-Fed PWM Inverter For Machine Drive SystemJandfor Tansfg Errott100% (1)

- Phase-Locked Loop For Grid-Connected Three-Phase Power Conversion SystemsDocument7 pagesPhase-Locked Loop For Grid-Connected Three-Phase Power Conversion Systems181084aNo ratings yet

- International Journal of Engineering Research and DevelopmentDocument9 pagesInternational Journal of Engineering Research and DevelopmentIJERDNo ratings yet

- Investigation of Three-Phase Grid-Connected Inverter For Photovoltaic ApplicationDocument6 pagesInvestigation of Three-Phase Grid-Connected Inverter For Photovoltaic ApplicationAmran MaulanaNo ratings yet

- Neural Network Control of Grid-Connected Fuel Cell Plants For Enhancement of Power QualityDocument7 pagesNeural Network Control of Grid-Connected Fuel Cell Plants For Enhancement of Power Qualityashikhmd4467No ratings yet

- Modeling and Dynamic Response Simulation of Gto-Based StatcomDocument4 pagesModeling and Dynamic Response Simulation of Gto-Based StatcomSadaf AnjumNo ratings yet

- Design of Resonant Controller For Four-Leg Matrix Converter Feeding Non Linear LoadsDocument10 pagesDesign of Resonant Controller For Four-Leg Matrix Converter Feeding Non Linear LoadsInternational Organization of Scientific Research (IOSR)No ratings yet

- Dynamic control of FACTS apparatus using linearized VSI modelDocument7 pagesDynamic control of FACTS apparatus using linearized VSI modelVenkat SubramanianNo ratings yet

- Power Quality of Adjustable Speed DriveDocument5 pagesPower Quality of Adjustable Speed DriveAyong HiendroNo ratings yet

- Unbalanced Three-Phase Distribution SystemDocument5 pagesUnbalanced Three-Phase Distribution SystemIraj Az IraniNo ratings yet

- Sumanth 15Document6 pagesSumanth 15Chenchu TnvNo ratings yet

- Master-Slave Sliding Control of Parallel InvertersDocument8 pagesMaster-Slave Sliding Control of Parallel Invertersvirus101No ratings yet

- Use of Upfc For Optimal Power Flow ControlDocument6 pagesUse of Upfc For Optimal Power Flow ControlRaghav Tu Jane NaaNo ratings yet

- PLL For Grid-Connected Three Phase Power ConversisionDocument7 pagesPLL For Grid-Connected Three Phase Power ConversisionNguyễn Quang SángNo ratings yet

- Real and Reactive Power Flow Control With Upfcconnected To A Transmission LineDocument7 pagesReal and Reactive Power Flow Control With Upfcconnected To A Transmission LineSravan GuptaNo ratings yet

- Simulation of D-Q Control System For A Unified Power Flow ControllerDocument10 pagesSimulation of D-Q Control System For A Unified Power Flow ControllerSyed Faizan AliNo ratings yet

- A Novel Method of Power Flow Analysis With UPFC Considering Limit Violations of VariableDocument5 pagesA Novel Method of Power Flow Analysis With UPFC Considering Limit Violations of VariableAmit DebnathNo ratings yet

- Optimizing neutral reactors reduces secondary arc currentsDocument8 pagesOptimizing neutral reactors reduces secondary arc currentsCarlos Lino Rojas AgüeroNo ratings yet

- A Single-Phase UPS System With Series-Parallel Power-Line ConditioningDocument6 pagesA Single-Phase UPS System With Series-Parallel Power-Line ConditioningSelamat Meliala, S.T.,MT Selamat Meliala, S.T.,MTNo ratings yet

- Optimal Control of Three-Phase PWM Inverter For UPS Systems: Keyhani.1@osu - EduDocument6 pagesOptimal Control of Three-Phase PWM Inverter For UPS Systems: Keyhani.1@osu - EdursrtnjNo ratings yet

- 48 Pulse PWMDocument6 pages48 Pulse PWMWilliam JavierNo ratings yet

- Kalman Filter Based Unified Power Quality Conditioner For Output RegulationDocument6 pagesKalman Filter Based Unified Power Quality Conditioner For Output RegulationyeisongarcesNo ratings yet

- Comparing Impact of STATCOM and SSSC On The Performance of Digital Distance RelayDocument7 pagesComparing Impact of STATCOM and SSSC On The Performance of Digital Distance RelayJimmy Alexander BarusNo ratings yet

- Indranil Saaki Paper On UpqcDocument7 pagesIndranil Saaki Paper On UpqcIndra SakiNo ratings yet

- The Use of Facts Devices in Disturbed Power Systems-Modeling, Interface, and Case StudyDocument5 pagesThe Use of Facts Devices in Disturbed Power Systems-Modeling, Interface, and Case StudyNoppon PatNo ratings yet

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetRating: 2 out of 5 stars2/5 (1)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetNo ratings yet

- Some Power Electronics Case Studies Using Matlab Simpowersystem BlocksetFrom EverandSome Power Electronics Case Studies Using Matlab Simpowersystem BlocksetNo ratings yet

- Simulation of Some Power System, Control System and Power Electronics Case Studies Using Matlab and PowerWorld SimulatorFrom EverandSimulation of Some Power System, Control System and Power Electronics Case Studies Using Matlab and PowerWorld SimulatorNo ratings yet

- Power Electronics Applied to Industrial Systems and Transports, Volume 2: Power Converters and their ControlFrom EverandPower Electronics Applied to Industrial Systems and Transports, Volume 2: Power Converters and their ControlRating: 5 out of 5 stars5/5 (1)

- Investigation of the Usefulness of the PowerWorld Simulator Program: Developed by "Glover, Overbye & Sarma" in the Solution of Power System ProblemsFrom EverandInvestigation of the Usefulness of the PowerWorld Simulator Program: Developed by "Glover, Overbye & Sarma" in the Solution of Power System ProblemsNo ratings yet

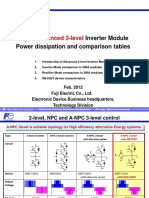

- Advanced 3-Level: T-Type Inverter Module Power Dissipation and Comparison TablesDocument32 pagesAdvanced 3-Level: T-Type Inverter Module Power Dissipation and Comparison TablesFelipeFalconiNo ratings yet

- BuckDocument36 pagesBuckBatuhan IzmırlıNo ratings yet

- Buck Converter Design DemystifiedDocument6 pagesBuck Converter Design Demystifiedshin sw100% (1)

- PFC HandbookDocument108 pagesPFC HandbookFelipeFalconiNo ratings yet

- Um 0ah0a 006 EngDocument1 pageUm 0ah0a 006 EngGaudencio LingamenNo ratings yet

- Emergency Room Delivery RecordDocument7 pagesEmergency Room Delivery RecordMariel VillamorNo ratings yet

- Clogging in Permeable (A Review)Document13 pagesClogging in Permeable (A Review)Chong Ting ShengNo ratings yet

- Victron MultiPlus 48 1200-13-16 Datasheet enDocument1 pageVictron MultiPlus 48 1200-13-16 Datasheet enBAHJARI AMINENo ratings yet

- JSA - 0026 Chipping & Granite cutting and lying Work At PB-19Document2 pagesJSA - 0026 Chipping & Granite cutting and lying Work At PB-19Koneti JanardhanaraoNo ratings yet

- Self Team Assessment Form - Revised 5-2-20Document6 pagesSelf Team Assessment Form - Revised 5-2-20api-630312626No ratings yet

- Course Tutorial ASP - Net TrainingDocument67 pagesCourse Tutorial ASP - Net Traininglanka.rkNo ratings yet

- Lecture 4Document25 pagesLecture 4ptnyagortey91No ratings yet

- Mechanics of Deformable BodiesDocument21 pagesMechanics of Deformable BodiesVarun. hrNo ratings yet

- Advantages and Disadvantages of The DronesDocument43 pagesAdvantages and Disadvantages of The DronesVysual ScapeNo ratings yet

- Lecture 1: Newton Forward and Backward Interpolation: M R Mishra May 9, 2022Document10 pagesLecture 1: Newton Forward and Backward Interpolation: M R Mishra May 9, 2022MANAS RANJAN MISHRANo ratings yet

- Ch07 Spread Footings - Geotech Ultimate Limit StatesDocument49 pagesCh07 Spread Footings - Geotech Ultimate Limit StatesVaibhav SharmaNo ratings yet

- BoQ East Park Apartment Buaran For ContractorDocument36 pagesBoQ East Park Apartment Buaran For ContractorDhiangga JauharyNo ratings yet

- Investigatory Project Pesticide From RadishDocument4 pagesInvestigatory Project Pesticide From Radishmax314100% (1)

- The Effect of Dodd-Frank On Divorcing Citizens 1Document5 pagesThe Effect of Dodd-Frank On Divorcing Citizens 1Noel CookmanNo ratings yet

- Transformer Oil Testing MethodsDocument10 pagesTransformer Oil Testing MethodsDEE TOTLVJANo ratings yet

- Application D2 WS2023Document11 pagesApplication D2 WS2023María Camila AlvaradoNo ratings yet

- Problems of Teaching English As A Foreign Language in YemenDocument13 pagesProblems of Teaching English As A Foreign Language in YemenSabriThabetNo ratings yet

- Create a seat booking form with Google Forms, Google Sheets and Google Apps Script - Yagisanatode - AppsScriptPulseDocument3 pagesCreate a seat booking form with Google Forms, Google Sheets and Google Apps Script - Yagisanatode - AppsScriptPulsebrandy57279No ratings yet

- Computer Portfolio (Aashi Singh)Document18 pagesComputer Portfolio (Aashi Singh)aashisingh9315No ratings yet

- AE-Electrical LMRC PDFDocument26 pagesAE-Electrical LMRC PDFDeepak GautamNo ratings yet

- ULN2001, ULN2002 ULN2003, ULN2004: DescriptionDocument21 pagesULN2001, ULN2002 ULN2003, ULN2004: Descriptionjulio montenegroNo ratings yet

- National Advisory Committee For AeronauticsDocument36 pagesNational Advisory Committee For AeronauticsSamuel ChristioNo ratings yet

- Ca. Rajani Mathur: 09718286332, EmailDocument2 pagesCa. Rajani Mathur: 09718286332, EmailSanket KohliNo ratings yet

- The Sound Collector - The Prepared Piano of John CageDocument12 pagesThe Sound Collector - The Prepared Piano of John CageLuigie VazquezNo ratings yet

- Daftar PustakaDocument4 pagesDaftar PustakaRamli UsmanNo ratings yet

- Trading Course DetailsDocument9 pagesTrading Course DetailsAnonymous O6q0dCOW6No ratings yet

- Doe v. Myspace, Inc. Et Al - Document No. 37Document2 pagesDoe v. Myspace, Inc. Et Al - Document No. 37Justia.comNo ratings yet

- MMW FinalsDocument4 pagesMMW FinalsAsh LiwanagNo ratings yet

- Henny Penny 500-561-600 TM - FINAL-FM06-009 9-08Document228 pagesHenny Penny 500-561-600 TM - FINAL-FM06-009 9-08Discman2100% (2)