Professional Documents

Culture Documents

A 1mb Flash Eeprom

Uploaded by

vbanuOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A 1mb Flash Eeprom

Uploaded by

vbanuCopyright:

Available Formats

ISSCC 89 /THURSDAY, F

Y 16,1989 / EAST G

ROOM / 11:45 A.M.

SESSION 10: T H A M 10.6:

N 0 NVO LATl LE ME M 0 R I ES

A 1Mb FLASH EEPROM

Raul-Adrian Cernea, Gheorghe Samachisa, Chien-Sheng Su, Hui-Fang Tsai, Yu-Sheng Kao, Cheng-Yuan Michael Wang, Yueh-Shing Chen, Alan Renninger, Ting Wong /James Brennan, Jr., Jeff Haines SEEQ Technology Inc. /National Semiconductor San Jose, CA /West Jordan, U T

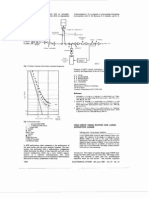

A lhlbit FLASII EEPROhl with a 5.6 x 4.4pm cell is fabricated with a double-polysilicon single-metal N-well CMOS process (Fig. 1). A double-diffused drain structure is used to reduce hot-electron degradation of N-channel peripheral devices. A summary of the process is presented in Table 1. The memory is organized into 1024 rows and 128 columns for each output. Erase and programming operations are internally controlled by a timer that is stabilized aagainst temperature and voltage supply variations. Addresses and data are latched during program and erase operations. Internal pumps generate the high voltage for the erase operation. Six redundant rows and two redundant columns are provided to enhance yield. Flash EEPROM cells similar t o the array cells are used as the programmable elements in the redundancy circuits. During the read operation, the sense current of the array cell, with drain kept at a constant voltage and gate at VCC, is compared t o a mirrored reference current (Fig. 2). An inverter, using a depletion transistor as the pull-up device for VCC insensitivity, senses the bit line voltage while feeding it back to the gate of a native pass transistor that regulates the bit line voltage and separates the bit line capacitance from the sensing node. An identical circuit is used t o regulate the drain voltage of the UV-erased flash EEPROM reference cell. The same circuit configuration is used t o clamp the sensing node at a voltage higher than that of the bit line while keeping the native transistor saturated for faster bit line precharge. With a poly-II-only word line, the access time is typically 120 ns (Fig. 3). For latching the addresses, a master-slave latch is set at the falling edge of the control signal (either WE or CE), while data is latched at the rising edge of the control signal. The internal timer controls the duration of the erase/programming operations with no need for external signals. Timing of these operations is optimized by the internal circuitry in order t o minimize the voltage stress experienced by the memory cell. The oscillator has two symmetrical halves with two capacitances alternatively charged t o a voltage Vref by a current Vref/R, R being the resistance of a poly-I1 resistor (Fig. 4).The period is 2RC, independent of Vref and thus of VCC, and has a low temperature coefficient. Measured period has +2%variation over VCC range and ?100/0variation over temperature range. The lOMHz oscillator drives 29 shift registers organized in three loops of shift register generators, t o provide all the waveforms needed for programming (ms range) and flash (seconds range) operations. Also the timer provides a fail-safe feature which prevents

unintentional erasing of the memory. The erase operation brings the whole chip or a column t o the FF state. Internal pumps, powered from Vpp, supply the drain current of the cells to be erased. In order t o supply DC current, depletion devices are used as the drivers of a cross-coupled system of diode-connect hlOS transistors (Fig. 5 ) . During the erase operation the drain voltage rises with time as the floating gate becomes less negatively charged through FowlerNordheim tunnelling. The gate of the cell remains grounded during this period. Programming operation is similar t o EPROhl and is also controlled by the timer. During power-up, a special circuit protects the memory against false write or erase. For testing and process monitoring, charge gain stress test, DC erase, and program disturb stress modes are implemented. In addition, the clock frequency can be read from an I/O pin. A micrograph of the chip is shown in Figure 6.

Acknowledgement The authors thank D. Anderson and B. Dockter for layout, D. Laughlin and B. Khoury for testing and characterization, M. Villott for support and P. Salsbury for guidance.

I . Sum Lithography Double Polysilicon N- Well CMOS Cell Size Cell Gate Oxide Interpoly Dielech'c Periphery Gate Oxide N+ Junction Depth P+ Junction Depth N-Well Junction Depth N-Channel Min Left P-Channel Min Left

14.6pm2 200 A 375 N 340 A .4pm

.5um

3.75pm 1.2pm 1.4~m

TABLE 1 - Process parameters

138

1989 lEEE International Sotid-Stow Circuita Conference

~ 1989 IEEE ~ 6 ~ 1

Authorized licensed use limited to: CSIC. Downloaded on July 1, 2009 at 06:45 from IEEE Xplore. Restrictions apply.

ISSCC 89 /THURSDAY, FEBRUARY 16,1989 1 EAST GRAND BALLROOM I THAM 10.6

FIGL RE 3

- Access

time

VDD

VDD

VDD

REF

FIGURE; 1- Oscillator

FIGURE 1 - (a) Flash EEPROM cell cross section (b) Flash E.FPKO\I arral

PRECHARGING PATH SENSING NODE

OUTPUT BUFFER

REFERENCE CELL (UVERASED)

1."."'",-E,L

FIGURE 2

- Sense

amplifier

FIGURE 5

Write/flash pump

FIGURE 6 - See page 316

DIGEST OF TECHNICAL PAPERS

739

Authorized licensed use limited to: CSIC. Downloaded on July 1, 2009 at 06:45 from IEEE Xplore. Restrictions apply.

T H A M 10.6: A lMb FLASH EEPROM (Continued from page 139)

FIGURE 6 - Chip micrograph

316

1989 IEEE lnternational Solid-State Circuits Conference

Authorized licensed use limited to: CSIC. Downloaded on July 1, 2009 at 06:45 from IEEE Xplore. Restrictions apply.

You might also like

- Electronics Explained: Fundamentals for Engineers, Technicians, and MakersFrom EverandElectronics Explained: Fundamentals for Engineers, Technicians, and MakersRating: 5 out of 5 stars5/5 (5)

- Basic Electronics Vol 2 - US NavyDocument332 pagesBasic Electronics Vol 2 - US Navyozzaib100% (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Antenna Analyzer vk5jst Version 1 Instructions PDFDocument10 pagesAntenna Analyzer vk5jst Version 1 Instructions PDFPisu Miau Pisu MiauNo ratings yet

- GE Energy: Digital Signal Processor Control Board IS200DSPXH - A - DDocument20 pagesGE Energy: Digital Signal Processor Control Board IS200DSPXH - A - DFathi YahyaouiNo ratings yet

- CQ 04 April 1946Document68 pagesCQ 04 April 1946Сергей БезразличныйNo ratings yet

- HPE Primera Data Reduction Technical White Paper-A50000209enwDocument34 pagesHPE Primera Data Reduction Technical White Paper-A50000209enwFrancisco HaroNo ratings yet

- Ultra-low Power Charge-Pump PLL with High Temperature StabilityDocument4 pagesUltra-low Power Charge-Pump PLL with High Temperature Stabilityhawking1122No ratings yet

- Truck Evo Manual FinalDocument28 pagesTruck Evo Manual FinalRodrigo Zuñiga RosselNo ratings yet

- Build A Rocket AltimeterDocument9 pagesBuild A Rocket AltimeterMisesWasRight100% (1)

- Edexcel IGCSE ICT Student's Book AnswersDocument50 pagesEdexcel IGCSE ICT Student's Book AnswersAvrinox89% (46)

- 158-Calculation of Short Circuit CurrentsDocument24 pages158-Calculation of Short Circuit Currentsgeorgel1980100% (2)

- GX Works2 TrainingDocument350 pagesGX Works2 Trainingmulomantore0% (1)

- Static vs. Dynamic Timing AnalysisDocument8 pagesStatic vs. Dynamic Timing Analysisd-fbuser-61705927No ratings yet

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- A High Capacitive-Coupling Ratio (Hicr) Cell V-Only 64 Mbit and Future Flash MemoriesDocument4 pagesA High Capacitive-Coupling Ratio (Hicr) Cell V-Only 64 Mbit and Future Flash MemoriesAmitNo ratings yet

- A CMOS Programmable Analog Memory-Cell ArrayDocument8 pagesA CMOS Programmable Analog Memory-Cell Arrayvaishnaw25No ratings yet

- 4k x 2k and 4k x 4k CCD ManualDocument21 pages4k x 2k and 4k x 4k CCD ManualagudpagudpNo ratings yet

- Algunas Unidades de Control Electrónico para Estudios de La Conducta OperanteDocument4 pagesAlgunas Unidades de Control Electrónico para Estudios de La Conducta OperanteALEJANDRO MATUTENo ratings yet

- Tuesday 3.1.1 1.00 PM 10712 TontiDocument38 pagesTuesday 3.1.1 1.00 PM 10712 TontiDarshan PatelNo ratings yet

- A Beam-Forming Transmit ASIC For Driving Ultrasonic Arrays: John V. Hat®eld, Kwet Seng ChaiDocument7 pagesA Beam-Forming Transmit ASIC For Driving Ultrasonic Arrays: John V. Hat®eld, Kwet Seng ChaitoloiceNo ratings yet

- FH5780897NP SDocument132 pagesFH5780897NP SNidhiNo ratings yet

- EEC 3111 - D E C S: Igital Lectronics in Ommunication YstemsDocument22 pagesEEC 3111 - D E C S: Igital Lectronics in Ommunication YstemsAlaa MalekNo ratings yet

- C. Damian, C. Zet, I. Enculescu, R. Spohr: Virtual PotentiostatDocument5 pagesC. Damian, C. Zet, I. Enculescu, R. Spohr: Virtual Potentiostatnajam696No ratings yet

- Dmill 4nn19ec004Document25 pagesDmill 4nn19ec004charan mNo ratings yet

- A 15mw 3125ghz PLL For Serial Backplane Transceivers in 013m CmoDocument3 pagesA 15mw 3125ghz PLL For Serial Backplane Transceivers in 013m CmoAhmed ShafeekNo ratings yet

- A Double-Tail Latch-Type Voltage Sense Amplifier With 18ps Setup+Hold TimeDocument3 pagesA Double-Tail Latch-Type Voltage Sense Amplifier With 18ps Setup+Hold TimeburakgonenNo ratings yet

- Basic Electronics Lab ManualDocument103 pagesBasic Electronics Lab ManualApril ShowersNo ratings yet

- ECPC Assignment 1 - Hardware - With AnsDocument4 pagesECPC Assignment 1 - Hardware - With AnsYashwin.v YashuNo ratings yet

- Practical 2P12 Semiconductor Devices: What You Should Learn From This PracticalDocument11 pagesPractical 2P12 Semiconductor Devices: What You Should Learn From This PracticalDevesh GargNo ratings yet

- Eal-Time Full Signature Corrosion Detection of e G o D Casing PipesDocument6 pagesEal-Time Full Signature Corrosion Detection of e G o D Casing PipesMani MaranNo ratings yet

- Design of 512-Bit Logic Process-Based Single Poly EEPROM IPDocument9 pagesDesign of 512-Bit Logic Process-Based Single Poly EEPROM IPPhuc HoangNo ratings yet

- Basic ElectronicsDocument126 pagesBasic ElectronicsFarazNo ratings yet

- SPICE Version 2G User's GuideDocument48 pagesSPICE Version 2G User's Guidexing tangNo ratings yet

- Ieee Bakker 1996Document5 pagesIeee Bakker 1996kurabyqldNo ratings yet

- Philips Mod 21pt9470-55 - 44 - 21sl9 - Chasis Sk8.0l CADocument36 pagesPhilips Mod 21pt9470-55 - 44 - 21sl9 - Chasis Sk8.0l CACarlos MedinaNo ratings yet

- A Double-Tail Latch-Type Voltage Sense Amplifier With 18ps Setup+Hold TimeDocument3 pagesA Double-Tail Latch-Type Voltage Sense Amplifier With 18ps Setup+Hold TimeWang TianyangNo ratings yet

- Kalisz 2003Document4 pagesKalisz 2003norbertscribdNo ratings yet

- Online Monitoring of Underground Cables Using Low-Cost SensorsDocument4 pagesOnline Monitoring of Underground Cables Using Low-Cost SensorspipotxNo ratings yet

- 0.18um Modular Triple Self-Aligned Embedded Split-Gate Flash MemoryDocument2 pages0.18um Modular Triple Self-Aligned Embedded Split-Gate Flash MemoryYohanes ErwinNo ratings yet

- Conclusion:: To DiagnosticsDocument3 pagesConclusion:: To DiagnosticsDhaval PatelNo ratings yet

- Magnavox Lo3.2U AA For (13MT1431/17, 20MT1331/17)Document44 pagesMagnavox Lo3.2U AA For (13MT1431/17, 20MT1331/17)Jorge G. Manzanero100% (2)

- Lesson 1 - ECG Theory - SimulationDocument10 pagesLesson 1 - ECG Theory - SimulationThanh TúNo ratings yet

- Simple automatic-shutoff circuit uses few componentsDocument5 pagesSimple automatic-shutoff circuit uses few componentsJuan Manuel Han MacNo ratings yet

- Simple PotentiostatDocument3 pagesSimple PotentiostatguiburNo ratings yet

- Realization of a Simple AND-OR Circuit and Propagation Delay StudyDocument6 pagesRealization of a Simple AND-OR Circuit and Propagation Delay StudyJoanne Lai100% (1)

- Experiment 5 - Inverter CharacteristicsDocument7 pagesExperiment 5 - Inverter CharacteristicsGowtham SpNo ratings yet

- Low Power Single Chip PstatDocument2 pagesLow Power Single Chip PstatKay ReimersNo ratings yet

- I, and I, and Zref Separately We Measured Changes of AboutDocument5 pagesI, and I, and Zref Separately We Measured Changes of AboutBodhayan PrasadNo ratings yet

- Philips L7.3a Aa Chassis TV SMDocument49 pagesPhilips L7.3a Aa Chassis TV SMRoger_74No ratings yet

- Development of The Carioca Front-End Chip For The LHCB Muon DetectorDocument11 pagesDevelopment of The Carioca Front-End Chip For The LHCB Muon DetectorAmir SultanNo ratings yet

- DS1302 Trickle-Charge Timekeeping ChipDocument13 pagesDS1302 Trickle-Charge Timekeeping ChipPravin MevadaNo ratings yet

- A 256Mb SDRAM Using A Register-Controlled Digital DLL - Register Controller DLLDocument3 pagesA 256Mb SDRAM Using A Register-Controlled Digital DLL - Register Controller DLLAhmed Fathy MoustafaNo ratings yet

- EEC 3111 - D E C S: Igital Lectronics in Ommunication YstemsDocument27 pagesEEC 3111 - D E C S: Igital Lectronics in Ommunication YstemsAlaa MalekNo ratings yet

- MOSFET Characterization LabDocument8 pagesMOSFET Characterization LabMjdNo ratings yet

- Cmos Microelectrode Array For Extracellular Stimulation and Recording of Electrogenic CellsDocument4 pagesCmos Microelectrode Array For Extracellular Stimulation and Recording of Electrogenic CellsAlex WongNo ratings yet

- Slup083 PDFDocument7 pagesSlup083 PDFlu1agpNo ratings yet

- Qs & As Class I+IIDocument9 pagesQs & As Class I+IIphyoNo ratings yet

- Mahalakshmi: Unit - Iv - Storage and Display DevicesDocument18 pagesMahalakshmi: Unit - Iv - Storage and Display Devicestareq omarNo ratings yet

- Ee 3101 Electronics I Laboratory Experiment 9 Lab Manual Applications of Ic Building BlocksDocument5 pagesEe 3101 Electronics I Laboratory Experiment 9 Lab Manual Applications of Ic Building BlocksPriyanshu KumawatNo ratings yet

- 2011 Scaling CPLDocument5 pages2011 Scaling CPLankushwreNo ratings yet

- Philips Chassis l9.1 e AaDocument63 pagesPhilips Chassis l9.1 e AaeduardskNo ratings yet

- Otp For DCDCDocument14 pagesOtp For DCDCseanNo ratings yet

- An Active, Microfabricated, Scalp Electrode Array For EEG RecordingDocument6 pagesAn Active, Microfabricated, Scalp Electrode Array For EEG RecordingChristopher RoblesNo ratings yet

- 7-11 Brosura de Prezentare PPPDocument28 pages7-11 Brosura de Prezentare PPPWeb AdevarulNo ratings yet

- Electrronic DevicesDocument234 pagesElectrronic DevicesvbanuNo ratings yet

- Seria@20micro@20nano@20vol@2024 FDocument228 pagesSeria@20micro@20nano@20vol@2024 FvbanuNo ratings yet

- Vol@2023 Cursiv@20Document174 pagesVol@2023 Cursiv@20vbanuNo ratings yet

- Mne 14Document260 pagesMne 14vbanuNo ratings yet

- Vol MNE 25 2017fDocument117 pagesVol MNE 25 2017fvbanuNo ratings yet

- Vol MNE 25 2017fDocument117 pagesVol MNE 25 2017fvbanuNo ratings yet

- SiC Schottky Diodes For Harsh Environment Space ApplicationsDocument9 pagesSiC Schottky Diodes For Harsh Environment Space ApplicationsvbanuNo ratings yet

- Pic 16 F 616Document172 pagesPic 16 F 616Maneesh BakaleNo ratings yet

- 2014 Samsung Electronics Annual ReportDocument123 pages2014 Samsung Electronics Annual ReportBoyJuniorOfMr'ChekaNo ratings yet

- FPGA UG 02094 1 0 Key Phrase HM01B0 UPduino Shield DemoDocument15 pagesFPGA UG 02094 1 0 Key Phrase HM01B0 UPduino Shield DemoBapiNo ratings yet

- Release Notes For C51 KEIL SoftwareDocument40 pagesRelease Notes For C51 KEIL SoftwareYeong Ming KeatNo ratings yet

- Xs Flash Instant GBDocument64 pagesXs Flash Instant GBAlin OlteanNo ratings yet

- ST Link UtilityDocument11 pagesST Link UtilityAleixLNo ratings yet

- EN25F80Document35 pagesEN25F80Juan GutierrezNo ratings yet

- Connecting and Hacking The Hi3518EV200 (ChipSet BulletCam SmartWares)Document13 pagesConnecting and Hacking The Hi3518EV200 (ChipSet BulletCam SmartWares)Joop MeloenNo ratings yet

- Temperature Controlled Fan SpeedDocument4 pagesTemperature Controlled Fan Speedsgrao2010549No ratings yet

- How To Reset Cisco 2960Document2 pagesHow To Reset Cisco 2960bryan pereiraNo ratings yet

- Asus P5SD1-FM2Document76 pagesAsus P5SD1-FM2dkrcmar1No ratings yet

- Flash BloquesDocument13 pagesFlash BloquesJose Alonso CalleNo ratings yet

- Integra Plus P en 5c1f6db6 PDFDocument102 pagesIntegra Plus P en 5c1f6db6 PDFHarisNo ratings yet

- AT89S52 Hardware-Software ManualDocument39 pagesAT89S52 Hardware-Software ManualugocirriNo ratings yet

- Mic 3Document18 pagesMic 3Gopinathan MNo ratings yet

- OBSTACLE DETECTOR ROBOT BY KULDEEP PANWAR AND DEVANSHU SHARMADocument11 pagesOBSTACLE DETECTOR ROBOT BY KULDEEP PANWAR AND DEVANSHU SHARMAParul BansalNo ratings yet

- s112 nrf52 7.2.0 Migration-DocumentDocument11 pagess112 nrf52 7.2.0 Migration-DocumentVinh LeNo ratings yet

- Pacsystems Rx3I: Ic695Niu001 PlusDocument13 pagesPacsystems Rx3I: Ic695Niu001 PlusMohammad Nabeel SarwarNo ratings yet

- Mtech ProjectsDocument14 pagesMtech Projectsmaxxtorr723No ratings yet

- Flash Erasable, Reprogrammable CMOS PAL® Device: PALCE22V10Document13 pagesFlash Erasable, Reprogrammable CMOS PAL® Device: PALCE22V10Imran Ali ShahNo ratings yet

- Ch341a Mini Flash ProgrammerDocument5 pagesCh341a Mini Flash ProgrammerendreminarikNo ratings yet

- Veho Muvi Pro Micro DV Camcorder User GuideDocument60 pagesVeho Muvi Pro Micro DV Camcorder User GuideSabrina HarveyNo ratings yet

- Esp Wroom s2 DatasheetDocument22 pagesEsp Wroom s2 DatasheetLucas Gabriel Cosmo MoraisNo ratings yet

- SSD-Insider: Internal Defense of Solid-State Drive Against Ransomware With Perfect Data RecoveryDocument10 pagesSSD-Insider: Internal Defense of Solid-State Drive Against Ransomware With Perfect Data Recoverymeena meenakshiNo ratings yet

- AT91SAM9G45-EKES User Guide: 6481B-ATARM-27-Nov-09Document66 pagesAT91SAM9G45-EKES User Guide: 6481B-ATARM-27-Nov-09Abolfazl SaeedieNo ratings yet