Professional Documents

Culture Documents

Solution Inverter

Uploaded by

Pragati RanaOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Solution Inverter

Uploaded by

Pragati RanaCopyright:

Available Formats

ECE 438: Digital Integrated Circuits Assignment #4 Solution The Inverter

Text: Chapter 5, Digital Integrated Circuits 2nd Ed, Rabaey

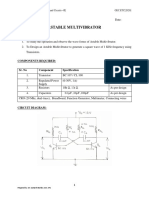

1) Consider the CMOS inverter circuit in Figure P1 with the following parameters. Assume long channel transistors and no velocity saturation.

Vin

Vout

Figure P1 Find VOL, VOH, VIL, and VIH on the VTC. Also find the noise margins of this inverter.

2) Consider a CMOS inverter circuit with power supply voltage VDD = 3.3V. The I-V characteristic of the NMOS transistor is specified below. When VGS=3.3V, the drain current reaches its saturation level Isat = 2mA, for VDS > 2.5V. Assume that the input signal applied to the gate is a step pulse that switches instantaneously, from 0V to 3.3V.

3) Consider a CMOS inverter with supply voltage of VDD = 5V. Assume long channel transistors and no velocity saturation. Determine the fall time tfall, defined as the time elapsed between 90% to 10% transition of the output voltage. Assume kn = 20A/V2, others are given below.

4) An inverter is simulated in SPICE in the following conditions and characteristics

5) For the resistive-load inverter in Figure P5, and assume an output load of 3 pF Given: VT0 = 0.43V, VDSAT=0.63, kn=115A/V2, = 0.06 V-1, VOH = 2.5V, VOL = 0.0463V

Figure P5 a) Calculate tplh, tphl, and tp Solution tpLH=0.69RLCL= 155 nsec. For tpHL: First calculate Ron for Vout at 2.5V and 1.27315V At Vout=2.5V, IDVsat=0.439mA giving Ron= 5695 (VOH VOL)/2.

t Vout=1.27315V, IDvsat=0.4106mA giving Ron= 3100.85. Thus, the average resistance between Vout=2.5V and Vout=1.27315V is Raverage=4.398k. tpHL=0.69RaverageCL=9.104nsec. tp=av{tpLH, tpHL}=82.05nsec ASIDE: if first-order approximation is considered, such that the 50% point is Vdd/2 t Vout=1.25V, IDvsat=0.41m giving Ron= 3049. Thus, the average resistance between Vout=2.5V and Vout=1.25V is Raverage=4.372k. tpHL=0.69RaverageCL=9.05nsec. tp=av{tpLH, tpHL}=82.0nsec b) Are the rising and falling delays equal? Why or why not? Solution tpLH >> tpHL because RL=75k is much larger than the effective linearized on-resistance of M1. c) Compute the static and dynamic power dissipation assuming the gate is clocked as fast as possible. Solution Static Power: VIN=VOL gives Vout=VOH=2.5V, thus IVDD=0A so PVDD=0W. VIN=VOH gives Vout=VOL=46.3mV, which is in the linear region. Calculating the current through M1 gives IVDD=32.8A PVDD=82W Dynamic Power: NOTE: fmax= 1 / tp =1 / 82.0nsec Pdyn=CLV*Vdd*fmax=3pF*(2.5V-46.3mV)*2.5V*12.2MHz=0.225mW.

6) Figure P6 shows two implementations of MOS inverters. Circuit A uses only NMOS transistors. Circuit B is a static CMOS inverter (NOTE: short-channel transistors and velocity saturated)

W/L = 0.75/0.25

Figure P6

a) Calculate VOH, VOL, VM for each case.

Setting ID3 + ID4 = 0, we get VM = 1.095V. So the assumption that both transistors were velocity saturated holds.

b) Find VIH, VIL, NML and NMH for each inverter and comment on the results. Given that VIL = 0.503V and VIH = 1.35V for circuit A, and VIL = 0.861V and VIH = 1.22V for circuit B. How can you increase the noise margins and reduce the undefined region? Solution Circuit A Based on the VOL and VOH from part (a) VIL = 0.503V, VIH = 1.35V NMH = VOH - VIH = 1.765 - 1.35 = 0.415V, NML = VIL - VOL = 0.503- 0.263 = 0.240V Circuit B VIL = 0.861V, VIH = 1.22V NMH = VOH - VIH = 2.5V - 1.22V = 1.28V, NML = VIL - VOL = 0.861V- 0V = 0.861V We can increase the noise margins by moving VM closer to the middle of the output voltage swing. c) Comment on the differences in the VTCs, robustness and regeneration of each inverter. Solution It is clear from the two VTCs, that the CMOS inverter is more robust, since the low and high noise margins are higher than the first inverter. Also the regeneration in the second inverter is greater since it provides rail to rail output and the gain of the inverter is much greater.

7) For this problem assume: VDD = 2.5V, WP/L = 1.25/0.25, WN/L = 0.375/0.25, L=Leff =0.25m (i.e. xd= 0m), CL=Cinvgate, kn = 115A/V2, kp= -30A/V2, Vtn0 = | Vtp0 | = 0.4V, = 0V-1, = 0.4, 2|f|=0.6V, and tox = 58A. Use the HSPICE model parameters for parasitic capacitance given below (i.e. Cgd0, Cj, Cjsw), and assume that VSB=0V. (NOTE: short-channel transistors and velocity saturated)

Figure P7

a) What is the VM for this inverter? Solution Assume that VM is around midrail (1.25V). That means that the NMOS is velocity saturated and the PMOS is saturated. To find VM, we set the sum of the currents at Vout equal to 0 using the correct equation for each device:

b) Calculate tPHL, tPLH assuming CLeff = 6.5fF. (Assume an ideal step input, i.e. trise=tfall=0. Do this part by computing the average current used to charge/discharge CLeff.) Solution We can estimate the propagation delay using the approximation t =Q/I, where Q 10

= CLeffVDD and I is the average current used to charge/discharge CLeff. During the high-to-low transition CLeff is discharged through the NMOS transistor so I = IavgN. During the low-to-high transition CLeff is charged through the PMOS transistor so I = IavgP. In summary:

IavgP =

IavgN =

0.223 0.208

0.216

37.65

included channel length modulation, but it is ok if your solution did not (see problem assumptions).

8) Consider the circuit in Figure P8 (which is a low-swing driver, not an inverter). Given VTn0 = 0.43 and VTp0 = -0.4. NOTE: short-channel transistors and velocity saturated.

Figure P8

a) What is the voltage swing on the output node (Vout)? Assume =0. 11

Solution The range will be from 0.4 V to 2.07 V, since the PMOS is a weak pull down device and the NMOS is a weak pull up device. b) Compute tpLH (i.e. the time to transition from VOL to (VOH + VOL) /2). Assume the input rise time to be 0. VOL is the output voltage with the input at 0V and VOH is the output voltage with the input at 2.5V. Solution When the input is high and the capacitor charges, the PMOS device is in cutoff and the NMOS is velocity saturated for the duration of the charging. The total voltage range is 0.4 V to 2.07 V, so the midpoint is 1.24 V. We can use the average current method to approximate tplh. For the velocity saturated NMOS:

Solving for the current at V=0.4 V and V=1.24 V and averaging yields an average current of 404 uA. Then:

12

You might also like

- Mooring Design AnalysisDocument41 pagesMooring Design AnalysisRaghu Nath100% (1)

- Power Amp ClassificationsDocument28 pagesPower Amp Classificationsshubhankar palNo ratings yet

- Transformer stability testing and commissioningDocument4 pagesTransformer stability testing and commissioningraul116574480% (5)

- Subsea Fasteners Guideline - 10002444011 PDFDocument28 pagesSubsea Fasteners Guideline - 10002444011 PDFbert berry100% (1)

- Chapter 1: Introduction to ElectronicsDocument87 pagesChapter 1: Introduction to ElectronicsnicoleNo ratings yet

- Angle ModulationDocument26 pagesAngle Modulationajeesh r100% (1)

- Solns - 1 CmosDocument15 pagesSolns - 1 Cmosramprakash_rampelliNo ratings yet

- Question BankDocument6 pagesQuestion Banksweetkhushboo786_592No ratings yet

- Solns 2cmosDocument18 pagesSolns 2cmosramprakash_rampelliNo ratings yet

- Solns 9Document66 pagesSolns 9ramprakash_rampelliNo ratings yet

- Expt 9 - Astable-Multivibrator (2020)Document5 pagesExpt 9 - Astable-Multivibrator (2020)samarth100% (1)

- Uniform Plane Waves SolutionsDocument52 pagesUniform Plane Waves SolutionsmboillaNo ratings yet

- Sheet 3 - SolutionDocument10 pagesSheet 3 - SolutionMajid HelmyNo ratings yet

- Chapter 5 Problems CMOS INVERTERDocument8 pagesChapter 5 Problems CMOS INVERTERShykh SheharyarNo ratings yet

- PSEUDO CMOS: A DESIGN STYLE FOR LOW COST AND ROBUST FLEXIBLE ELECTRONICSDocument22 pagesPSEUDO CMOS: A DESIGN STYLE FOR LOW COST AND ROBUST FLEXIBLE ELECTRONICSjyothsnavkNo ratings yet

- 4) Frequency and Phase ModulationDocument13 pages4) Frequency and Phase ModulationAditya PaulNo ratings yet

- Experiment No. (5) : Frequency Modulation & Demodulation: - ObjectDocument5 pagesExperiment No. (5) : Frequency Modulation & Demodulation: - ObjectFaez FawwazNo ratings yet

- Class 1-20Document149 pagesClass 1-20SaurabhBisht100% (1)

- Semiconductor Device CalculationsDocument37 pagesSemiconductor Device Calculationsbhasin_hemantNo ratings yet

- BEE2123 TUT4 - Bridge AnswerDocument9 pagesBEE2123 TUT4 - Bridge AnswerWatashiNoNo ratings yet

- Multistage Differential AmplifiersDocument46 pagesMultistage Differential Amplifiersmamdery_kumarNo ratings yet

- Expt - 7 :transistorized Astable MultivibratorDocument4 pagesExpt - 7 :transistorized Astable Multivibratorsamarth100% (1)

- Chapter 2 - Waveguide PDFDocument38 pagesChapter 2 - Waveguide PDFHiroshi RayNo ratings yet

- Analog Electronics Circuits (Semester V - EEE) : Important QuestionsDocument2 pagesAnalog Electronics Circuits (Semester V - EEE) : Important QuestionsHadush KingNo ratings yet

- 08-Com101 AMDocument11 pages08-Com101 AMHồng HoanNo ratings yet

- Generalized Method for Solving Clipper Circuit ProblemsDocument4 pagesGeneralized Method for Solving Clipper Circuit ProblemsAnshuman Vyas0% (2)

- Module 2 Op-AmpDocument26 pagesModule 2 Op-AmpSTUDENTS OF DOE CUSATNo ratings yet

- MCQ-EC 304 Transmission Lines and WaveguidesDocument6 pagesMCQ-EC 304 Transmission Lines and WaveguidesSreejithNo ratings yet

- Module 2 - PPT 4 - Miller Effect and Miller Capacitance and High Frequency Analysis PDFDocument11 pagesModule 2 - PPT 4 - Miller Effect and Miller Capacitance and High Frequency Analysis PDFGokulnath SNo ratings yet

- Questions On Small Signal Model of AmpDocument2 pagesQuestions On Small Signal Model of AmpdevsrivastavaNo ratings yet

- Objective Questions On Microwave Devices For BSNL and ISRO ExamsDocument29 pagesObjective Questions On Microwave Devices For BSNL and ISRO ExamsRaj Kumar50% (4)

- Chapter 12 Differential AmplifiersDocument34 pagesChapter 12 Differential Amplifiersshubhankar palNo ratings yet

- Iecep EsatDocument29 pagesIecep EsatIvy Cee100% (1)

- Astable and Monostable Multivibrator Trainer NV6507Document10 pagesAstable and Monostable Multivibrator Trainer NV6507Himadri MandalNo ratings yet

- EC6411 Circuit & Devices Lab ManualDocument93 pagesEC6411 Circuit & Devices Lab ManualKALAIMATHINo ratings yet

- Angle ModulationDocument28 pagesAngle ModulationChinmoy GhoraiNo ratings yet

- Astable Multivibrator ExperimentDocument5 pagesAstable Multivibrator ExperimentShivakumar goud100% (1)

- Rectangular Waveguide TE Mode MATLABDocument4 pagesRectangular Waveguide TE Mode MATLABSiddharth MakvanaNo ratings yet

- EC2307-New Digital Communication Lab Manual Odd 2011Document53 pagesEC2307-New Digital Communication Lab Manual Odd 2011chenthiltrNo ratings yet

- ADC 11 Digital ModulationDocument38 pagesADC 11 Digital ModulationMehboob KhokharNo ratings yet

- BJTDocument6 pagesBJTengineerluvNo ratings yet

- CH 4 B P LathiDocument99 pagesCH 4 B P LathiHarsh LuharNo ratings yet

- Simulation of a Voltage-Mode PWM Boost ConverterDocument103 pagesSimulation of a Voltage-Mode PWM Boost ConverterAshok KumarNo ratings yet

- Questions On DSP - Basic SignalingDocument10 pagesQuestions On DSP - Basic Signalingkibrom atsbhaNo ratings yet

- Solved ProblemsDocument24 pagesSolved ProblemsParth Cholera100% (1)

- Experiment No.2: Colpitt OscillatorDocument3 pagesExperiment No.2: Colpitt OscillatorBhadresh Renuka50% (2)

- Stripline FundamentalsDocument18 pagesStripline FundamentalsJamilNo ratings yet

- Introduction to Electrical Machines Chapter One: Electromagnetic PrinciplesDocument286 pagesIntroduction to Electrical Machines Chapter One: Electromagnetic Principlestesfayregs gebretsadik100% (1)

- Design A RC Coupled CE Transistor AmplifierDocument7 pagesDesign A RC Coupled CE Transistor AmplifierSudeep Nayak100% (1)

- EDC - Important ProblemsDocument12 pagesEDC - Important ProblemssansureNo ratings yet

- Engineering Electromagnetics: The Steady Magnetic FieldDocument71 pagesEngineering Electromagnetics: The Steady Magnetic FieldSandeep RajputNo ratings yet

- Nescom TestDocument1 pageNescom TestGreen SignalNo ratings yet

- Chapter 2 - Basic Concepts of ModulationDocument25 pagesChapter 2 - Basic Concepts of Modulationayu afNo ratings yet

- Emona Lab ReportDocument14 pagesEmona Lab ReportGmind0% (1)

- Ec3058D-Vlsi Circuits and Systems Winter Semester-2020-21: DD Ton TopDocument2 pagesEc3058D-Vlsi Circuits and Systems Winter Semester-2020-21: DD Ton TopGamer AnonymousNo ratings yet

- Assignment - Unit 1Document2 pagesAssignment - Unit 1ApoorvaNo ratings yet

- Tutorial 2023 - AnsDocument3 pagesTutorial 2023 - Anschetannp121No ratings yet

- Digital Integrated Circuits Problem Sheet 2: OL OH MDocument2 pagesDigital Integrated Circuits Problem Sheet 2: OL OH MChanandler BongNo ratings yet

- You. You Are Not Allowed To Share Your Solutions With Others in The ClassDocument16 pagesYou. You Are Not Allowed To Share Your Solutions With Others in The ClassJitendra SinghNo ratings yet

- Homework 3 - SolutionsDocument14 pagesHomework 3 - SolutionsYahya Salam SalehNo ratings yet

- Tutorial Sheet 5Document2 pagesTutorial Sheet 5Shashank SinghNo ratings yet

- Vlsi Assignment 1 SolvedDocument17 pagesVlsi Assignment 1 SolvedNilesh ChauhanNo ratings yet

- MOS Transistor Analysis and Circuit DesignDocument4 pagesMOS Transistor Analysis and Circuit DesignAnh KhoaNo ratings yet

- Answers of Test On Quantum Physics and Particle PhysicsDocument3 pagesAnswers of Test On Quantum Physics and Particle PhysicsFakin AsholNo ratings yet

- CV BaxterDocument3 pagesCV BaxterGYANNo ratings yet

- Taller 2 Pearson (1 Al 8)Document19 pagesTaller 2 Pearson (1 Al 8)WALTER ANDRES CORDOBA CACERENo ratings yet

- 11.5 Applications of Right-And Non-Right-Angled TrigonometryDocument2 pages11.5 Applications of Right-And Non-Right-Angled TrigonometryAanya RalhanNo ratings yet

- Jis G 0417Document52 pagesJis G 0417Thanh Tín TăngNo ratings yet

- Screw gaugeDocument4 pagesScrew gaugenopeyeah88No ratings yet

- NDT for Detection of HTHA in Petrochemical PlantsDocument7 pagesNDT for Detection of HTHA in Petrochemical PlantsMahbub ShojibNo ratings yet

- AltuglasDocument8 pagesAltuglasLUCACOMP1974No ratings yet

- Magnetic IDocument34 pagesMagnetic IDeepesh SureshNo ratings yet

- Measuring motion and forcesDocument3 pagesMeasuring motion and forcesALS-MP CARNo ratings yet

- AsdasdDocument3 pagesAsdasdNero James Sia100% (1)

- Flex Cheat SheetDocument1 pageFlex Cheat SheetjezzieNo ratings yet

- St. Columban'S Institute: Mathematics - 8Document3 pagesSt. Columban'S Institute: Mathematics - 8roseNo ratings yet

- Specifications PDFDocument1 pageSpecifications PDFRazvan SasuNo ratings yet

- Calculating Magnetic Field and Deflection VoltageDocument1 pageCalculating Magnetic Field and Deflection Voltagearnabrc123No ratings yet

- TDS Byk-1780 enDocument2 pagesTDS Byk-1780 enabhijit.home2022No ratings yet

- Types of Agitators, Agitator's Design and Significance - Pharma EngineeringDocument58 pagesTypes of Agitators, Agitator's Design and Significance - Pharma Engineeringmyself_riteshNo ratings yet

- LE13-038-R04a (TECHNICAL SHEET)Document83 pagesLE13-038-R04a (TECHNICAL SHEET)Sermchart PakumNo ratings yet

- CE602 MockboardQuiz2Document8 pagesCE602 MockboardQuiz2Najib A. CasanNo ratings yet

- Geometry Worksheet on Shapes and AnglesDocument4 pagesGeometry Worksheet on Shapes and AnglesairinputNo ratings yet

- Electric Circuits: Chapter 6ADocument40 pagesElectric Circuits: Chapter 6Ananio_7No ratings yet

- 6th SEM - Sep-22Document4 pages6th SEM - Sep-22Jay RanjanNo ratings yet

- Chip Formation: IntroductionDocument5 pagesChip Formation: IntroductionDr.S.Ravi CITNo ratings yet

- DP1 Practice 2: MarkschemeDocument17 pagesDP1 Practice 2: MarkschemeaurennosNo ratings yet

- Properties of Thrusts and Upper Bounds For The Size of Thrust SheetsDocument12 pagesProperties of Thrusts and Upper Bounds For The Size of Thrust SheetsstephenNo ratings yet

- Documents of Daily Check Sheets For WDs and CR10K - 20130530Document37 pagesDocuments of Daily Check Sheets For WDs and CR10K - 20130530Vijay RajaindranNo ratings yet

- Soil Mechanics Laboratory ReportDocument17 pagesSoil Mechanics Laboratory ReportJordan Marcel100% (1)