Professional Documents

Culture Documents

4.planificacion de Uso Del Procesador

Uploaded by

Cristian Llanes VillagraOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

4.planificacion de Uso Del Procesador

Uploaded by

Cristian Llanes VillagraCopyright:

Available Formats

Planificacin de uso del procesador

Contenidos

(T5)

Planificacin en VAX/VMS Planificacin en UNIX 4.4 BSD Estructuras de datos Clculo de prioridades Planificacin en W2K

Concepto de planificacin Estados de un proceso Planificador / Dispatcher Planificadores Algoritmos de planificacin Criterios de evaluacin Planificacin FIFO Planificacin SJF

Mtodo de prediccin

Quantum

Escenarios de planificacin Ajuste de prioridad en W2K

Planificacin prioridades Planificacin Planificacin Planificacin multinivel

con con requisa round-robin con colas

Colas multinivel realimentadas

Planificacin del procesador

2

Concepto de planificacin (i)

La ejecucin de un trabajo se compone de secuencias de procesador y de espera Objetivo de la planificacin:

Incrementar el rendimiento global del sistema Maximizar el uso de la CPU

Ejemplos de planificacin:

Multitarea cooperativa: Windows 3.x Multitarea expulsiva o apropiativa: Windows 2k

Planificacin del procesador

Concepto de planificacin (ii)

Estados de un proceso

Cola de listos

CPU

E/S

Cola de E/S

E/S

Cola de E/S

E/S

Cola de E/S

Planificacin del procesador

Concepto de planificacin (iii)

Planificador / Dispatcher

Planificador o scheduler: Determina en quin es el siguiente proceso en hacer uso de la CPU Dispatcher o repartidor: Conmuta el procesador de un trabajo a otro

Cambio de contexto Ejecuta el proceso durante un momento Salva el estado del proceso en el BCP

CP

Flags de estado

Registros de propsito general Registros de operaciones en coma flotante Informacin relativa a la memoria: punteros a las tablas de pginas, punteros a las tablas de segmentos, TLB, etc.

Restaura el estado de otro proceso Transfiere el control al nuevo proceso

Planificacin del procesador

5

Concepto de planificacin (iv)

Proceso 1

En ejecucin

Interrupcin o llamada al sistema

Sistema operativo

Dispatcher Dispatcher

Proceso 2

Planificador

Listo

Listo

Dispatcher Dispatcher

En ejecucin

Interrupcin o llamada al sistema

Planificador

En ejecucin

Listo

Planificador

Dispatcher

polticas mecanismos

Planificacin del procesador

Concepto de planificacin (v)

Planificadores

Planificador a largo plazo

Carga del proceso en memoria Controla el grado de multiprogramacin

Planificador a corto plazo

Selecciona entre los trabajos cargados en memoria y que estn listos para ejecutarse, cul har uso del procesador Debe ser muy rpido ya que entra en juego con una frecuencia muy alta

Planificador a medio plazo

Carga y descarga trabajos (swap in-out) desde el disco a la memoria y de la memoria al disco en funcin del grado de sobrecarga del sistema

Planificacin del procesador

Algoritmos de planificacin (i)

Criterios de evaluacin

Grado de utilizacin del procesador Rendimiento (Throughput)

Trabajos completados por unidad de tiempo

Tiempo de estancia (Turnaround time)

Tiempo transcurrido desde que se lanza hasta que finaliza

Tiempo de espera

Tiempo que est un proceso en una cola (no ejecucin)

Tiempo de respuesta

Importante en aplicaciones interactivas o de tiempo real (hasta la 1 respuesta del sistema)

Grado de sobrecarga

Recursos que emplea el planificador: tiempo de procesador y memoria

Planificacin del procesador

8

Algoritmos de planificacin (ii)

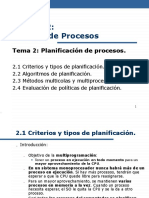

Planificacin Planificacin Planificacin Planificacin Planificacin Planificacin

FIFO primero el ms corto por prioridades

round robin

con colas multinivel con colas multinivel realimentadas

Planificacin del procesador

Planificacin FIFO (i)

FIFO: First in first out primero en entrar, primero en salir Gestiona la cola de procesos listos como una cola FIFO Ventaja:

Es el algoritmo ms sencillo de codificar

Inconveniente:

Un proceso puede monopolizar la CPU efecto convoy Depende fuertemente de los tipos de trabajo y del instante en que llegan

Ejemplo:

T1: 12 u.t., T2: 3 u.t., T3: 6 u.t. T1: 100 u.t., T2: 1 u.t., T3: 1 u.t., T4: 1 u.t.

Planificacin del procesador

10

Planificacin FIFO (ii)

Ejemplo FIFO

Caso 1:

Trabajo 1 0 Trabajo 2 12 15 Trabajo 3 21

Caso 2:

Trabajo 2 0 3 Trabajo 3 9 Trabajo 1 21

Los tiempos medios de respuesta varan dependiendo de cmo se encolen los trabajos

Caso 1: t Caso 2: t = 16 respuesta = 11

respuesta

Planificacin del procesador

11

Planificacin FIFO (iii)

Ejemplo FIFO

Caso 1: Efecto convoy

Trabajo 1 0 T2 T3 T4 100 101 102 103

Caso 2:

T2 T3 T4 0 1 2 3 Trabajo 1 103

Los tiempos medios de respuesta varan dependiendo de cmo se encolen los trabajos

Caso 1: t Caso 2: t = 101,5 u.t. respuesta = 27,25 u.t.

respuesta

Planificacin del procesador

12

Planificacin SJF (i)

SJF: shortest job first primero el ms corto Asigna la CPU al trabajo con la siguiente rfaga ms pequea Calcula, de forma dinmica, la longitud de la siguiente rfaga de CPU para cada proceso Ventaja:

Reduce los tiempos medios de respuesta

Inconveniente:

Conocer cules van a ser las duraciones de las prximas rfagas de CPU de cada proceso Produce inanicin en procesos con rfagas largas

Planificacin del procesador

13

Planificacin SJF (ii)

Mtodo de prediccin

La siguiente rfaga de CPU se predice como una media exponencial de las longitudes medias en anteriores rfagas n+1 = tn + (1-) n Sea:

tn: longitud de la n-sima rfaga de CPU n: valor predicho para la n-sima rfaga de CPU : parmetro de ajuste tn: contiene la informacin ms reciente n: contiene la historia pasada

Ejemplo:

T1: 3 u.t., T2: 12 u.t., T3: 7 u.t., T4: 5 u.t. t respuesta = 13,25 u.t.

Planificacin del procesador

14

Planificacin con prioridades

Se asigna la CPU al trabajo con la prioridad ms alta Las prioridades pueden definirse:

Internamente: Segn los requisitos del SO

Tiempo de CPU, memoria usada, recursos empleados, etc.

Externamente: Requisitos ajenos al SO

Tipo de usuario, tipo de aplicacin, etc.

Estticas: No vara durante la vida del proceso Dinmicas: Vara a lo largo de la vida del proceso, dependiendo de las decisiones del planificador

Inconveniente:

Produce inanicin en procesos de baja prioridad Solucin: Utilizar envejecimiento

Planificacin del procesador

15

Planificacin con requisa

En los algoritmos anteriores, un proceso usa la CPU hasta pedir una E/S o terminar monopolizar la CPU Solucin: Un proceso puede desalojar al que usa la CPU Algoritmos con requisa (preemption):

SJF con requisa Prioridades con requisa

Ejemplo: SJF con requisa

T1: t = 0, 8 u.t. T2: t = 3, 4 u.t. T3: t = 2, 11 u.t.

Trabajo 1 Trabajo 2 0 3 7 Trabajo 1 12

Planificacin del procesador

Trabajo 3 23

16

Planificacin round-robin (i)

Planificacin por turno rotatorio La CPU se asigna a cada proceso listo durante un cuanto de tiempo q

Evita la monopolizacin de uso de CPU En sistemas de tiempo compartido

La cola de procesos preparados es FIFO Si la rfaga de CPU > q Interrupcin TIME-OUT Si la rfaga de CPU < q Liberacin de CPU Prestaciones: dependen fuertemente de q q round-robin degenera en FCFS q 0 CPU/n n es el nmero de procesos listos

Planificacin del procesador

17

Planificacin round-robin (ii)

Si q es muy pequeo se pierde mucho tiempo en el cambio de contexto. Disminuye la eficacia del procesador Si q es grande los tiempos de respuesta aumentan Regla emprica:

El 80% de las rfagas de CPU deben ser menores que el cuanto

Problema:

Slo existe una cola de trabajos preparados, no distingue entre tipos de trabajos

Planificacin del procesador

18

Planificacin con colas multinivel (i)

Objetivo: Diferenciar entre distintos tipos de trabajos Existen colas separadas en funcin del tipo de trabajo Cada cola tiene su propio algoritmo de planificacin Debe existir otro algoritmo para elegir la cola en cada momento

Prioridad alta Tareas del sistema Tareas interactivas Tareas de edicin Prioridad baja Tareas batch

Planificacin del procesador

19

Planificacin con colas multinivel (ii)

Colas multinivel realimentadas

Tcnicas adaptativas

Los trabajos cambian de prioridad y de cola

Consideraciones:

El algoritmo de planificacin de cada cola Mtodos para ascender y descender entre colas Dnde poner inicialmente a los trabajos

+ Prioridad

Tareas de TR Quantum = 10 Quantum = 20 FCFS

Planificacin del procesador

20

10

Planificacin en VAX/VMS (i)

Caractersticas:

Entorno multiusuario Tiempo compartido Aplicaciones interactivas Planificacin de procesos

Planificacin con prioridades [0 31] y desalojo Procesos de usuario [0 15] : Prioridad base fija + offset

Offset: hasta 6 niveles sobre la prioridad base

Se beneficia a las tareas limitadas por E/S

Procesos de tiempo real [16 31] :

Su prioridad no suele cambiar

Planificacin del procesador

21

Planificacin en VAX/VMS (ii)

+

31

...

16 15

Tareas de tiempo real

...

Tareas ordinarias

Cont. W2K

Planificacin del procesador

22

11

Planificacin en UNIX 4.4 BSD (i)

Caractersticas:

Entorno multiusuario Tiempo compartido Aplicaciones interactivas Planificacin de procesos

Planificacin con prioridades dinmicas [127 0] y desalojo

Procesos en modo supervisor [49 0] Procesos en modo usuario [127 50]

Existen 32 colas

Cola Prioridad / 4 q = 0,1 s

Planificacin del procesador

23

Planificacin en UNIX 4.4 BSD (ii)

Estructuras de datos

whichqs 0 0 1 0 1 qs Cola 0 Cola 1 Cola 2 Cola 3 Cola 4 Prio. 0-3 Prio. 4-7 Prio. 8-11 Prio. 12-15 Prio. 16-19 ... Cola 31 Prio. 124-127 Proc Proc Proc Proc Proc ... Indica qu cola contiene procesos listos

Planificacin del procesador

24

12

Planificacin en UNIX 4.4 BSD (iii)

Estructuras de datos

Estructura proc:

p_usrpri p_estcpu p_nice p_slptime Prioridad en modo usuario Tiempo de procesador acumulado Definido por el usuario [-20 +20] Tiempo bloqueado por algn evento

1 tick = 10 ms. Interrupciones de un reloj hardware

Planificacin del procesador

25

Planificacin en UNIX 4.4 BSD (iv)

Clculo de prioridades

hardclock()

Incrementa el valor de p_estcpu del proceso activo hasta un mximo de 127 cada 1 tick

setpriority()

Recalcula la prioridad de cada proceso cada 4 ticks: p_usrpri = PUSER + (p_estcpu/4) + 2p_nice

schedcpu()

Recalcula las prioridades cada 1 s: p_estcpu = decay p_estcpu + p_nice (decrementa p_estcpu) donde: decay = 2 carga / (2 carga) + 1 p_estcpu = decayp_slptime p_estcpu

roundrobin() conmuta el procesador cada 100 ms

Planificacin del procesador

26

13

Planificacin en W2K (i)

Caractersticas:

Entorno monousuario Tiempo compartido Aplicaciones interactivas o como servidor Planificacin de hilos

Planificacin apropiativa con prioridades [031]

Tareas de tiempo real [16 31] Tareas ordinarias [1 15] Prioridades dinmicas: base + offset Prioridad 0: Zero page thread

Proceso inactivo del sistema

Colas VAX/VMS

Planificacin del procesador

27

Planificacin en W2K (ii)

Quantum

1 tick:

q=q3 10 ms en sistemas monoprocesador i80x86 15 ms en sistemas multiprocesador i80x86

W2K Professional:

6 unidades lgicas 2 ticks 20 ms Interactividad, tiempo de respuesta ms bajo

W2K Server:

36 unidades lgicas Mejor rendimiento 12 ticks 120 ms

Listo Ejecucin

Ensanchamiento de q:

W2K professional Valores: 6, 4 2 ticks Mejora tiempo de respuesta Aplicable a la tarea que se ejecuta en 1er. plano

Planificacin del procesador

28

14

Planificacin en W2K (iii)

El planificador se activa, cuando un hilo:

Abandona el estado de ejecucin porque acaba su q, pasa al estado de espera o finaliza su ejecucin Pasa al estado de listo porque acaba de ser creado o finaliza una operacin de E/S Cambia de prioridad de forma implcita definida por el SO o de forma explcita definida pro el programador Cambia la afinidad de procesador

Terminado Ejecucin Espera Transicin Listo

Planificacin del procesador

29

Standby

Planificacin en W2K (iv)

Escenarios de planificacin

Conmutacin voluntaria

El hilo en ejecucin pasa al estado de espera Se elige el 1er. trabajo de la cola de mayor prioridad

Listo Ejecucin

Finalizacin del quantum

Si la prioridad del hilo es la prioridad base

Espera

Si ha habido aumento de prioridad (no en tareas de TR)

Planificacin del procesador

30

15

Planificacin en W2K (v)

Escenarios de planificacin

Requisa

Si pasa al estado de listo un hilo de mayor prioridad que el que est en ejecucin Existe requisa para hilos en modo ncleo, si IRLQ <=2

Listo despus de una espera

Si pasa al estado de listo un hilo de menor prioridad que el que est en ejecucin

Planificacin del procesador

31

Planificacin en W2K (vi)

Ajuste de prioridad en W2K

Beneficia a tareas interactivas, frente a las de uso intensivo de CPU Priority boosting y priority decay:

Se aplica a la prioridad base de hilos ordinarios prioridad base <= prioridad obtenida <= 15

Decay:

Si un hilo agota su quantum -1

Planificacin del procesador

32

16

Planificacin en W2K (vii)

Ajuste de prioridad en W2K

Boost:

Fin de E/S, especificado por el device driver

Disco, CD-ROM, tarjeta grfica, pto. paralelo Red, pto. serie, tubera con nombre +2 Teclado y ratn +6 Tarjeta sonido +8 +1

Fin de espera por eventos o semforos: +1 La tarea de primer plano finaliza una espera: +2 Se despierta una tareas GUI: +2

Sobre la prioridad actual

Cada 1s. se activa Balance Set Manager

Evita inanicin de hasta 16 hilos con ms de 300 ticks sin ejecutarse Prioridad 16 boost +10 y 2 * quantum

Planificacin del procesador

33

Planificacin en W2K (viii)

Ajuste de prioridad en W2K

Prioridad

Decay

Boost

Apropiacin

Prioridad base Ejecucin Espera Ejecucin Listo Ejecucin

Tiempo

Planificacin del procesador

34

17

You might also like

- UF0852 - Instalación y actualización de sistemas operativosFrom EverandUF0852 - Instalación y actualización de sistemas operativosRating: 5 out of 5 stars5/5 (1)

- Practico 3Document8 pagesPractico 3Diana Parra SalazarNo ratings yet

- Problemas Escogidos SODocument33 pagesProblemas Escogidos SOebolanoskaNo ratings yet

- Introducción a los Algoritmos y las Estructuras de Datos 3: Introducción a los Algoritmos y las Estructuras de Datos, #3From EverandIntroducción a los Algoritmos y las Estructuras de Datos 3: Introducción a los Algoritmos y las Estructuras de Datos, #3No ratings yet

- 04 Procesos PlanificacionDocument94 pages04 Procesos PlanificacionovmlcabreraNo ratings yet

- Algoritmos PlanificadorDocument109 pagesAlgoritmos PlanificadorRigs JuarezNo ratings yet

- Practico3 2018Document5 pagesPractico3 2018davidNo ratings yet

- Planificacion de CpuDocument48 pagesPlanificacion de CpuNailiz BetancourtNo ratings yet

- Capitulo2 IS11Document19 pagesCapitulo2 IS11rammsterNo ratings yet

- 2022 SO - Planificación CPU (Cap.5 - Silberschatz 10ma Ed.) (T)Document25 pages2022 SO - Planificación CPU (Cap.5 - Silberschatz 10ma Ed.) (T)Daniela Luján FacalNo ratings yet

- SO_2.1_PlanificacionDeProcesosDocument33 pagesSO_2.1_PlanificacionDeProcesosjonathanjgb3No ratings yet

- Practico 3Document5 pagesPractico 3José Luis Martínez HernándezNo ratings yet

- UNIDAD III Cap 4 Admon Del ProcesadorDocument46 pagesUNIDAD III Cap 4 Admon Del ProcesadorElocoNo ratings yet

- Sist Operativo3Document16 pagesSist Operativo3Luis SantamariaNo ratings yet

- CuadernillodeTrabajosPracticos UltimoDocument19 pagesCuadernillodeTrabajosPracticos UltimoStepan Sergeivich MelnikovNo ratings yet

- Planificacion de ProcesosDocument25 pagesPlanificacion de ProcesosAurelio RicoNo ratings yet

- Presentacion PlanificacionDocument30 pagesPresentacion Planificacionangie andreaNo ratings yet

- S03.s5 - Algoritmos de Planificación - Parte 1Document36 pagesS03.s5 - Algoritmos de Planificación - Parte 1Sebastian Villar SeguraNo ratings yet

- Programación de operaciones y control de producciónDocument59 pagesProgramación de operaciones y control de producciónMari RiveraNo ratings yet

- PlanificacionDocument48 pagesPlanificacionKa GiaNo ratings yet

- 02-Administración Del ProcesadorDocument33 pages02-Administración Del ProcesadorSlyferNo ratings yet

- Consulta Algoritmos PlanificacionDocument3 pagesConsulta Algoritmos PlanificacionAntonio ZambranoNo ratings yet

- Capitulo 4 - PlanificaciónDocument14 pagesCapitulo 4 - PlanificaciónAlexander SaavedraNo ratings yet

- Administración Del Procesador (Scheduling) - Universidad Católica Andrés BelloDocument48 pagesAdministración Del Procesador (Scheduling) - Universidad Católica Andrés Bellodarioleonz0% (1)

- Planificacion de Procesos Sistemas OperativosDocument12 pagesPlanificacion de Procesos Sistemas OperativosArtuto LeyvaNo ratings yet

- Algoritmos de Planificación:: Sistemas Operativos Windows y Unix/LinuxDocument8 pagesAlgoritmos de Planificación:: Sistemas Operativos Windows y Unix/LinuxJorge Sari Di FabioNo ratings yet

- Administracion de Procesos NEWDocument68 pagesAdministracion de Procesos NEWWilkier RosalesNo ratings yet

- TrabajosPracticos Sistema OperativoDocument19 pagesTrabajosPracticos Sistema OperativoDanielNo ratings yet

- 8 Arquitectura SoDocument41 pages8 Arquitectura SoAlfredo Alexis Arevalo VenegasNo ratings yet

- Planificación de procesos en SO: políticas y algoritmosDocument23 pagesPlanificación de procesos en SO: políticas y algoritmoschechejgvNo ratings yet

- Procesos Hilos Planificación Práctico 2Document3 pagesProcesos Hilos Planificación Práctico 2jkNo ratings yet

- PA2 Sistemas OperativosDocument11 pagesPA2 Sistemas Operativosjuan carlos hernandez paredezNo ratings yet

- Planificacion Del ProcesadorDocument51 pagesPlanificacion Del ProcesadorAaron Hernan Chilin ValleNo ratings yet

- (800832256) Tp1-So2016Document7 pages(800832256) Tp1-So2016Mauro MachadoNo ratings yet

- Planificacion Procesos 2aDocument21 pagesPlanificacion Procesos 2amanuel alexander vasquez rafaelanoNo ratings yet

- Tema4. Planificación - 2020Document29 pagesTema4. Planificación - 2020Ayman MejradiNo ratings yet

- Sistemas Operativos - Ejercicios de Planificación de ProcesosDocument60 pagesSistemas Operativos - Ejercicios de Planificación de ProcesosRubén Senzano OvandoNo ratings yet

- ExplicaciónDocument43 pagesExplicaciónseba.cris.lp.97No ratings yet

- Examen BelénMiranda BryamLópezDocument10 pagesExamen BelénMiranda BryamLópezBryam LópezNo ratings yet

- ArqComp t1 PmaDocument11 pagesArqComp t1 PmaMauricio Arguello SolanoNo ratings yet

- Planificación de La CPUDocument5 pagesPlanificación de La CPUAnderson JordanNo ratings yet

- Planificacion de ProcesosDocument32 pagesPlanificacion de ProcesosJesús Marín HernándezNo ratings yet

- AlgoritmosPlanificacionCPUMaximizarUtilizacionDocument13 pagesAlgoritmosPlanificacionCPUMaximizarUtilizacionCamila LopezNo ratings yet

- Rendimiento CpuDocument77 pagesRendimiento CpuJuan Marcelo Cortez GutiérrezNo ratings yet

- S04.s4 - Material PDFDocument28 pagesS04.s4 - Material PDFAlbert RomeroNo ratings yet

- Planificación Del ProcesadorDocument28 pagesPlanificación Del ProcesadorccoyocNo ratings yet

- SO-Planificador-CFSDocument25 pagesSO-Planificador-CFSJesús CarvajalNo ratings yet

- Algoritmo de PlanificacionDocument10 pagesAlgoritmo de PlanificacionGerard AntonyNo ratings yet

- Planeación de ProcesosDocument7 pagesPlaneación de ProcesosjosemanuelmachaNo ratings yet

- Planificación CPU PDFDocument34 pagesPlanificación CPU PDFRodrigo HigueraNo ratings yet

- SO Teo PlanificacionDocument28 pagesSO Teo PlanificacionMaria Magdalena Navarro CamachoNo ratings yet

- Gestion de ProcesosDocument31 pagesGestion de ProcesosKevin BanegasNo ratings yet

- Problemas de Planificación de ProcesosDocument9 pagesProblemas de Planificación de ProcesosRaymundo Cruz ToledoNo ratings yet

- Algoritmos de PlanificaciónDocument8 pagesAlgoritmos de PlanificaciónBorja Rey SeoaneNo ratings yet

- QuishpeG Practica2Document2 pagesQuishpeG Practica2MATTHEUS QUISHPENo ratings yet

- Gestión de procesos y algoritmos de planificación en SODocument27 pagesGestión de procesos y algoritmos de planificación en SOJose LuisNo ratings yet

- Algoritmos de Planificacion No ExpulsivosDocument11 pagesAlgoritmos de Planificacion No ExpulsivosLuis Manuel Bravo AgüeroNo ratings yet

- Ejercicio Gestión Procesos 1Document3 pagesEjercicio Gestión Procesos 1Edgar OrtizNo ratings yet

- Programacion de OperacionesDocument49 pagesProgramacion de OperacionesNina DavisNo ratings yet

- CodeIgniter 3 1 9 Manual Esp PDFDocument572 pagesCodeIgniter 3 1 9 Manual Esp PDFingjlaNo ratings yet

- ITA3 PRHDocument5 pagesITA3 PRHCristian Llanes VillagraNo ratings yet

- InformaticaDocument6 pagesInformaticaCristian Llanes VillagraNo ratings yet

- DataDocument2 pagesDataCristian Llanes VillagraNo ratings yet

- Plansqa JavaDocument8 pagesPlansqa Javagenscrib75No ratings yet

- CapitulaDocument10 pagesCapitulaCristian Llanes VillagraNo ratings yet

- Intro Ducci OnDocument6 pagesIntro Ducci OnCristian Llanes VillagraNo ratings yet

- PDFDocument12 pagesPDFCristian Llanes VillagraNo ratings yet

- Intro Ducci OnDocument6 pagesIntro Ducci OnCristian Llanes VillagraNo ratings yet

- c39 TungDocument1 pagec39 TungCristian Llanes VillagraNo ratings yet

- PHPExcel Developer DocumentationDocument3 pagesPHPExcel Developer DocumentationCristian Llanes VillagraNo ratings yet

- Unidad II. - Metricas de La Calidad Del SWDocument31 pagesUnidad II. - Metricas de La Calidad Del SWCristian Llanes VillagraNo ratings yet

- Botanica Gral IIDocument1 pageBotanica Gral IICristian Llanes VillagraNo ratings yet

- LeyesDocument7 pagesLeyesCristian Llanes VillagraNo ratings yet

- Balance - 2016 12 06Document2 pagesBalance - 2016 12 06Cristian Llanes VillagraNo ratings yet

- Guia Sqpa 1 0Document30 pagesGuia Sqpa 1 0Cristian Llanes VillagraNo ratings yet

- Analisis DiseñoDocument3 pagesAnalisis DiseñoCristian Llanes VillagraNo ratings yet

- Informe de AvanceDocument6 pagesInforme de AvanceCristian Llanes VillagraNo ratings yet

- Gestión de Procesos de Desarrollo de Software Con Herramientas ALM PDFDocument26 pagesGestión de Procesos de Desarrollo de Software Con Herramientas ALM PDFCristian Llanes VillagraNo ratings yet

- Cf-Riquelme RT PDFDocument63 pagesCf-Riquelme RT PDFCristian Llanes VillagraNo ratings yet

- 1.2 Manifiesto Agil PDFDocument13 pages1.2 Manifiesto Agil PDFCristian Llanes VillagraNo ratings yet

- Plan de CalidadDocument21 pagesPlan de CalidadCristian Llanes VillagraNo ratings yet

- Clase 1Document34 pagesClase 1Cristian Llanes VillagraNo ratings yet

- Manual PHP5 BasicoDocument180 pagesManual PHP5 Basicozerojohnsoft100% (1)

- WebDocument76 pagesWebLuis GomezNo ratings yet

- Ing SoftwDocument74 pagesIng SoftwraulNo ratings yet

- Code IgniterDocument21 pagesCode IgniterJuan Diaz del VallinNo ratings yet

- Agile RoadmapDocument105 pagesAgile RoadmapJuan Francisco Salinas AedoNo ratings yet

- LeliaDocument12 pagesLeliaCristian Llanes VillagraNo ratings yet

- Es Intro KanbanDocument7 pagesEs Intro KanbanWilber Sierra Motta de RamosNo ratings yet

- Entrega 1Document15 pagesEntrega 1jose david laverde alvaradoNo ratings yet

- Humanware, Hardware y SoftwareDocument2 pagesHumanware, Hardware y SoftwareNinja_ZeroNo ratings yet

- 04 3 PRESENTACION Aplicaciones de HardeningDocument17 pages04 3 PRESENTACION Aplicaciones de HardeningdanielNo ratings yet

- Curriculum Jose Manuel Martinez MejiaDocument3 pagesCurriculum Jose Manuel Martinez MejiaJose Manuel MartinezNo ratings yet

- Crear USB booteable Windows 7Document17 pagesCrear USB booteable Windows 7Gustavo Adolfo Tafur ValeraNo ratings yet

- Tipos de Restricciones o Constraints en SQL ServerDocument3 pagesTipos de Restricciones o Constraints en SQL Serveromar marriaga SystemNo ratings yet

- Informe de prácticas en Carbones del CerrejónDocument54 pagesInforme de prácticas en Carbones del Cerrejónjuan carlos dazaNo ratings yet

- Términos de Referencia: Gobierno Autónomo Descentralizado Municipal Del Cantón MantaDocument5 pagesTérminos de Referencia: Gobierno Autónomo Descentralizado Municipal Del Cantón MantaDiego TejadaNo ratings yet

- Caso Practico 2 SimulacionDocument9 pagesCaso Practico 2 SimulacionLuis AlvarezNo ratings yet

- Aws OverviewDocument93 pagesAws OverviewSamuel RománNo ratings yet

- Sap AbapDocument2 pagesSap AbapHugo Armando Cervantes HernandezNo ratings yet

- Hoja de Vida JROV Jun2011Document9 pagesHoja de Vida JROV Jun2011Julio Roberto Otálora VargasNo ratings yet

- Análisis de Capítulo 13Document5 pagesAnálisis de Capítulo 13Jerrick Simití100% (1)

- Evaluacion N°3 - Sistemas Electrohidraulicos BDocument2 pagesEvaluacion N°3 - Sistemas Electrohidraulicos BRodrigo NavarroNo ratings yet

- Cuestionario Auditoria en SistemasDocument2 pagesCuestionario Auditoria en SistemasJorge CastilloNo ratings yet

- Word WallDocument2 pagesWord WallDario MaNo ratings yet

- Introduccion A La Metodología RUPDocument14 pagesIntroduccion A La Metodología RUPdlujane0% (1)

- SOMTarea Presencial2.1.Document4 pagesSOMTarea Presencial2.1.Silvia Zenteno0% (1)

- Universidad de El Salvador RR 16116 Laboratorio 2 Logica y LogaritmoDocument13 pagesUniversidad de El Salvador RR 16116 Laboratorio 2 Logica y LogaritmoJose Daniel Ruiz100% (1)

- ES How To Format A Grab'n'GO Hard DiskDocument25 pagesES How To Format A Grab'n'GO Hard DiskRaul Exposito CarmonaNo ratings yet

- NOMINADocument29 pagesNOMINAKarla DUNo ratings yet

- Integración web y arquitectura informaciónDocument16 pagesIntegración web y arquitectura informaciónjanet lopezNo ratings yet

- Crea cuenta gratis Logbook of the WorldDocument29 pagesCrea cuenta gratis Logbook of the Worldoscar tebarNo ratings yet

- Apuntes Css y DivsDocument81 pagesApuntes Css y DivsAlfredo GonzalezNo ratings yet

- Manual de SysprepDocument12 pagesManual de Sysprepluis_020_913056No ratings yet

- IDESF QGIS Primeros PasosDocument10 pagesIDESF QGIS Primeros Pasosignacio vinconNo ratings yet

- Glosario Normatividad SNIEGDocument12 pagesGlosario Normatividad SNIEGSTEPHANIE ELIZABETH MEDINA PONCENo ratings yet

- Adso Diseño de Fichas Tecnicas para La Recolecdion de Informacion Ga2-220501094.aa1-Ev02Document6 pagesAdso Diseño de Fichas Tecnicas para La Recolecdion de Informacion Ga2-220501094.aa1-Ev02josemontero8401No ratings yet

- Unidad de Aprendizaje - Lenguaje de Programación JavaDocument44 pagesUnidad de Aprendizaje - Lenguaje de Programación JavalubicanNo ratings yet

- Invitacion Cotizar Vanessa CaamañoDocument4 pagesInvitacion Cotizar Vanessa CaamañoVanessa CaamañoNo ratings yet