Professional Documents

Culture Documents

Lecture3 20120325 165942

Uploaded by

iamumpidiOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lecture3 20120325 165942

Uploaded by

iamumpidiCopyright:

Available Formats

Datorarkitektur

F 3 - 1

Datorarkitektur

F 3 - 2

The Instruction Cycle

INSTRUCTION PIPELINING (I)

Fetch instruction 1. The Instruction Cycle Decode 2. Instruction Pipelining 3. Pipeline Hazards 4. Structural Hazards 5. Data Hazards 6. Control Hazards Execute instruction - Execute instruction (EI) - Write back operand (WO) Fetch operand - Calculate operand address (CO) - Fetch operand (FO) DI FI

Petru Eles, IDA, LiTH

Petru Eles, IDA, LiTH

Datorarkitektur

F 3 - 3

Datorarkitektur

F 3 - 4

Instruction Pipelining

Instruction execution is extremely complex and involves several operations which are executed successively (see slide 2). This implies a large amount of hardware, but only one part of this hardware works at a given moment.

Acceleration by Pipelining Two stage pipeline: Clock cycle Instr. i Instr. i+1 FI: fetch instruction EI: execute instruction 1 2 3 4 5 6 7 8 FI EI FI EI FI EI FI EI FI EI FI EI FI EI

Pipelining is an implementation technique whereby multiple instructions are overlapped in execution. This is solved without additional hardware but only by letting different parts of the hardware work for different instructions at the same time. The pipeline organization of a CPU is similar to an assembly line: the work to be done in an instruction is broken into smaller steps (pieces), each of which takes a fraction of the time needed to complete the entire instruction. Each of these steps is a pipe stage (or a pipe segment). Pipe stages are connected to form a pipe: Stage 1 Stage 2 Stage n

Instr. i+2 Instr. i+3 Instr. i+4 Instr. i+5 Instr. i+6

We consider that each instruction takes execution time Tex. Execution time for the 7 instructions, with pipelining: (Tex/2)*8= 4*Tex

The time required for moving an instruction from one stage to the next: a machine cycle (often this is one clock cycle). The execution of one instruction takes several machine cycles as it passes through the pipeline.

Petru Eles, IDA, LiTH

Petru Eles, IDA, LiTH

Datorarkitektur

F 3 - 5

Datorarkitektur

F 3 - 6

Acceleration by Pipelining (contd) Acceleration by Pipelining (contd) Six stage pipeline (see also slide 2): FI: fetch instruction FO: fetch operand DI: decode instruction EI: execute instruction CO: calculate operand address WO:write operand Clock cycle Instr. i Instr. i+1 Instr. i+2 Instr. i+3 Instr. i+4 Instr. i+5 Instr. i+6 1 2 3 4 5 6 7 8 9 10 11 12

FI DI COFO EI WO FI DI COFO EI WO FI DI COFO EI WO FI DI COFO EI WO FI DI COFO EI WO FI DI COFO EI WO FI DI COFO EI WO

Apparently a greater number of stages always provides better performance. However: - a greater number of stages increases the overhead in moving information between stages and synchronization between stages. - with the number of stages the complexity of the CPU grows. - it is difcult to keep a large pipeline at maximum rate because of pipeline hazards. five-stage pipeline for integer instr. eight-stage pipeline for FP instr. four-stage pipeline for integer instr. six-stage pipeline for FP instr.

80486 and Pentium: PowerPC:

Execution time for the 7 instructions, with pipelining: (Tex/6)*12= 2*Tex After a certain time (N-1 cycles) all the N stages of the pipeline are working: the pipeline is lled. Now, theoretically, the pipeline works providing maximal parallelism (N instructions are active simultaneously).

Petru Eles, IDA, LiTH

Petru Eles, IDA, LiTH

Datorarkitektur

F 3 - 7

Datorarkitektur

F 3 - 8

Pipeline Hazards

Pipeline hazards are situations that prevent the next instruction in the instruction stream from executing during its designated clock cycle. The instruction is said to be stalled. When an instruction is stalled, all instructions later in the pipeline than the stalled instruction are also stalled. Instructions earlier than the stalled one can continue. No new instructions are fetched during the stall.

Structural Hazards

Structural hazards occur when a certain resource (memory, functional unit) is requested by more than one instruction at the same time.

Instruction ADD R4,X fetches in the FO stage operand X from memory. The memory doesnt accept another access during that cycle. Clock cycle ADD R4,X 1 2 3 4 5 6 7 8 9 10 11 12

FI DI COFO EI WO FI DI COFO EI WO FI DI COFO EI WO

stall

Types of hazards: 1. Structural hazards 2. Data hazards 3. Control hazards

Instr. i+1 Instr. i+2 Instr. i+3 Instr. i+4 Penalty: 1 cycle

FI DI COFO EI WO FI DI COFO EI WO

Certain resources are duplicated in order to avoid structural hazards. Functional units (ALU, FP unit) can be pipelined themselves in order to support several instructions at a time. A classical way to avoid hazards at memory access is by providing separate data and instruction caches.

Petru Eles, IDA, LiTH

Petru Eles, IDA, LiTH

Datorarkitektur

F 3 - 9

Datorarkitektur

F 3 - 10

Data Hazards

We have two instructions, I1 and I2. In a pipeline the execution of I2 can start before I1 has terminated. If in a certain stage of the pipeline, I2 needs the result produced by I1, but this result has not yet been generated, we have a data hazard. MUL ADD R2,R3 R1,R2 R2 R2 * R3 R1 R1 + R2

Data Hazards (contd) Some of the penalty produced by data hazards can be avoided using a technique called forwarding (bypassing). from reg- from register or ister or memory memory

I1: I2:

MUX bypass path ALU

MUX bypass path

Clock cycle MUL R2,R3 ADD R1,R2 Instr. i+2

1 2 3 4 5 6 7 8 9 10 11 12

FI DI COFO EI WO FI DI CO stall stall FO EI WO FI DI COFO EI WO

to register or memory The ALU result is always fed back to the ALU input. If the hardware detects that the value needed for the current operation is the one produced by the previous operation (but which has not yet been written back) it selects the forwarded result as the ALU input, instead of the value read from register or memory. 1 2 3 4 5 6 7 8 9 10 11 12

FI DI COFO EI WO FI DI CO stall FO EI WO

Before executing its FO stage, the ADD instruction is stalled until the MUL instruction has written the result into R2. Penalty: 2 cycles

Clock cycle MUL R2,R3 ADD R1,R2

After the EI stage of the MUL instruction the result is available by forwarding. The penalty is reduced to one cycle.

Petru Eles, IDA, LiTH

Petru Eles, IDA, LiTH

Datorarkitektur

F 3 - 11

Datorarkitektur

F 3 - 12

Control Hazards

Control hazards are produced by branch instructions.

Control Hazards (contd) Conditional branch ADD R1,R2 BEZ TARGET instruction i+1 ------------------------R1 R1 + R2 branch if zero

Unconditional branch -------------BR TARGET -------------TARGET -------------After the FO stage of the branch instruction the address of the target is known and it can be fetched Clock cycle BR TARGET target target+1 1 2 3 4 5 6 7 8 9 10 11 12

FI DI COFO EI WO FI

stall stall

TARGET Branch is taken

At this moment, both the condition (set by ADD) and the target address are known. Clock cycle ADD R1,R2 BEZ TARGET target Penalty: 3 cycles Branch not taken At this moment the condition is known and instr+1 can go on. Clock cycle ADD R1,R2 BEZ TARGET instr i+1 Penalty: 2 cycles 1 2 3 4 5 6 7 8 9 10 11 12

FI DI COFO EI WO FI DI COFO EI WO FI

stall stall

1 2 3 4 5 6 7 8 9 10 11 12

FI DI COFO EI WO FI DI COFO EI WO FI

stall stall

FI DI COFO EI WO

FI DI COFO EI WO FI DI COFO EI WO

The instruction following the branch is fetched; before the DI is nished it is not known that a branch is executed. Later the fetched instruction is discarded Penalty: 3 cycles

DI COFO EI WO

Petru Eles, IDA, LiTH

Petru Eles, IDA, LiTH

Datorarkitektur

F 3 - 13

Datorarkitektur

F 3 - 14

Summary

Control Hazards (contd) With conditional branch we have a penalty even if the branch has not been taken. This is because we have to wait until the branch condition is available.

Instructions are executed by the CPU as a sequence of steps. Instruction execution can be substantially accelerated by instruction pipelining. A pipeline is organized as a succession of N stages. At a certain moment N instructions can be active inside the pipeline. Keeping a pipeline at its maximal rate is prevented by pipeline hazards. Structural hazards are due to resource conicts. Data hazards are produced by data dependencies between instructions. Control hazards are produced as consequence of branch instructions

Branch instructions represent a major problem in assuring an optimal ow through the pipeline. Several approaches have been taken for reducing branch penalties (see slides of the following lecture).

Petru Eles, IDA, LiTH

Petru Eles, IDA, LiTH

You might also like

- Fundamentals of Computer Organization and ArchitectureFrom EverandFundamentals of Computer Organization and ArchitectureRating: 5 out of 5 stars5/5 (1)

- Lec3 PDFDocument15 pagesLec3 PDFRabia ChaudharyNo ratings yet

- Pipelining (All Slides)Document45 pagesPipelining (All Slides)NISHIT JAINNo ratings yet

- Pipelining: Mod I, Part IIIDocument39 pagesPipelining: Mod I, Part IIIann lynnNo ratings yet

- Computer Architecture Pipe LineDocument28 pagesComputer Architecture Pipe LineNAHID TECHNOLOGYNo ratings yet

- Pipelinehazard For ClassDocument61 pagesPipelinehazard For ClassJayanta SikdarNo ratings yet

- 第七章 PIPELININGDocument49 pages第七章 PIPELININGbill100% (1)

- Instruction Pipelining: 1 Zelalem Birhanu, AaitDocument20 pagesInstruction Pipelining: 1 Zelalem Birhanu, AaittesfuNo ratings yet

- Pipeline ProcessingDocument43 pagesPipeline ProcessingprabhakrishnanNo ratings yet

- Instruction Pipelining (Ii) : Reducing Pipeline Branch PenaltiesDocument5 pagesInstruction Pipelining (Ii) : Reducing Pipeline Branch PenaltiesvinnisharmaNo ratings yet

- Chapter 4 (Part II) The Processor: Datapath and Control: (Enhancing Performance With Pipelining)Document21 pagesChapter 4 (Part II) The Processor: Datapath and Control: (Enhancing Performance With Pipelining)許藝蓁No ratings yet

- L12 Pipelining 1Document31 pagesL12 Pipelining 1MD. JUWEL MALLICKNo ratings yet

- Comparison Between PipeliningDocument9 pagesComparison Between PipeliningBibek Ale MagarNo ratings yet

- Parallelism in Uniprocessor System and GranularityDocument5 pagesParallelism in Uniprocessor System and GranularityBravoYusuf100% (5)

- 4 Instruction PipelineDocument13 pages4 Instruction PipelineAKASH PALNo ratings yet

- 13054119-176 - Pipelining - Aqsa SaleemDocument21 pages13054119-176 - Pipelining - Aqsa SaleemMasoomBachiiNo ratings yet

- Session - 29 and 30 Instruction Pipelining and Pipeline Hazards, Instruction Level ParallelismDocument25 pagesSession - 29 and 30 Instruction Pipelining and Pipeline Hazards, Instruction Level ParallelismArnoldNo ratings yet

- PipeliningDocument10 pagesPipeliningyogesh deoNo ratings yet

- ILP-Architectures Part IIIDocument49 pagesILP-Architectures Part IIIYAAKOV SOLOMONNo ratings yet

- Week11 SlidesDocument49 pagesWeek11 SlidesVansh JainNo ratings yet

- Week 11 ReducedDocument29 pagesWeek 11 Reducedv69gnf5csyNo ratings yet

- Chapter6 Pipelining 141116000614 Conversion Gate01Document78 pagesChapter6 Pipelining 141116000614 Conversion Gate01Amit PanchalNo ratings yet

- Pipeline Very UsefulDocument8 pagesPipeline Very UsefulDinesh Kumara YapaNo ratings yet

- Microprocessors Piplining SlidesDocument38 pagesMicroprocessors Piplining SlidesHamza HassanNo ratings yet

- SuperscarlarDocument104 pagesSuperscarlarTang PisethNo ratings yet

- Chapter 6 PipeliningDocument58 pagesChapter 6 Pipeliningvinoliamanohar100% (1)

- Lecture 16Document21 pagesLecture 16ZainNo ratings yet

- Week 4 - PipeliningDocument44 pagesWeek 4 - Pipeliningdress dressNo ratings yet

- Module 5 - PipeliningDocument61 pagesModule 5 - Pipeliningsathishkumar.sNo ratings yet

- Coa Lecture Unit 3 PipeliningDocument95 pagesCoa Lecture Unit 3 PipeliningSumathy JayaramNo ratings yet

- Pipeline: A Simple Implementation of A RISC Instruction SetDocument16 pagesPipeline: A Simple Implementation of A RISC Instruction SetakhileshNo ratings yet

- Lecture 7 - PIPELININGDocument16 pagesLecture 7 - PIPELININGnoberth nikombolweNo ratings yet

- PipeliningDocument26 pagesPipeliningJayanta SikdarNo ratings yet

- Unit 3-2 COADocument58 pagesUnit 3-2 COAmy storiesNo ratings yet

- Chapter 8 - PipeliningDocument38 pagesChapter 8 - Pipeliningnagpal3No ratings yet

- Internal Structure of CPUDocument5 pagesInternal Structure of CPUSaad KhanNo ratings yet

- 4-PipelineDocument30 pages4-Pipelinesingaram112No ratings yet

- Pipelining 2Document16 pagesPipelining 2Kumar GagneshNo ratings yet

- Pipelining Pipelining Characteristics of Pipelining Clocks and Latches 5 Stages of Pipelining Hazards Loads / Stores Risc and CiscDocument12 pagesPipelining Pipelining Characteristics of Pipelining Clocks and Latches 5 Stages of Pipelining Hazards Loads / Stores Risc and CiscKelvinNo ratings yet

- Pipelining Basic Concepts: Instruction Fetch Execute Operand Fetch IF OF EXDocument28 pagesPipelining Basic Concepts: Instruction Fetch Execute Operand Fetch IF OF EXSyed AshmadNo ratings yet

- CH7-Parallel and Pipelined ProcessingDocument23 pagesCH7-Parallel and Pipelined Processingaashifr469No ratings yet

- SuperpipeliningDocument7 pagesSuperpipeliningBravoYusufNo ratings yet

- Chapter 6 - PipeliningDocument61 pagesChapter 6 - PipeliningShravani ShravzNo ratings yet

- Pipe Line1Document7 pagesPipe Line1midoNo ratings yet

- Chapter6 - PipeliningDocument61 pagesChapter6 - Pipeliningv69gnf5csyNo ratings yet

- L06 Arc DR Wail c4 PipeliningDocument168 pagesL06 Arc DR Wail c4 PipeliningtesfuNo ratings yet

- Pipelining SeminarDocument14 pagesPipelining SeminarDURAISAMYNo ratings yet

- Lec18 PipelineDocument59 pagesLec18 PipelineAliGhandiNo ratings yet

- Pipe LiningDocument16 pagesPipe LiningMUNEEBA GULNo ratings yet

- Chapt 02Document51 pagesChapt 02Kashif KhanNo ratings yet

- Instruction PipelineDocument16 pagesInstruction PipelineRamya RamasubramanianNo ratings yet

- SIMD Machines:: Pipeline SystemDocument35 pagesSIMD Machines:: Pipeline Systempssdk99hfdNo ratings yet

- Pipeline of 8086Document11 pagesPipeline of 8086A21 RUTUJA JAGTAPNo ratings yet

- Pipelining - Information Communication Technology ICTDocument13 pagesPipelining - Information Communication Technology ICTweeab postingNo ratings yet

- WINSEM2022-23 CSE4001 ETH VL2022230504003 Reference Material I 05-01-2023 M-2 2ILPDocument42 pagesWINSEM2022-23 CSE4001 ETH VL2022230504003 Reference Material I 05-01-2023 M-2 2ILPnehaNo ratings yet

- 8086 - PipeliningDocument3 pages8086 - PipeliningMovie DownloadNo ratings yet

- Lec3 1Document18 pagesLec3 1DaltonNo ratings yet

- Pipe LiningDocument29 pagesPipe LiningAnkitShingalaNo ratings yet

- NWIE RepairDocument29 pagesNWIE RepairNosaErnest50% (2)

- Pipeline HazardDocument4 pagesPipeline HazardMouli MandalNo ratings yet

- Eceg-4161.Chp.2. (Lec 1 of CHP 2)Document96 pagesEceg-4161.Chp.2. (Lec 1 of CHP 2)Natnail getachewNo ratings yet

- 8051 Instruction SetDocument47 pages8051 Instruction SetSanthosh CricketNo ratings yet

- MP-MC R16 - Unit-2Document56 pagesMP-MC R16 - Unit-2Vaishnavi. KoyaNo ratings yet

- AMP Lab ManualDocument22 pagesAMP Lab ManualSatish PawarNo ratings yet

- Logical OperatorsDocument23 pagesLogical OperatorsHadijaNo ratings yet

- ALP - Lab Manual 2023 - 24Document48 pagesALP - Lab Manual 2023 - 24rahul ghildiyal [fbking]No ratings yet

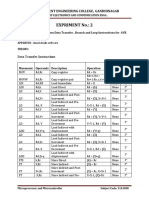

- Expriment No.: 2: Government Engineering College, GandhinagarDocument10 pagesExpriment No.: 2: Government Engineering College, GandhinagarDhrumil ManiyarNo ratings yet

- 8086 Alp Ppts-Modified 2022-23 BatchDocument63 pages8086 Alp Ppts-Modified 2022-23 BatchAshisha TulsianNo ratings yet

- Microprocessor Control Logic - 2: Load and Jump InstructionsDocument2 pagesMicroprocessor Control Logic - 2: Load and Jump InstructionsRaghav MaheswariNo ratings yet

- Instruction Set ArchitectureDocument61 pagesInstruction Set ArchitectureOlnes YosefaNo ratings yet

- Assignment 2Document7 pagesAssignment 2Muneeb Hassan SoomroNo ratings yet

- Chapter 3A PIC18 AssemblyLanguageProgrammingPartADocument75 pagesChapter 3A PIC18 AssemblyLanguageProgrammingPartAAndy WoNo ratings yet

- Computer Organization and Architecture: Sharmila ChidaravalliDocument102 pagesComputer Organization and Architecture: Sharmila ChidaravalliSharmila ChidaravalliNo ratings yet

- RPG Maker VX Ace Tutorial 9Document11 pagesRPG Maker VX Ace Tutorial 9Luis Júpiter Franco MartínezNo ratings yet

- Data Manipulation: Introduction To Computer ScienceDocument54 pagesData Manipulation: Introduction To Computer ScienceGiovana BogadoNo ratings yet

- The 8051 Microcontroller: Hsabaghianb at Kashanu - Ac.irDocument99 pagesThe 8051 Microcontroller: Hsabaghianb at Kashanu - Ac.irVinay ChowdaryNo ratings yet

- Chapter 08 - Msp430 IsaDocument62 pagesChapter 08 - Msp430 Isaokocha712No ratings yet

- Herbert Taub - Digital Circuits and Microprocessors-McGraw-Hill (1982)Document568 pagesHerbert Taub - Digital Circuits and Microprocessors-McGraw-Hill (1982)Jason Peters100% (4)

- Computer Organization Assembly Language: Prof. Muhammad SaeedDocument22 pagesComputer Organization Assembly Language: Prof. Muhammad SaeedAnam ManzoorNo ratings yet

- Q5 SolutionDocument1 pageQ5 Solutionapi-3801329No ratings yet

- DataPath DesignDocument23 pagesDataPath DesignOliver Barrina JaguinesNo ratings yet

- The CPU, Instruction Fetch & Execute: 2.1 A Bog Standard ArchitectureDocument15 pagesThe CPU, Instruction Fetch & Execute: 2.1 A Bog Standard ArchitectureRobert RobinsonNo ratings yet

- Operating Manual 280474Document221 pagesOperating Manual 280474Héctor Peláez García100% (3)

- Helping Slides Pipelining Hazards SolutionsDocument55 pagesHelping Slides Pipelining Hazards SolutionsA NNo ratings yet

- ES Lecture2 (ARM)Document19 pagesES Lecture2 (ARM)Rajneesh SharmaNo ratings yet

- MPI Lab ManualDocument103 pagesMPI Lab ManualVeerayya JavvajiNo ratings yet

- 8051 CH3 950217Document72 pages8051 CH3 950217Amardeep PotdarNo ratings yet

- Mcs 48Document72 pagesMcs 48Kartikeya SharmaNo ratings yet

- x8088/8086 Compare and Jump InstructionDocument30 pagesx8088/8086 Compare and Jump InstructionRuel Niño LapidezNo ratings yet

- Lecture 4 BSITDocument6 pagesLecture 4 BSITmu70832No ratings yet