Professional Documents

Culture Documents

2.9.4 Prácticas de Full-Custom

Uploaded by

Randy PumachaguaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

2.9.4 Prácticas de Full-Custom

Uploaded by

Randy PumachaguaCopyright:

Available Formats

PRACTICAS DE FULL-CUSTOM

JUAN LANCHARES DVILA

DEPARTAMENTO DE ARQUITECTURA DE COMPUTADORES Y AUTOMTICA

UNIVERSIDAD COMPLUTENSE DE MADRID

Practicas de diseo full-custom

1. LOGICA COMBINACIONAL ESTTICA

1.1 LGICA DE CARGA DINMICA 1.2 INVERSOR CMOS COMPLEMENTARIO

La lgica CMOS complementaria es la ms extendida en el diseo de circuitos integrados. Aproximadamente el 80% de los circuitos se disean con esta lgica. Los motivos por lo que esto es as son la robustez y el bajo consumo de potencia esttica. a.- Comprobar estos extremos diseando y simulando un inversor CMOS de lgica complementaria de tamaos mnimos. b.- En la simulacin anterior se puede comprobar que los tiempos de subida y de bajada del inversor no coinciden. Corrige el layout para que estos tiempos queden aproximadamente simtricos.

Practicas de diseo full-custom

1.2.1 PUERTA COMPLEJA CMOS COMPLEMENTARIA A) Implementa una puerta NAND de fan-in 4. (figura 1)

TN CL

I1 I2 In

Pull-up

T2

T1 > T2 > T3> T4 Vout

C2

I1 I2 In

Pull-down

T1

C1

Figura 1

Figura 2

B) En este tipo de puertas en las que existen mucho transistores en serie existe el problema del retardo que se genera. Para evitarlo se podran hacer los transistores serie ms anchos. El problema de esta solucin es el consumo de rea. La solucin ideal es aumentar el canal de los transistores progresivamente. Esta tcnica se describe en la pgina 197 de [Rabaey] y 290 de [weste] Weste indica que esta tcnica aplicada a tecnologas antiguas (es decir, tecnologas no submicra) puede conseguir mejoras entre el 20 y 30 de rendimiento. En cambio en tecnologas submicra no consigue mejoras superiores al 4%. Aplicarla a la puerta NAND diseada (figura 2). Para ello suponer que CL=2C y que C1=C2=C3=C4=C c) Por otro lado, el orden de llegada de las seales a las puertas puede afectar al rendimiento del sistema. Supn que llegan a la puerta NAND cuatro seales en tiempos diferentes. Busca cual ser el mejor orden de llegada de las seales y cual ser el peor orden de llegada.(figura3) Atencin: se debe tener cuidado al elegir el paso de simulacin.

I3 TN I1

CL

TN

CL

I2

T2

C2

I2

T2

C2

I1

T1

C1

I3

T1

C1

Practicas de diseo full-custom

Practicas de diseo full-custom

1.3 LGICA DE CARGA ESTTICA

1.3.1 LGICA PSEUDO NMOS A) Implementa una puerta NAND de cuatro entradas en lgica pseudonmos. B) Observa como se modifican los mrgenes de ruido de baja, los tiempos de subida y de bajada, el rea y el consumo de potencia cuando voy modificando los canales p desde su tamao mnimo a un tamao 8 veces el tamao mnimo. Supn los transistores N de tamao mnimo.

ENABLE

M1

M2

Pulldown

Figura X

Figura y

C) Como se ha podido comprobar en las simulaciones de la puerta ya vistas, los tiempos de subida de la seal son extremadamente largos comparados con los de bajada. Esto se debe a la gran capacidad que hay que cargar a la salida, sobre todo cuando se han escalado los transistores NMOS para conseguir buenos ceros lgicos. Esto se podra solucionar haciendo el transitor P ms grande pero entonces tendramos de nuevo un mal cero lgico, adems de un mayor consumo de potencia. Otra solucin es la que se presenta en la figura y. Se aade un transistor p controlado por una seal ck en paralelo al inicial. Este esquema es muy til para los decodificadores de memoria. A nosotros nos interesa que la seal que selecciona la palabra de memoria cambie muy rpidamente de 0 a 1 incluso a expensas de que se consuma mucha potencia. Una vez que la seal ya est a uno se desactiva la seal de reloj y el decodificador queda en una fase de standby. Esta seal de reloj se podra activar cuando variara la direccin a la que se desea accede.

Practicas de diseo full-custom

Practicas de diseo full-custom

1.3.2

DIFERENTIAL CASCADE VOLTAGE SWITCH ( DCVS )

Un tipo particular de carga esttica. Particularmente interesante para implementar puertas XOR como la de la figura. Su principal ventaja reside en generar las dos fases de la puerta y en que comparte lgica las dos ramas.

no tB

no tB

n otA

Practicas de diseo full-custom

Practicas de diseo full-custom

1.4 LGICA DE TRANSISTORES

A ) Implementa el circuito de la figura x. Comprueba que la seal de entrada se degenera en V1.qu cantidad se degenera y porque? aparece consumo de potencia esttica? Por qu? Modifica los potenciales umbrales e los p y de los n hasta conseguir que aparezca consumo de potencia esttica. Razonalo.

P1

VIN

V1

VIN

V1 VOUT

C Figura X

Figura y

B) Implementa la solucin al problema que aparece en la figura y. Realizar el diseo de manera que sea vlido tanto para Vin=0 como para el Vin=1. C) Implementar la misma funcin con puertas de transmisin y comparar resultados (Figura z).

notA notB notC

Vin

Vout

Practicas de diseo full-custom

10

Practicas de diseo full-custom

2. LGICA COMBINACIONAL DINMICA

2.1 LGICA DE PRECARGA Y EVALUACIN

CL

CL

F=(a+b)cd F=(a+b)cd

Figura a

Figura b

A) Implementa una funcin F=(a+b)cd con una CMOS complementaria y tcnica de diseo de celdas estndar. Para ello calcula el mejor orden de llegada de las entradas utilizando el grafo lgico. B) Implementar la funcin con lgica de precarga y evaluacin (figura a). Indica claramente que ocurre en las fases de precarga y evaluacin C) Estudia en que casos se podra producir distribucin de carga en el caso anterior y simlalo. D) Aplica la solucin al problema de la distribucin de carga que aparece en la figura B y comenta las repercusiones que tiene sobre la evaluacin, la precarga, el rea y el consumo

Fig y puerta lgina cmos complementaria usando tecnicas de layout de celdas estandar

11

Practicas de diseo full-custom

El conjunto de puertas NMOS se puede utilizar para realizar el diseo de precarga y evaluacin

12

Practicas de diseo full-custom

2.2 PUERTAS DINMICAS EN CASCADA

Las puertas implementadas mediante lgica de precarga y evaluacin no se pueden conectar directamente en cascada debido a que se pueden descargar las capacidades de salida de la segunda etapa debido a retardos en la propagacin de la evaluacin de la primera etapa. A) Implementa el circuito de la figura. Utiliza la tcnica de layout de celdas estndar. B) Calcula las seales de reloj y de entrada para que se produzca el fenmeno de descarga de la capacidad. Simlalo para que se vea claramente el problema de la descarga de la capacidad

F=Ab+cd

FG+C

G=(A+B)(C+D)

13

Practicas de diseo full-custom

14

Practicas de diseo full-custom

2.3 LGICA DOMINO

La lgica domin surgi como solucin al problema de la descarga de la capacidad cuando se conectaba lgica de precarga y evaluacin en cascada. A) Sabiendo que el esquema de la lgica domin es el de la figura implemntala suponiendo que PDN1= (a+b)(c+d) y PDN2=(pl+rt) nota: En est lgica se debe tener cuidado con los diseos porque al ser puertas que implementan funciones lgicas positivas no es una lgica completa

Mp

Vout1

Mp

PDN1

PDN2

Mn

Mn

2.4 LGICA ZIPPER

El problema que introduca la lgica domin era que al tener que aadir inversores a la salida de las puertas estas solo implementaban lgica positiva y esto haca los diseos complejos. Adems se consuma mucho rea debido al inversor. Como solucin surgi la lgica Zipper cuyo esquema se puede ver en la figura X. A) Implementa con lgica zipper la misma funcin implementada para la lgica domino y compara los resultados.

PDN

PUP

PDN

PUP

15

Practicas de diseo full-custom

2.5 C2MOS CLOCKED CMOS

Implementar la funcin F=(a+bc)d con los dos esquemas que aparecen en la figura y comenta los resultados.

Vout

Vout

N

16

Practicas de diseo full-custom

3. LGICA SECUENCIAL

3.1 ESTRUCTURAS DE MEMORIA DE UNA FASE DE RELOJ

3.1.1 BIESTABLE D Dato CK Q nQ

3.1.2 CARGA POR FLANCO

nQm Dato Q

CK

3.1.3 LATCH CON SOLO UNA PUERTA DE TRANSMISIN.

3.1.4 REGISTRO DE DESPLAZAMIENTO DINMICO IN CK C1 CK C2 OUT

3.1.5 REGISTRO C2MOS

CK CK

CK CK

17

Practicas de diseo full-custom

3.2 ESTRUCTURAS LGICAS DE UNA FASE DE RELOJ

Partiendo de un registro de desplazamiento dinmico se puede realizar la siguiente implementacin de un Pipe Line:

CK IN CK IN T1

Funcin F

CK OUT CK

Funcin

CK

T2 C2

T3 C3

C1

3.3 LGICA NORA

sabiendo que

BLOQUES CK

A un bloque N

A un bloque P

Mp

P1

A una seccin CLK

CL N1 Mn

A un bloque N

A un bloque P

18

Practicas de diseo full-custom

BLOQUE NOTCLK

Mp

P1

A una seccin CLK

CL N1 Mn

Para conseguir bloques en cascada se hace de la siguiente manera:

DN

DP

C2MOS

DP

DN

C2MOS

DN

DP

C2MOS

19

Practicas de diseo full-custom

4. SUBSISTEMA DE MEMORIA

4.1 INTRODUCCIN

El esquema general de un bit de memoria aparece en la siguiente figura:

Lineas de bit

Celda de memoria

Decodifica columnas

Decodifica filas

Buffer de escritura Amplificadores mux

4.2 CELDA DE 6 TRANSISTORES CON PRECARGA

precarga

BIT NBIT

palabra

20

Practicas de diseo full-custom

4.3 CELDA DE 4 TRANSISTORES (DINMICA)

NBIT BIT

WORD

WORD

21

Practicas de diseo full-custom

4.4 DECODIFICADORES

4.4.1 DECODIFICADORES DE FILA Weste pg 574.Me gusta ms lo que viene en el weste porque se complementa con lo que se dijo en clase de que se usan decodificadores implementados en lgica pseudo-nmos. Tambin comenta aqu lo de la decodificacin de dos niveles ( Rabey pg 593) Un decodificador de N entradas tiene 2N salidas cada una de las cuales es un mintrmino de la entrada, es decir cada lnea de seleccin viene implementada por un puerta nand de tantas entradas como tiene el decodificador.

M3=ab

a M2=anb

M1=nab

M0=nanb

La primera manera que a uno se le puede ocurrir de implementar esto es colocar una puerta NAND complementaria seguida de un inversor. Pero esta implementacin no es demasiado buena cuando se trata de memorias de gran tamao, en la que es crtica tanto el rea consumida como la velocidad de funcionamiento. La implementacin habitual es mediante puertas NOR de lgica pseudo NMOS de tamao mnimo bufferadas con dos inversores convenientemente escalados. Por otro lado conviene saber que en ocasiones dividir una puerta lgica en dos o ms layers lgicos a menudo produce layers ms rpidos y econmicos. Esto hace surgir el concepto de predecodificacin. Se decodifica un segmento de la direccin en el primer layer y el segundo layer produce la seleccin de la palabra. Esto se puede traducir en la siguiente aproximacin. Se sustituye una puerta AND por dos niveles de puertas (NAND+NOR).

22

Practicas de diseo full-custom

4.4.2 DECODIFICADORES DE COLUMNAS Rabey pg 594 La diferencia con los decodificadores de fila es que estos suelen ser bastante mayores que los de columna. Por eso en este segundo caso se suele utilizar multiplexores para realizar la seleccin del dato de salida. En la actualidad existen dos tipos de implementacin que se ven a continuacin. Implementacin 1

Bit3 Bit2 Bit1 Bit0

Dir columna

DECODIFICA

Sal dato

Implementacin 2 Sabiendo que un multiplexor se puede implementar de la siguiente manera:

Dir1 Dir 1

Bit 0 Sal dato Bit 1

Para implementar un multiplexor que debe seleccionar entre 8 bits se utilizara un diseo multinivel de mulitplexores:

23

Practicas de diseo full-custom

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 nDir 2 Dir 0 nDir 0 Dir 1 nDir 1 Dir 2

Esta aproximacin tiene la ventaja del enorme ahorro de rea con respecto al primer decodificador, pero es mucho ms lento debido a la gran cantidad de transistores que tiene que atravesar, adems de la degeneracin de la seal que se produce.

24

Practicas de diseo full-custom

5. SUBSISTEMA ARITMETICO

5.1 SUMADOR

Ci

B Ci A

Ci Ci A Ci A B B

CO

A B Ci

Las expresiones tpicas del sumador se pueden manipular para conseguir compartir layout entre las dos funciones lgicas. El resultado de esta manipulacin se puede ver en las expresiones que aparecen a continuacin y en el esquemtico de la figura. C0=AB+BCi+ACi S=ABCi+C0(A+B+Ci) Aunque este sumador consume menos rea que la implementacin directa de las expresiones de suma tiene importantes inconvenientes como utilizar 28 transistores para su implementacin, es decir sigue consumiendo mucho rea y potencia. Y adems es un circuito muy lento.: Cadenas de transistores p largas tanto en el carry como en la suma La seal co tiene una capacidad intrinseca muy grande que consta de dos transitores y seis capacidades de puerta. Prctica: Implementar el sumador de la figura para cuatro bits utilizando los el primer estilo de layout que se explica en el tema 8.

Sumador simtrico o mirror

25

Practicas de diseo full-custom

Ci

A Ci A

C0

Ci A A B Ci B

Ci

B A B

Prctica: Implementar el sumador de la figura para cuatro bits utilizando los el segundo estilo de layout que se explica en el tema 8.

26

Practicas de diseo full-custom

6. REGLAS DE DISEO Las reglas de diseo son el punto de conexin entre el diseador de C.I. y el ingeniero de procesos durante la fase de fabricacin. El principal objetivo de estas reglas de diseo es obtener un circuito con un rendimiento de produccin optimo (circuitos validos/circuitos no validos) en un rea lo menor posible sin comprometer la fiabilidad del circuito. En definitiva representan el mejor compromiso entre la rentabilidad de la fabricacin y el performance del circuito. Si las reglas son conservadoras dan lugar a circuitos que cuya rentabilidad de fabricacin es mayor pero que son mas lentos y ocupan mayor rea. Las reglas mas agresivas tienen mayor probabilidad de generar mejoras en el performance, pero estas mejoras pueden daar la rentabilidad. Las reglas de diseo especifican al diseador ligaduras geomtricas y topolgicas que deben cumplir los patrones utilizados en el proceso de fabricacin. Estas ligaduras no son leyes rgidas que se deban cumplir inexorablemente para que los circuitos funcionen correctamente, sino ms bien son recomendaciones del fabricante que aseguran una alta probabilidad de una fabricacin correcta. Se pueden encontrar diseos que violan las reglas y viceversa.Existen dos conjuntos bien diferenciados de reglas de diseo: las que especifican la anchura mnima de las lneas y las que especifican distancia entre layers. Una anchura demasiado pequea lleva consigo una discontinuidad en las lneas lo que puede provocar cortocircuitos, y si los layers estn demasiado cercanos se pueden fundir o interactuar el uno con el otro produciendo un cortocircuito entre dos nodos de circuitos diferentes Hay dos aproximaciones para describir las reglas de diseo: las Reglas micron que dan las anchuras y distancias entre layers en micras m y son con las que se trabaja en en la industria y las reglas basadas en lambda. Con estas normas no se trabaja directamente con la longitud en micras, sino con un parmetro al que se le da un valor determinado segn la tecnologa con la que estemos trabajando. En teora permite trabajar con diseos independientemente del avance tecnolgico. Es decir 0Un diseo que utilizase reglas lambda en su descripcin servira para diferentes tecnologas. Esto fue cierto cuando se trabajaba con tecnologas sobremicra (de 4- a 5 .) porque el escalado era lineal pero no es valido para tecnologas inferiores.

6.1.1 REPRESENTACIN DE LAYERS El proceso de fabricacin de un dispositivo CMOS es muy complejo y necesita muchos niveles de mascaras. Si el diseo tuviera que describir todas las mascaras, este se hara engorroso y pesado. Generalmente se hace una abstraccin del diseo y solo se utilizan las mascaras estrictamente necesarias. Los elementos que se utilizan para describir un diseo CMOS son: Polisilicio Difusin n Difusin p

27

Practicas de diseo full-custom

Metal 1 Metal 2 Pozo Contacto n Contacto p Contacto metal-poli Contacto metal-metal La forma de representar estos layers: Diferentes colores. Diferentes tipos de bordes. Diferentes rellenos o fondos. Rojo-polisilicio Azul metal Verde claro difusin P Verde obscuro difusin n

28

Practicas de diseo full-custom

6.1.2 ENUMERACIN DE LAS REGLAS

Pozo N

r101. Tamao minimo:12 r102. Espacio entre dos pozos :12

DIFUSION

r201. Tamao mnimo 4 r202. Espacio mnimo 4 r203.Pozo extra tras la difusin:6 r204. Distancia de un pozo y la difusinr:6

Polisilicio.

r301, r302, r303. Tamao mnimo 2 r304. Distancia entre dos polisilicios 3 R305. Distancia entre poli y difusin 2 R306.difusin despues de poli 4 R307. Extensin depoli despues de difusin 2

29

Practicas de diseo full-custom

CONTACTOS.

R401: anchura de contacto :2 R404: entre dos contactos:3 R403 extrametal sobre contacto 2 R404: extra poli sobre contacto 2 R405 extra diff sobre contacto 2

METAL 1

R701: Tamao minimo 3 2. Distancia minima 3

30

Practicas de diseo full-custom

VIA ENTRE M1 Y M2

r601: anchura de la via: 3 r602 distancia entre dos vias 3 r603 distancia entre via y contacto 3 r604 extra metal over via: 2 r605: extrametal 2over via

metal2 : r701 anchura 5 r702 distancia entre dos metales 2:5

31

Practicas de diseo full-custom

7. TCNICAS DE DISEO Para puertas complejas existen dos tcnicas de layout: la de Weinberger y la de celdas estndar. En la tcnica de Weinberger las lneas de entrada y salida de datos se rutan en metal y en paralelo con las lneas de alimentacin y en perpendicular a las reas de difusin. Esta tcnica es particularmente efectiva para los caminos de datos bit-sliced.

En la tcnica de celdas estndar. Las seales se rutan en polisilicio y perpendiculares a las lneas de alimentacin. Esta aproximacin da lugar a layout de gran densidad sobre todo en los orientados a lgica combinacional esttica. Las interconexiones entre celdas se hacen a travs de los llamados canales de rutado. Esta tcnica es muy popular debido al alto grado de automatizacin que se puede obtener.

Por razones de densidad conviene que los transistores NMOS y PMOS se implementen como una fila continua de dispositivos con lneas de fuente y alimentacin colindantes. Con esta estrategia se necesita una nica banda de difusin. Este objetivo no siempre se puede alcanzar, pero se pueden obtener muy buenos resultados si se analizan el orden en que las seales de entrada llegan al layout. Para esto existe un anlisis sistemtico de las seales de entrada que sirve para encontrar el mejor resultado.

32

Practicas de diseo full-custom

Las libreras de celdas estndar suelen proporcionar una amplio rango de puertas, tanto para diferentes fanin, como fanout. Las puertas mas tpicas son and/nand, or/nor exor/xor y flipflops, aunque tambin suelen contener celdas ms complejas como por ejemplo and-or-inversor, mux, sumadores, contadores, decodificadores. Puesto que tanto el fan-out de las puertas como la capacidad de carga debido al hilo son desconocidas, para asegurar a las puertas son capaces de cargarlas correctamente en tiempos aceptables se suelen emplear transistores de salida muy grandes. Esto simplifica el diseo pero va en detrimento del area y la potencia. La opcin alternativa es proporcionar para cada puerta logica diferentes celdas encargadas de cargar diferentes capacidades. Tcnica del grafo lgico. El grafo lgico de una red de transistores es aquel en el que los vrtices corresponden a los nodos del circuito (siendo los nodos las uniones entre transistores y la alimentacin y la tierra). Las aristas del grafo son los transistores que unen los nodos. A estas aristas se les da el nombre de la seal que lo controla. El grafo lgico puede ser del rbol NMOS o del rbol PMOS. Se llama camino de Euler al camino que recorre todas las aristas del grafo sin repetir ninguna de ellas. El orden en que se recorren las aristas es el orden en que deben llegar las entradas. Como existe un grafo para el rbol PMOS y otro para el rbol NMOS, puede que se obtengan dos ordenes de entradas diferentes. Cuando el orden de las entradas es el mismo para los dos grafos se dice que los caminos de Euler son consistentes. Este es el caso ptimo para optimizar el layout. En la figura que viene a continuacin se ve como son los grafos lgicos para puerta de la izquierda. Se ve con claridad que {a,b,c} es un caminos de datos consistente que fija el mejor orden de llegada de las seales al layout

33

Practicas de diseo full-custom

vdd b j a x c y a b b gnd j a x i vdd c c x

gnd

34

Practicas de diseo full-custom

8. DEL ESQUEMATICO DEL CAMINO DE DATOS AL AYOUT Las necesidades de rendimiento afectan a la manera final en que la estructura del circuito se vuelca sobre el silicio. Hay que tener gran cuidado en minimizar las capacidades parsitas de los caminos crticos . El primer objetivo es conservar la estructura del diseo minimizando la longitud de los hilos. Esto explica el porque el diseo del camino de datos todava es manual, sobre todo en microprocesadores de alto rendimiento, mientras el diseo de otras unidades como la de control es automtica. Afortunadamente la regularidad de las estructuras del camino de datos simplifica la tarea del diseador, aplicando tcnicas de bit-slice. En un proceso de dos lneas de metal, existen un cierto nmero de estrategias para implementar los mdulos bit-slice. Las topologa de bsica y la eleccin de los layer de rutado semuestran en la figura En la primera aproximacin , los pozos se orientan horizontalmente y se comparten entre slices vecinos.. La lnea de alimentacin Vdd tambin se comparte entre slice vecinos. Esto hace colocar los slices pares e impares tomando como eje la lnea de alimentacin

Lneas de control Metal 1

pozo Lneas de seal Metal 2 VDD

GND

35

Practicas de diseo full-custom

Funcin 1 Funcin 2 GND

Slice 1

VDD

Slice 2

GND Slice 1 y slice 2 vecinos

En la segunda estrategia, el pozo y las lineas de alimentacin corren de arriba abajo y pueden compartirse entre celdas vecinas del mismo slace, por ejemplo entre una celda sumadora y una multiplicadora. Esto implica que estas celdas puedan conectarse "by abutment" lo que excluye la insercin de canales de rutado verticales. Esta aproximacin es mejor para el diseo manual.

Control Metal1

Hilos de seal Metal2

Pozo n

GND M1

vdD M1

GND M1

36

Practicas de diseo full-custom

Funcion 1 Funcion 2 Funcion 1 Pozo n

Slice 2

Slice 1

GND M1

vdD M1

GND M1

Algunas caractersticas de este tipo de layout se pueden ver a continuacin: Las lneas globales de alimentacin se rutan en la parte superior e inferior del diseo en metal 2 (horizontalmente) mientras que se distribuyen en vertical en metal 1 Los canales de rutado verticales se proporcionan para capacitar las conexiones entre celdas vecinas, esto impide que estas celdas compartan pozo. De hecho el layaout clsico explicado solo se encuentra en la actualidad en celdas de tipo sumador donde la profundidad de la lgica requiere puertas en cascada. En estos caso las lneas de alimentacin y los pozos si se comparten entre celdas vecinas. La aproximacin de datapath bite-slice usa un paradigma de ubicacin lineal. Esto es todas las celdas son ubicadas en un nico eje. Debido a esto algunas conexiones deben atravesar entre celdas no vecinas. Para intentar que no crezca en exceso la longitud del hilo y por lo tanto su capacidad asociada, feedthroughs son usadas . Estas son areas entre celdas no usadas

37

You might also like

- Evaluación 2 REDES DE COMPUTADORES PARTE 1Document5 pagesEvaluación 2 REDES DE COMPUTADORES PARTE 1carlos augusto padilla gonzalezNo ratings yet

- GT12 Dispositivos de Entrada y SalidaDocument13 pagesGT12 Dispositivos de Entrada y SalidaJuan RodriguezNo ratings yet

- ComunicaDocument23 pagesComunicaSergio Quisbert P.No ratings yet

- Entregable 02Document5 pagesEntregable 02Jordan Rubio Vasquez100% (1)

- Metodología de La Detección de FallasDocument3 pagesMetodología de La Detección de FallasMauro FabianNo ratings yet

- Evidencia de Actividades en Packet Tracer (Capitulo 9)Document29 pagesEvidencia de Actividades en Packet Tracer (Capitulo 9)Andresrc6cNo ratings yet

- Receptores de Un Sistema de ComunicacionDocument3 pagesReceptores de Un Sistema de ComunicacionHenryNo ratings yet

- 1-Buenas Practicas Apicolas - BPAp PDFDocument88 pages1-Buenas Practicas Apicolas - BPAp PDFMary Luz Castañeda AgudeloNo ratings yet

- Cómo Identificar Valor de Componentes SMD en Un CircuitoDocument5 pagesCómo Identificar Valor de Componentes SMD en Un CircuitoDairo DNo ratings yet

- Trabajo de Domotica. Instalaciones ElectricasDocument6 pagesTrabajo de Domotica. Instalaciones ElectricasAna LuchiiaNo ratings yet

- Satellite C45-ASP4311FL Spec SP PDFDocument4 pagesSatellite C45-ASP4311FL Spec SP PDFLucho Cohaila GuzmanNo ratings yet

- Maquinas Secuenciales EjemplosDocument12 pagesMaquinas Secuenciales EjemplosDanny Perez100% (1)

- 222 - Syllabus Instrumentación y Medidas (Rev WR)Document7 pages222 - Syllabus Instrumentación y Medidas (Rev WR)Fredy AcostaNo ratings yet

- Robotica Industrial - Manual de Laboratorio y PracticasDocument45 pagesRobotica Industrial - Manual de Laboratorio y PracticasJuvenal G. C. Gallardo100% (1)

- 02 - FX - Front - Panel - Auto - Programming r4 EspañolDocument23 pages02 - FX - Front - Panel - Auto - Programming r4 EspañolHugoRosenblattNo ratings yet

- TBSDocument11 pagesTBSJefry Osorio LemusNo ratings yet

- Arquitectura y Ensamblaje de ComputadorasDocument18 pagesArquitectura y Ensamblaje de ComputadorasHector RodriguezNo ratings yet

- Tarea - 3 - Sistema de ComunicaciónDocument15 pagesTarea - 3 - Sistema de ComunicaciónXergio LmusNo ratings yet

- Diseño de Fuente Sin TramsformadorDocument29 pagesDiseño de Fuente Sin Tramsformadoroscar marinNo ratings yet

- CV Ing - Pablo Salazar LDocument4 pagesCV Ing - Pablo Salazar LPablo V SalazarNo ratings yet

- Matriz Recursos TecnologicosDocument1 pageMatriz Recursos TecnologicosEliodoro Pernet Ubarne100% (4)

- Seguimiento y Soporte para El Proceso de Formación Virtual 21.04Document14 pagesSeguimiento y Soporte para El Proceso de Formación Virtual 21.04JudithBp01No ratings yet

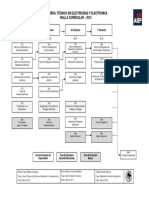

- Malla Curricular-Técnico en Electricidad y Electrónica-2013 (2016)Document1 pageMalla Curricular-Técnico en Electricidad y Electrónica-2013 (2016)cuenta forniteNo ratings yet

- Comparador de VoltajeDocument4 pagesComparador de VoltajeCamila GuerraNo ratings yet

- 11 1598267260 Eco2 mg102Document2 pages11 1598267260 Eco2 mg102Sorin AlexandruNo ratings yet

- BR ProductPortfolio WIIKADocument116 pagesBR ProductPortfolio WIIKAMartin AndradeNo ratings yet

- Toshiba Satellite Pro A210-SP6812 Portatil Francisco ArturoDocument3 pagesToshiba Satellite Pro A210-SP6812 Portatil Francisco Arturojuanelos21No ratings yet

- Imforme Formato IEEEDocument10 pagesImforme Formato IEEECristian TituanaNo ratings yet

- Amplificador Cuasi ComplementarioDocument8 pagesAmplificador Cuasi ComplementarioJuan AllendeNo ratings yet

- Procesadores I3 I5 I7 y Equivalentes en AMDDocument9 pagesProcesadores I3 I5 I7 y Equivalentes en AMDJohn ConstantineNo ratings yet