Professional Documents

Culture Documents

11 Level Diode Clamped Inverter-Ijcis-2011

Uploaded by

gjk1236596Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

11 Level Diode Clamped Inverter-Ijcis-2011

Uploaded by

gjk1236596Copyright:

Available Formats

International Journal of Computer Information Systems, Vol. 3, No.

3, 2011

Diode Clamped Multilevel Inverter Eleven Level

K.Shashikanth

shashi221@gmail.com B.tech ACE Engineering College. Hyderabad, India.

Vaishnavi.T

R.Linga Swamy

vaishnavi_tunuguntla@yahoo.com rlingaswamy@gmail.com B.E. 4th year Asst. Professor University College of Engg (A), Osmania University, Hyderabad, India.

ABSTRACT- In photovoltaic power systems where a set of series-connected photo voltaic arrays is connected to a conventional two-level inverter, the occurrence of partial shades and/or the mismatching of photo voltaic arrays leads to a reduction in power generated from its potential maximum. In order to minimize these cons, we consider the connection of photo voltaic arrays to a multi-level diode clamped converter in this paper. Among the various techniques available for the triggering of the IGBTs we make use of the PWM technique. It has been simulated using the MATLAB/ Simulink software package and total harmonic distortion (THD) is calculated. Keywords: Diode Clamped Inverter, Multilevel inverter, PWM switching

square wave output if fundamental frequency switching is used. These multilevel inverters are further classified into three types: diode clamped inverters, flying capacitor inverters, and cascaded inverters. Comparing with the number of other components, for example, clamping diodes and dc-link capacitors having the same capacity per unit, diode clamped inverters bear the advantage of requiring the least number of capacitors, however require additional clamping diodes. Flying capacitor inverters need the most number of capacitors. But cascaded inverters are considered as having the simplest structure. The diode clamped inverter, particularly the three level one, has drawn much interest in motor drive applications because it needs only one Common voltage source. Also, simple and efficient PWM algorithms have been developed for it, even if it has inherent unbalanced dc-link capacitor voltage problem. However, it would be a limitation to applications beyond four-level diode clamped inverters for the reason of reliability and complexity considering dc-link balancing and the prohibitively high number of clamping diodes. Multilevel PWM has lower DV/dt than that experienced in some two-level PWM drives because switching is between several smaller voltage levels. II. DIODE-CLAMPED MULTILEVEL INVERTER In an m-level inverter, m-1 capacitors are employed on the dc bus to produce m

I.

INTRODUCTION

In traditional methods, controlled ac drives in the megawatt range were usually connected to the medium-voltage network with the growing demand of the industries; it is practically not feasible to continue with the same method. As a replacement, a new family of multi-level inverters has been developed to serve the purpose. The general structure of the multilevel inverter is to synthesize a sinusoidal voltage from several levels of voltages, typically obtained from capacitor voltage sources. The multilevel inverters start from three levels. A three-level inverter, also known as a neutral clamped inverter consists of two capacitor voltages in series and uses the center tap as the neutral. Each phase leg of the three-level inverter has two pairs of switching devices in series. The centre of each device pair is clamped to the neutral through clamping diodes. The waveform obtained from a three-level inverter is a quasi

September Issue

Page 101 of 105

ISSN 2229 5208

International Journal of Computer Information Systems, Vol. 3, No. 3, 2011

Fig.1 Output line voltage of 11-level DCMLI

Fig: 2 Three phase Eleven level diode clamped multilevel inverter schematic.

September Issue

Page 102 of 105

ISSN 2229 5208

International Journal of Computer Information Systems, Vol. 3, No. 3, 2011

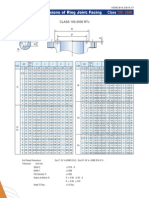

Table: 1 DCMLI Voltage Levels and Switching State

VOLTAGE Va V10= 10Vdc V9= 9Vdc V8= 8Vdc V7= 7Vdc V6= 6Vdc V5= 5Vdc V4= 4Vdc V3= 3Vdc V2= 2Vdc V1= 1Vdc V0= 0Vdc

Sa1 1 0 0 0 0 0 0 0 0 0 0

Sa2 1 1 0 0 0 0 0 0 0 0 0

Sa3 1 1 1 0 0 0 0 0 0 0 0

Sa4 1 1 1 1 0 0 0 0 0 0 0

Sa5 1 1 1 1 1 0 0 0 0 0 0

Sa6 1 1 1 1 1 1 0 0 0 0 0

Sa7 1 1 1 1 1 1 1 0 0 0 0

Sa8 1 1 1 1 1 1 1 1 0 0 0

Sa9 1 1 1 1 1 1 1 1 1 0 0

Sa10 1 1 1 1 1 1 1 1 1 1 0

Sa1 0 1 1 1 1 1 1 1 1 1 1

Sa2 0 0 1 1 1 1 1 1 1 1 1

Sa3 0 0 0 1 1 1 1 1 1 1 1

Sa4 0 0 0 0 1 1 1 1 1 1 1

Sa5 0 0 0 0 0 1 1 1 1 1 1

Sa6 0 0 0 0 0 0 1 1 1 1 1

Sa7 0 0 0 0 0 0 0 1 1 1 1

Sa8 0 0 0 0 0 0 0 0 1 1 1

Sa9 0 0 0 0 0 0 0 0 0 1 1

Sa10 0 0 0 0 0 0 0 0 0 0 1

levels of the phase voltage. One of the legs of the three phase 11-level inverter has been shown in the figure 2. Each of the three phases of the inverter shares a common dc bus, which has been subdivided by ten capacitors into eleven levels. The voltage across each capacitor is, and the voltage stress across each switching device is limited to the safe working level through the clamping diodes. Table 1 lists the output voltage levels possible for one phase of the inverter with the negative dc rail voltage as a reference. State condition 1 means the switch is on, and 0 means the switch is off. Each phase has 10 complementary switches. The table illustrates that complementary switches are not to be turned on simultaneously. The complementary switch pairs for phase leg A are (Sa1, Sa1), (Sa2, Sa2), (Sa3, Sa3) (Sa4, Sa4) (Sa5, Sa5), (Sa6, Sa6), (Sa7, Sa7), (Sa8, Sa8), (Sa9, Sa9), and (Sa10, Sa10). Table 1 also shows that in a diode clamped Inverter, the switches that are ON for particular phase legs are always adjacent and in series. For an eleven-level inverter, a set of ten switches is ON at any given time. Figure 1 shows one of the three line-line output voltage waveforms for an eleven-level multilevel inverter. The line voltage Vab consists of a phase-leg a Voltage and a phase-leg b voltage. The resulting line voltage is an 11-level staircase waveform. From this, it can be inferred that an m-level diode-clamped inverter has an m-level output phase voltage and a (2m-1)-level output line voltage. Although each active switching device is required to block only a voltage level of dc V, the clamping diodes require different Ratings for reverse voltage blocking. Using phase A as an example, when all the lower

switches S a1 through S a10 are turned on, D9 must block nine voltage levels or 9 Vdc. Similarly, D8 must block 8 dc V D7 must block 7 dc V D6 must block 6 dcV, D5 must block 5 dc V, D4 must block 4 dcV, D3 must block 3 dc V, D2 must block 2 dc V and D1 must block 1 dc V. If the inverter is designed such that each blocking diode has the same voltage rating as the active switches, Dn will require n diodes in series; consequently, the number of diodes required for each phase would be 2(m-2). Thus, the number of blocking diodes is quadratically related to the number of levels in a diodeclamped inverter. DCMLI has the following advantages and disadvantages. Advantages: (1) DC-link capacitors are common to three phases. (2) Switching frequency can be low. (3) Reactive current and negative-phase sequence current can be controlled Disadvantages: (1) Many diodes are used for clamping. (2) Many diodes make physical layout difficult, e.g. increase stray inductance III. PWM METHOD FOR ELEVEN-LEVEL DCMLI The PWM technique to be used for multilevel inverters can be obtained just by a slight modification in the strategies used in the conventional inverters. The most popular and easiest technique to implement uses several triangle carrier signals and one reference, or modulation, signal per phase.

September Issue

Page 103 of 105

ISSN 2229 5208

International Journal of Computer Information Systems, Vol. 3, No. 3, 2011 are shown in Figure 5 & 6. In order to get THD level of the waveform, a fast Fourier transform (FFT) is applied to obtain the spectrum of the output voltage, which is shown in Figure7.

Fig 5 Out Put Phase Voltages

Fig 3 Eleven level Inverter Model

Figure 4 shows the principle of the PWM method for a multilevel inverter. The PWM method generates switching signals by comparing one sinusoidal signal and ten triangular wave signals, which have DC bias for each voltage level, as shown in Figure 4. In this Modulation method, the duty cycle of each voltage level is determined by the ratio of the sine wave amplitude to the triangular carrier signal amplitude. That is, the sine wave amplitude determines modulation factor, and one modulation factor generates only one pattern of output pulse width.

Fig 6 Out Put Line voltages

Fig 7 Total Harmonic Distortion

Fig 4 Sinusoidal PWM

Using PWM modulation explained above, simulations have been conducted to verify the effectiveness of the algorithm. PWM modulation in MATLAB Simulink block Diagrams and the eleven-level DCMLI is shown in Figure. IV. SIMULATION RESULTS Using a comparator with inputs as a triangular carrier wave and a sinusoidal reference wave, we generate gate signals to trigger the IGBTs. The output of eleven-level DCMLI is connected to a three phase RLC load and the voltage waveforms

The THD of the output voltage of eleven-level DCMLI is 8.22% which shows that lower order harmonics have been eliminated. Therefore it is concluded that the 93% of harmonics can be eliminated within the inverter itself which is more preferable over the other lower level inverters.

V. CONCLUSION In this paper the eleven-level diode clamped multilevel inverter for harmonic elimination in MATLAB/ Simulink software package has been presented. The THD level of eleven-level DCMLI with other levels of DCMLI is explained. Simulation results reveal that the THD of eleven-level DCMLI is less than any of the other level inverters.

September Issue

Page 104 of 105

ISSN 2229 5208

International Journal of Computer Information Systems, Vol. 3, No. 3, 2011

as an Assistant Professor at Universiy College of Engineering (Autonomous), Osmania University in the department of Electrical and Electronics Engineering. He has published several papers in the area of power electronics in various international journals.

REFERENCES

[1] J. Rodriguez, J. S. Lai, F. Z. Peng, Multilevel Inverters: A Survey of Topologies, Controls, and Applications, IEEE Transactions on Industrial Electronics, Vol.49, no.4, pp. 724-738, 2002. [2] J. S. Lai, F. Z. Peng, Multilevel Converters-A New Breed of Power Converters, IEEE Transactions on Industry Applications, Vol. 32,no.3, pp. 509-517, 1996. [3] J. Chiasson, L.M. Tolbert, K.J.McKenzie, Z.Du, Control of a Multilevel Converter Using Resultant Theory, IEEE Trans on Control Systems Technology, Vol.11, no.3, pp. 345-354, 2003. [4] S. Khomfoi and L. M. Tolbert, Power Electronics Handbook, Multilevel Power Converters - Chapter 17, 2nd Edition Elsevier, 2007, ISBN 978-0-12-088479-7, pp. 451482, 2007. [5] K. Fuji, U. Schwarzer, Comparison of Hard- Switched Multi-Level Inverter Topologies for STATCOM by LossImplemented Simulation and Cost Estimation, Power Electronics Specialists Conference, PESC '05. pp.340 346, 2005. [6] McGrath, B.P. and D.G. Holmes, Multicarrier PWM Strategies for Multilevel Inverters, IEEE Transaction on Industrial Electronics, Volume 49, Issue 4, pp.858-86, 2002. [7] Wang, J, Wei, R., Ge, Q., Li, Y., The Harmonic Selection Elimination of Multilevel Converters IEEE International Conference on Electrical Machines and Systems, Vol.1, pp. 419-422, 2003 [8] S. Kjaer, J. Pedersen, and F.Blaabjerg, A Review of single-phase grid connected inverters for photovoltaic modules, IEEE Trans. Ind. Appl., vol. 41, no. 5, pp. 1292 1306, 2005. [9] S. Daher, J. Schmid, and F. Antunes, Multilevel IEEE Trans. Ind. Electron., Vol. 55, no. 7, pp. 27032712, 2008. [10] S. Busquets-Monge, J. Rocabert, P.Rodriguez, S. Alepuz, and J. Bordonau, Multilevel diode- clamped converter for Photo voltaic generators with independent Voltage control of each solar array, IEEE Trans. Ind. Electron. vol. 55, no.7, pp. 27132723, 2008 [11] Seven level diode clamped multilevel inverter by V.Saikrishna and Shashikanth IJCIIS April 2011 Vol. 2 No. 4 page no.35-42.

AUTHORS PROFILE

Katkuri Shashikanth pursued Bachelors degree from JNTU Hyderabad affliated ACE Engineering College in Electrical and Electronics Engineering. This author has been working in the area of multilevel inverters since two years and published two inernational journals. His areas of interest includes power electronics,power engineering, deregulation, signal processing etc. Vaishnavi Tunuguntla pursuing her B.E from Osmania Universiy College of Engineering in Electrical and Electronics Engineering. This author has been working in several areas including power electronics, digital signal processing etc. R.Linga Swamy R.Linga Swamy obtained his Masters degree from NIT Warangal in the field of Power Electronics and Drives. He has been working

September Issue

Page 105 of 105

ISSN 2229 5208

You might also like

- Checkpoint Physics Notes Chapter 1-5Document5 pagesCheckpoint Physics Notes Chapter 1-5Siddhant Srivastava50% (2)

- Total Harmonics Distortion Investigation in Multilevel InvertersDocument8 pagesTotal Harmonics Distortion Investigation in Multilevel InvertersAJER JOURNALNo ratings yet

- Iceict2015i020315001 PDFDocument6 pagesIceict2015i020315001 PDFmadihaNo ratings yet

- Single Phase Asymmetrical Cascaded Multilevel Inverter Design For Induction MotorDocument6 pagesSingle Phase Asymmetrical Cascaded Multilevel Inverter Design For Induction Motorfarid kerroucheNo ratings yet

- A Is (Facts) (SVG) ,: AbstractDocument9 pagesA Is (Facts) (SVG) ,: AbstractSherif M. DabourNo ratings yet

- Single-Phase Five-Level Inverter With Less Number of Power Elements For Grid ConnectionDocument7 pagesSingle-Phase Five-Level Inverter With Less Number of Power Elements For Grid Connectionvinay kumarNo ratings yet

- Iiii JJJJ S S S S A A A A A A A A: Simulation of Cascaded Multilevel Inverter Using Hybrid PWM TechniqueDocument4 pagesIiii JJJJ S S S S A A A A A A A A: Simulation of Cascaded Multilevel Inverter Using Hybrid PWM TechniqueKanaga VaratharajanNo ratings yet

- Simulation and Experimental Results of 7-Level Inverter SystemDocument8 pagesSimulation and Experimental Results of 7-Level Inverter Systembacuoc.nguyen356No ratings yet

- (IJET-V1I6P3) Authors:Bachwad M.R., Maske Ashadeep MDocument4 pages(IJET-V1I6P3) Authors:Bachwad M.R., Maske Ashadeep MInternational Journal of Engineering and TechniquesNo ratings yet

- Switching Pattern Selection Scheme Based Cascaded Multilevel Inverter Fed Induction Motor DriveDocument6 pagesSwitching Pattern Selection Scheme Based Cascaded Multilevel Inverter Fed Induction Motor Drivevinay kumarNo ratings yet

- An Analysis and Survey of Multilevel Inverters Topologies, Controls, and ApplicationsDocument10 pagesAn Analysis and Survey of Multilevel Inverters Topologies, Controls, and ApplicationsDr-Ismayil CNo ratings yet

- Three-Level Inverter Speed Control of Induction MotorDocument12 pagesThree-Level Inverter Speed Control of Induction MotorMallikarjunBhiradeNo ratings yet

- Multi-Modular Multi-Level Pulse Width Modulated Inverters: Mon W LDocument6 pagesMulti-Modular Multi-Level Pulse Width Modulated Inverters: Mon W LveguruprasadNo ratings yet

- Single-Phase Seven-Level Grid-Connected Inverter For Photovoltaic SystemDocument14 pagesSingle-Phase Seven-Level Grid-Connected Inverter For Photovoltaic Systemqais652002No ratings yet

- Fault Elimination in Transmission Line Using Eleven Level StatcomDocument7 pagesFault Elimination in Transmission Line Using Eleven Level Statcomsurendiran123No ratings yet

- A Novel Two Switches Based DC-DC Multilevel Voltage MultiplierDocument5 pagesA Novel Two Switches Based DC-DC Multilevel Voltage MultiplierdanielflorescortezNo ratings yet

- Comparison of Multicarrier PWM Strategies For Five-Level Z-Source Diode-Clamped Inverter For On-Grid Renewable Energies ApplicationsDocument5 pagesComparison of Multicarrier PWM Strategies For Five-Level Z-Source Diode-Clamped Inverter For On-Grid Renewable Energies ApplicationsJeya RamNo ratings yet

- MultilevelDocument15 pagesMultilevelsyfullahnelNo ratings yet

- Paper 12Document9 pagesPaper 12Hari ShankarNo ratings yet

- Induction Motor Drive Using Seven Level Multilevel Inverter For Energy Saving in Variable Torque Load ApplicationDocument8 pagesInduction Motor Drive Using Seven Level Multilevel Inverter For Energy Saving in Variable Torque Load ApplicationAnonymous 22GBLsme1No ratings yet

- A Novel Scheme To Eliminate Common Mode Voltage in Multilevel InvertersDocument4 pagesA Novel Scheme To Eliminate Common Mode Voltage in Multilevel InvertersJavier MaldonadoNo ratings yet

- International Journal of Computational Engineering Research (IJCER)Document7 pagesInternational Journal of Computational Engineering Research (IJCER)International Journal of computational Engineering research (IJCER)No ratings yet

- 11 Level Inverter With Less Number of Switches: Mubashrasazda KhanDocument10 pages11 Level Inverter With Less Number of Switches: Mubashrasazda Khanajay rNo ratings yet

- Comparative study of MLI and dual inverter using SVM techniquesDocument8 pagesComparative study of MLI and dual inverter using SVM techniquesshiva256No ratings yet

- 9-Level Trinary DC Source Inverter Using Embedded ControllerDocument6 pages9-Level Trinary DC Source Inverter Using Embedded ControllerIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalNo ratings yet

- 04285962, DJSDocument9 pages04285962, DJSDeepu ChinnaNo ratings yet

- International Journal of Engineering Research and DevelopmentDocument7 pagesInternational Journal of Engineering Research and DevelopmentIJERDNo ratings yet

- Single-Phase Seven-Level Grid-Connected Inverter For Photovoltaic SystemDocument9 pagesSingle-Phase Seven-Level Grid-Connected Inverter For Photovoltaic SystemDeepak Kumar NayakNo ratings yet

- Seven Level Inverter With Nearest Level ControlDocument7 pagesSeven Level Inverter With Nearest Level Controlsanjay sNo ratings yet

- Multilevel Converters-A New Breed of Power Converters: Jih-Sheng and Fang Zheng PengDocument9 pagesMultilevel Converters-A New Breed of Power Converters: Jih-Sheng and Fang Zheng PengEdsonNo ratings yet

- Q02201300137Document8 pagesQ02201300137Vikas PatelNo ratings yet

- Simulation of Single Phase Multilevel Inverters With Simple Control Strategy Using MATLABDocument9 pagesSimulation of Single Phase Multilevel Inverters With Simple Control Strategy Using MATLABFarman UllahNo ratings yet

- Design of 7 & 9 Level Inverters with Less SwitchesDocument6 pagesDesign of 7 & 9 Level Inverters with Less SwitchesJediNo ratings yet

- Harmonic Reduction in Parallel Inverters Using THIPWMDocument6 pagesHarmonic Reduction in Parallel Inverters Using THIPWMAhmed JanadNo ratings yet

- Rao 2013Document7 pagesRao 2013aditya317crazyNo ratings yet

- Analysis and Control of DSTATCOM For A Line Voltage RegulationDocument6 pagesAnalysis and Control of DSTATCOM For A Line Voltage RegulationSeema P DiwanNo ratings yet

- Novel Seven - Level Flying Capacitor Based Active Neutral Point Clamped Converter Using Photovoltaic Energy GenerationDocument4 pagesNovel Seven - Level Flying Capacitor Based Active Neutral Point Clamped Converter Using Photovoltaic Energy GenerationInnovative Research PublicationsNo ratings yet

- Single Phase To Three Phase ConverterDocument5 pagesSingle Phase To Three Phase ConverterGabriel MejiaNo ratings yet

- A Novel ZVS Bidirectional DC-DC Converter For Fuel Cell ApplicationsDocument4 pagesA Novel ZVS Bidirectional DC-DC Converter For Fuel Cell ApplicationsS B RajNo ratings yet

- A Study of Comparative Analysis of Different PWMDocument6 pagesA Study of Comparative Analysis of Different PWMwilliam chaconNo ratings yet

- Improving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshDocument5 pagesImproving The Power Quality by MLCI Type DSTATCOM: P. Manoj Kumar Y. Sumanth S. N. V. GaneshsarathNo ratings yet

- Performance Analysis of Multi-Level Inverter For Dynamic Voltage RestorerDocument6 pagesPerformance Analysis of Multi-Level Inverter For Dynamic Voltage Restorersup9No ratings yet

- Design and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerDocument12 pagesDesign and Implementation of Space Vector PWM Inverter Based On A Low Cost MicrocontrollerHaider NeamaNo ratings yet

- Improved Voltage and Power Quality of Cascaded Inverters Using Sine Quantization Progression MethodDocument8 pagesImproved Voltage and Power Quality of Cascaded Inverters Using Sine Quantization Progression MethodSabdo WibowoNo ratings yet

- Modular Multilevel Converter Control Strategy With Fault ToleranceDocument6 pagesModular Multilevel Converter Control Strategy With Fault TolerancesatyacvaNo ratings yet

- Low Cost Digital Signal Generation For Driving Space Vector PWM InverterDocument12 pagesLow Cost Digital Signal Generation For Driving Space Vector PWM InverterJunaid AhmadNo ratings yet

- Passive Filter-1110Document9 pagesPassive Filter-1110christopherNo ratings yet

- A Generalized Multilevel Inverter TopologyDocument8 pagesA Generalized Multilevel Inverter TopologyMinh NhậtNo ratings yet

- Multilevelinverter PPT FINALDocument27 pagesMultilevelinverter PPT FINALROSHAN KUMAR GUPTANo ratings yet

- International Journal of Engineering Research and DevelopmentDocument7 pagesInternational Journal of Engineering Research and DevelopmentIJERDNo ratings yet

- A Modified Seven Level Cascaded H Bridge InverterDocument6 pagesA Modified Seven Level Cascaded H Bridge InverterMary NdhlovuNo ratings yet

- High Performance of Sinusoidal Pulse Width Modulation Based Flying Capacitor Multilevel Inverter Fed Induction Motor DriveDocument6 pagesHigh Performance of Sinusoidal Pulse Width Modulation Based Flying Capacitor Multilevel Inverter Fed Induction Motor DrivePradyumn ChaturvediNo ratings yet

- Inverter and Its TopologiesDocument14 pagesInverter and Its TopologiesAvnesh SuryavanshiNo ratings yet

- Mali 2019Document7 pagesMali 2019aymenNo ratings yet

- Resonant DC Link in PWM AC ChopperDocument5 pagesResonant DC Link in PWM AC ChopperMukesh SharmaNo ratings yet

- Seminar ReportDocument23 pagesSeminar ReportvinaykumaarNo ratings yet

- THD Analysis of Cascaded Multi Level Inverters Using Different PWM TechniquesDocument4 pagesTHD Analysis of Cascaded Multi Level Inverters Using Different PWM TechniquesEditor IJTSRDNo ratings yet

- Optimum Space Vector PWM Algorithm For Three-Level Inverter: B. Urmila and D. Subba RayuduDocument13 pagesOptimum Space Vector PWM Algorithm For Three-Level Inverter: B. Urmila and D. Subba RayudusureshonuNo ratings yet

- Authors:: M.V.S.Prajith B.NagarjunaDocument18 pagesAuthors:: M.V.S.Prajith B.NagarjunaKALYANpwnNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Power Quality Unit-1 M.tech (10-4-2018) FinalDocument31 pagesPower Quality Unit-1 M.tech (10-4-2018) Finalgjk1236596No ratings yet

- Network Analysis SyllabusDocument3 pagesNetwork Analysis Syllabusgjk1236596No ratings yet

- Facts 3Document14 pagesFacts 3gjk1236596100% (1)

- Facts 4Document13 pagesFacts 4gjk1236596No ratings yet

- Unit-V: Power Flow ControllersDocument11 pagesUnit-V: Power Flow Controllersgjk1236596No ratings yet

- Neuro Controlled Seven Level InverterDocument17 pagesNeuro Controlled Seven Level Invertergjk1236596No ratings yet

- Neuro Controlled Seven Level InverterDocument17 pagesNeuro Controlled Seven Level Invertergjk1236596No ratings yet

- GJK - PSOC Course Sheet - 21!9!12Document8 pagesGJK - PSOC Course Sheet - 21!9!12gjk1236596No ratings yet

- Design Methodology For Shunt Active FiltersDocument8 pagesDesign Methodology For Shunt Active FiltersAbdalla FahmyNo ratings yet

- How To WriteDocument21 pagesHow To WriteLenin Darío DuchicelaNo ratings yet

- A380-LEVEL III - ATA 42 Integrated Modular Avionics - Avionics DaDocument66 pagesA380-LEVEL III - ATA 42 Integrated Modular Avionics - Avionics DaAbolfazl Mazloomi100% (11)

- PactFocus Report - Sample - LPGDocument27 pagesPactFocus Report - Sample - LPGIqbal HussainNo ratings yet

- Concrete Pipe Installation Guide-CPMDocument17 pagesConcrete Pipe Installation Guide-CPMSankar CdmNo ratings yet

- Pressure Regulators (DRV Valve) Suitable ForDocument4 pagesPressure Regulators (DRV Valve) Suitable ForNOUREDDINE BERCHAOUANo ratings yet

- Brandt M FR Btd500blnDocument74 pagesBrandt M FR Btd500blnStéphane JoussetNo ratings yet

- Measurement & Calculation of Vehicle Center of Gravity Using Portable Wheel ScalesDocument11 pagesMeasurement & Calculation of Vehicle Center of Gravity Using Portable Wheel ScalesVedant KodagiNo ratings yet

- Manage Payment Process Profiles - 1Document1 pageManage Payment Process Profiles - 1I'm RangaNo ratings yet

- WTS 12 ElectrodynamicsDocument28 pagesWTS 12 ElectrodynamicsTondani100% (1)

- You Yangs RP Visitor GuideDocument2 pagesYou Yangs RP Visitor GuideSomaNo ratings yet

- Dissolved OxygenDocument2 pagesDissolved OxygenAnonymous atBeojaNo ratings yet

- Control Valve and Steam Line PDFDocument19 pagesControl Valve and Steam Line PDFRofi MuhammadNo ratings yet

- Chapter 15. Applications of Integration: Exercises 15.2Document2 pagesChapter 15. Applications of Integration: Exercises 15.2Donghyun AhnNo ratings yet

- CRSP ManualDocument140 pagesCRSP ManualCarlos Andrés Buenahora BallesterosNo ratings yet

- Maxxi Report FinalDocument7 pagesMaxxi Report FinalDepanshu Gola100% (1)

- Plutnicki ResumeDocument1 pagePlutnicki ResumeAli PlutnickiNo ratings yet

- Ricoh 2090Document832 pagesRicoh 2090cosmin176100% (1)

- d-Copia3500MF 4500MF 5500MFsmY113351-4Document1,051 pagesd-Copia3500MF 4500MF 5500MFsmY113351-4ctecisbNo ratings yet

- MET312 Non Destructive Testing SyllabusDocument8 pagesMET312 Non Destructive Testing SyllabusHARI KRISHNANNo ratings yet

- LMS Adaptive FiltersDocument14 pagesLMS Adaptive FiltersalialibabaNo ratings yet

- 2019 Zeta Zwheel Catalogs PDFDocument30 pages2019 Zeta Zwheel Catalogs PDFSales One - Plusgrow - IndiaNo ratings yet

- BRAY SERIES 4X HIGH PERFORMANCE BRAY-McCANNLOCK VALVES - Technical ManualDocument28 pagesBRAY SERIES 4X HIGH PERFORMANCE BRAY-McCANNLOCK VALVES - Technical ManualLuis Daniel ContrerasNo ratings yet

- Saes N 004Document5 pagesSaes N 004Mo'tasem SerdanehNo ratings yet

- GameBoy Programming ManualDocument298 pagesGameBoy Programming Manualdiceman2037100% (4)

- Metronidazole AnalysisDocument5 pagesMetronidazole AnalysisHendri WasitoNo ratings yet

- Dual Band Mobile Phone Service ManualDocument40 pagesDual Band Mobile Phone Service Manualأبو عبد الرحمان زهيرNo ratings yet

- Mechanical Power Transmission ReviewDocument17 pagesMechanical Power Transmission ReviewRoshan TiwariNo ratings yet

- Complex Instruction Set ComputerDocument17 pagesComplex Instruction Set ComputerkangkanpaulNo ratings yet

- RTJ Dimension ASME B16.5/B16.47Document1 pageRTJ Dimension ASME B16.5/B16.47parayilomer0% (1)

- Modified 0-30V - 0-3A Variable Power Supply - Rev.2Document2 pagesModified 0-30V - 0-3A Variable Power Supply - Rev.2Manuel Cereijo NeiraNo ratings yet