Professional Documents

Culture Documents

Cache Exercicios

Uploaded by

patyvirgilioCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cache Exercicios

Uploaded by

patyvirgilioCopyright:

Available Formats

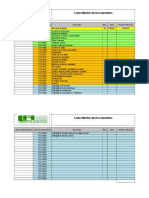

Arquitetura de Computadores Li 3 Lista de Exerccios

1)Um sistema de cache tem uma taxa de acerto de 95%, um tempo de acesso de 100 ns quando o dado for encontrado na cache e um tempo de acesso de 800 ns se a cache no contiver o dado. Qual o tempo de acesso mdio? 2)Uma cache est sendo projetada para um computador com 232 B de memria. A cache ter 2K slots (linhas) e usar um bloco de 16 B. Calcule, tanto para uma cache associativo quanto para uma cache com mapeamento direto, quantos bytes a cache ir ocupar? 3)Para os endereos hexadecimais da memria principal 111111, 666666, BBBBBB, mostre as seguintes informaes, em formato hexadecimal: a. Os valores dos campos de rtulo, linha e palavra, para uma memria cache com mapeamento direto, usando o formato TAG SLOT BYTE +------------+---------------------------------------+-----+ | 8 | 14 | 2 | +------------+---------------------------------------+-----+ b. Os valores dos campos de rtulo e palavra, para uma memria cache associativa, usando o formato TAG BYTE +----------------------------------------------------+-----+ | 22 | 2 | +----------------------------------------------------+-----+ c. Os valores dos campos de rtulo, conjunto e palavra, para uma memria cache associativa por conjuntos de duas linhas, usando o formato TAG SET BYTE +------------+---------------------------------------+-----+ | 9 | 13 | 2 | +------------+---------------------------------------+-----+

4)Considere um microprocessador de 32 bits, com uma memria cache interna pastilha de 16 Kbytes, organizada com mapeamento associativo por conjuntos de quatro linhas. Suponha que o tamanho da linha da memria cache seja de quatro palavras de 32 bits. Desenhe um diagrama de blocos dessa memria cache, mostrando sua organizao e como os diferentes campos do endereo so usados para determinar um acerto ou falha na memria cache. Onde a palavra de memria de endereo ABCDE8F8 mapeada na memria cache? 5)Suponha as seguintes especificaes para uma memria cache externa: mapeamento associativo por conjuntos de quatro linhas; tamanho de linha igual a duas palavras de 16 bits; capaz de acomodar um total de 4K palavras de 32 bits da memria principal; utilizada com um processador de 16 bits que gera endereos de 24 bits. Projete a estrutura da memria cache com todas as informaes pertinentes e mostre como ela interpreta os endereos enviados pelo processador. 1/3

UN

IM

IN

AS

Arquitetura de Computadores Li 3 Lista de Exerccios

6)A pastilha do processador Intel 80486 possui uma memria cache nica para dados e instrues. Esse processador tem capacidade de 8 Kbytes e organizado com mapeamento associativo por conjuntos de quatro linhas e com blocos de quatro palavras de 32 bits. A memria cache organizada em 128 conjuntos. Existe um nico "bit de linha vlida" e trs bits, BO, B1 e B2 (bits de uso para o algoritmo LRU), por conjunto. No caso de um acesso com falha na cache, o 80486 l uma linha de 16 bytes da memria principal, em uma nica leitura por meio do barramento de memria. Mostre como os diferentes campos do endereo so interpretados. 7)Considere uma mquina com memria endereada byte a byte, com tamanho de 216 bytes e tamanho de bloco de 8 bytes. Suponha que seja utilizada uma memria cache com mapeamento direto, composta de 32 linhas. a. Como o endereo de memria de 16 bits dividido em rtulo (TAG), nmero de linha (SLOT) e nmero de byte (BYTE)? b. Em que linha seriam armazenados os bytes com os seguintes endereos? 0001 0001 0001 1011 1100 0011 0011 0100 1101 0000 0001 1101 1010 1010 1010 1010 c. Suponha que o byte de endereo 0001 1010 0001 1010 esteja armazenado na memria cache. Quais so os endereos dos outros bytes na mesma linha? d. Qual o total de bytes de memria que podem ser armazenados na memria cache? e. Por que o rtulo tambm armazenado na memria cache?

9)Considere o seguinte cdigo: for (i = O; i < 20; i++) for (j = O; j < 10; j + +) ali] = ali] * j; a. D um exemplo de localidade espacial no cdigo. b. D um exemplo de localidade temporal no cdigo.

10)Um computador tem uma memria principal com 32K palavras de 16 bits. Tem tambm uma memria cache de 4K palavras, dividida em conjuntos de quatro linhas com 64 palavras por linha. Suponha que a memria cache esteja inicialmente vazia. O processador busca palavras das posies 0, 1, 2, ..., 4351, nessa ordem. Ele ento repete essa seqncia de referncias mais nove 2/3

UN

IM

8)Uma memria cache associativa por conjuntos tem um tamanho de bloco de quatro palavras de 16 bits e um conjunto de duas linhas. A memria cache pode acomodar um total de 4048 palavras. A poro da memria principal que cache tem dimenso de 64K x 32 bits. Mostre como os endereos do processador so interpretados.

IN

AS

Arquitetura de Computadores Li 3 Lista de Exerccios

vezes. A memria cache dez vezes mais rpida que a memria principal. Estime a melhoria de desempenho obtida com o uso da memria cache. 11) Considere um sistema de memria com os seguintes parmetros: Tc = 100 ns Tm = 1200 ns Cc = 0,01 centavo/bit Cm = 0,001 centavo/bit a. Qual o custo de 1 MB de memria principal? b. Qual o custo de 1 MB de memria principal utilizando tecnologia de memria cache? c. Se o tempo de acesso mdio 10% maior que o tempo de acesso memria cache, qual a taxa de acerto h?

REFERNCIAS

UN

IM

IN

3/3

AS

You might also like

- Exercicio 6Document2 pagesExercicio 6PhiberdjNo ratings yet

- Ar Quite TuraDocument3 pagesAr Quite TuraMaurynhoNo ratings yet

- Arquitetura de Computadores - Lista de ExercíciosDocument14 pagesArquitetura de Computadores - Lista de ExercíciosalexNo ratings yet

- Lista prova 1 memória cacheDocument6 pagesLista prova 1 memória cacheWeslley RodrigoNo ratings yet

- Exercícios sobre Gerenciamento de MemóriaDocument8 pagesExercícios sobre Gerenciamento de MemóriaJonathan MouraNo ratings yet

- Sistemas Microprocessados - Lista de ExercíciosDocument2 pagesSistemas Microprocessados - Lista de ExercíciosMatheus LibórioNo ratings yet

- ExercDocument2 pagesExercjorgeNo ratings yet

- Organização de Computadores - Gabarito AD1 2006.1Document8 pagesOrganização de Computadores - Gabarito AD1 2006.1Mauricio RodriguesNo ratings yet

- 2a Prova ED II - QuestõesDocument3 pages2a Prova ED II - QuestõesCássioNo ratings yet

- Arquitetura de Compuradores - Lista 4 PDFDocument10 pagesArquitetura de Compuradores - Lista 4 PDFSamuel LeonhardtNo ratings yet

- Sistemas Microprocessados - Respostas Lista ExercíciosDocument2 pagesSistemas Microprocessados - Respostas Lista ExercíciosPaulo SantiagoNo ratings yet

- Lista 15 - Microprogramação - Memória CacheDocument5 pagesLista 15 - Microprogramação - Memória CacheKaique LimaNo ratings yet

- Exercícios de Arquitetura de ComputadoresDocument5 pagesExercícios de Arquitetura de ComputadoresNikolas AugustoNo ratings yet

- Lista Ex 1 SC 2016 1Document2 pagesLista Ex 1 SC 2016 1Raissa BarcellosNo ratings yet

- Exercícios de Revisão 1 Arquitetura de ComputadoresDocument2 pagesExercícios de Revisão 1 Arquitetura de ComputadoresTiago VenturaNo ratings yet

- Gabarito Top Av Arq MM Prova Av1 2018 2Document5 pagesGabarito Top Av Arq MM Prova Av1 2018 2Alexandre Melo100% (1)

- Atv21 MemPrinc 27maio2011Document3 pagesAtv21 MemPrinc 27maio2011gulione123456No ratings yet

- Lista de Exercicio de CacheDocument10 pagesLista de Exercicio de CacheEmerson MenesesNo ratings yet

- Aula 13Document61 pagesAula 13Igor LimaNo ratings yet

- LIVRO MONTEIRO - Questionário Capítulo 2Document2 pagesLIVRO MONTEIRO - Questionário Capítulo 2Rodrigo Dias0% (1)

- Sistemas Operacionais: Lista de Exercícios sobre Memória VirtualDocument1 pageSistemas Operacionais: Lista de Exercícios sobre Memória VirtualDanieleValverdeNo ratings yet

- Lista de Exercícios de Memória e ComponentesDocument3 pagesLista de Exercícios de Memória e ComponentesDavi GuimarãesNo ratings yet

- Exercicios Memoria 1Document2 pagesExercicios Memoria 1marcoNo ratings yet

- Gerenciamento de memória: paginação, segmentação e alocaçãoDocument3 pagesGerenciamento de memória: paginação, segmentação e alocaçãopkaricaNo ratings yet

- 2 Lista de Exercícios de Arquitetura de Computadores: QuestõesDocument6 pages2 Lista de Exercícios de Arquitetura de Computadores: QuestõesderyNo ratings yet

- Sistemas Operacionais - AP2 2019.2Document3 pagesSistemas Operacionais - AP2 2019.2Cristiano JuniorNo ratings yet

- FATEC Questionário sobre componentes e funções de um processadorDocument4 pagesFATEC Questionário sobre componentes e funções de um processadorCassie100% (1)

- 1a Lista Arquitetura ComputadoresDocument12 pages1a Lista Arquitetura ComputadoresJOSE JOSE AUGUSTO CHAVES DA SILVA JUNIORNo ratings yet

- Eng Comp e Elet - MicroprocessadosDocument3 pagesEng Comp e Elet - MicroprocessadosLucas LagoNo ratings yet

- Exercicios de Memoria PrincipalDocument3 pagesExercicios de Memoria PrincipalLeandro PedroNo ratings yet

- Lista de Exercícios 1 - Arquiteturas de Computadores: Semana 1 - Entregar Pelo Moodle Até Às 10h Do Dia 03/10Document3 pagesLista de Exercícios 1 - Arquiteturas de Computadores: Semana 1 - Entregar Pelo Moodle Até Às 10h Do Dia 03/10Daniela KaoriNo ratings yet

- SD Aula05 Memorias Parte 1 MPMDocument20 pagesSD Aula05 Memorias Parte 1 MPMoseiasalbuquerqueNo ratings yet

- Lista 1 Sel415Document3 pagesLista 1 Sel415raulpmicenaNo ratings yet

- Monitoria Prova (Document1 pageMonitoria Prova (Misael MoraisNo ratings yet

- Solution SODocument3 pagesSolution SOElkson Eller100% (2)

- Lista de Exercicios Sistemas Operacionais - Cap 5, 8, 11, 12 e 15Document7 pagesLista de Exercicios Sistemas Operacionais - Cap 5, 8, 11, 12 e 15Paulo HemmelNo ratings yet

- Arquitetura de Computadores - Lista de ExercíciosDocument2 pagesArquitetura de Computadores - Lista de ExercíciosJoao Pedro Da Cunha DiasNo ratings yet

- Ap1 - Questões 11,12,13,14,21,22,25e26Document4 pagesAp1 - Questões 11,12,13,14,21,22,25e26Thiago Francisco Paes AlvesNo ratings yet

- Oc Aula 05Document28 pagesOc Aula 05Raphael QuintanilhaNo ratings yet

- Arquitetura de Computadores – Questionário 7Document5 pagesArquitetura de Computadores – Questionário 7Marcus Ramos0% (1)

- 1a ListaExerciciosDocument4 pages1a ListaExerciciosRilner Azevedo de MucioNo ratings yet

- Memória e Desempenho em Sistemas DigitaisDocument2 pagesMemória e Desempenho em Sistemas DigitaisClarissa Conta pra ndsNo ratings yet

- 2020 - 2 - ARQUITETURA E Organização de Computadores - Tecad: Minhas TurmasDocument1 page2020 - 2 - ARQUITETURA E Organização de Computadores - Tecad: Minhas TurmasBruno MachadoNo ratings yet

- Exercícios MP: Acesso, Endereçamento e OrganizaçãoDocument10 pagesExercícios MP: Acesso, Endereçamento e OrganizaçãoGeorge Felipe100% (1)

- Arquitetura de Computadores - Questionário 7Document5 pagesArquitetura de Computadores - Questionário 7Marcus RamosNo ratings yet

- ExerciciosDocument4 pagesExerciciosMaikon Rodrigues0% (2)

- DocumentoDocument4 pagesDocumentoLord SipriamNo ratings yet

- Provas - 4 AocDocument1 pageProvas - 4 AocWasterman ApolinárioNo ratings yet

- ARQ - Quest 7-v 30-33-Sist Memoria-P 2Document6 pagesARQ - Quest 7-v 30-33-Sist Memoria-P 2Yasmin CristinaNo ratings yet

- Resumo Arqcomp 4.2 - 4.3Document3 pagesResumo Arqcomp 4.2 - 4.3Ana LuisaNo ratings yet

- Funções da UCP e componentes de uma CPUDocument4 pagesFunções da UCP e componentes de uma CPUNatalFonseca0% (2)

- 8086 MICROPROCESSADOR - Linguagem Assembly - Univ MinhoDocument29 pages8086 MICROPROCESSADOR - Linguagem Assembly - Univ MinhoVictorBonfim100% (1)

- AP1 - 2013-2 - Gabarito - Organização de ComputadoresDocument4 pagesAP1 - 2013-2 - Gabarito - Organização de ComputadoresJoeme AlvesNo ratings yet

- Arquitetura de Computadores - Questionário 6Document4 pagesArquitetura de Computadores - Questionário 6Marcus RamosNo ratings yet

- Exercicios Arquitetura e Sistemas de ComputadoresDocument4 pagesExercicios Arquitetura e Sistemas de ComputadoresA Carlos GarciaNo ratings yet

- A Post Il Amemori AsDocument17 pagesA Post Il Amemori AsAlfredo MeurerNo ratings yet

- Projetos No Vb Para Raspberry Pi 3 Com Windows 10 Iot Core Parte IiFrom EverandProjetos No Vb Para Raspberry Pi 3 Com Windows 10 Iot Core Parte IiNo ratings yet

- Projetos No Vc# Para Raspberry Pi 3 Com Windows 10 Iot Core Parte IiFrom EverandProjetos No Vc# Para Raspberry Pi 3 Com Windows 10 Iot Core Parte IiNo ratings yet

- Matemática A - Exponenciais e LogaritmosDocument7 pagesMatemática A - Exponenciais e LogaritmosMatemtica2015No ratings yet

- MKT Digital e relações de consumoDocument3 pagesMKT Digital e relações de consumoBruna Alves Machado0% (1)

- SIPEX - Manual do Sistema de Controle de Protocolo e ExpedienteDocument22 pagesSIPEX - Manual do Sistema de Controle de Protocolo e ExpedientemjsouzasjcNo ratings yet

- Manual Atlas - Ti Tatiana Marceda BachDocument25 pagesManual Atlas - Ti Tatiana Marceda Bachtatibach100% (2)

- Gerenciamento costeiro e zoneamento ecológico-econômico do litoral norte de SPDocument1 pageGerenciamento costeiro e zoneamento ecológico-econômico do litoral norte de SPGustavo Cruz100% (1)

- Fundamentos de lógica e algoritmosDocument44 pagesFundamentos de lógica e algoritmosJomarFerreiraNo ratings yet

- FLStudio básico: introdução aos comandos e criação de projetosDocument21 pagesFLStudio básico: introdução aos comandos e criação de projetosAnderson Silva100% (2)

- Aula 1-Introdução - Aprendizagem de Máquina PDFDocument24 pagesAula 1-Introdução - Aprendizagem de Máquina PDFgustavo_maNo ratings yet

- CursosGratuitosTECNOLOGIADA INFORMACAOSemestre2012Document2 pagesCursosGratuitosTECNOLOGIADA INFORMACAOSemestre2012Dierla Pires CostaNo ratings yet

- Exemplos de Tipos de Gráficos: Aplicação em Dados ReaisDocument16 pagesExemplos de Tipos de Gráficos: Aplicação em Dados Reaisdmd2No ratings yet

- A LEITURA FORA DO LIVRO Lúcia Santaella PDFDocument2 pagesA LEITURA FORA DO LIVRO Lúcia Santaella PDFHenryNo ratings yet

- TCC Vitor Felicio Salema PDFDocument79 pagesTCC Vitor Felicio Salema PDFVítor SalemaNo ratings yet

- Sistema de Gestão de Pedidos para RestaurantesDocument46 pagesSistema de Gestão de Pedidos para Restaurantes@nanesoj0% (1)

- Informática IndustrialDocument30 pagesInformática IndustrialJohn Lopes Jr.No ratings yet

- Plano de Aula LOGISTICADocument2 pagesPlano de Aula LOGISTICACcasue LagutropNo ratings yet

- Metodologia 8D para resolução de problemasDocument3 pagesMetodologia 8D para resolução de problemasRodrigo Noguerol CorreaNo ratings yet

- Notas Sobre o Teorema de Três Séries de KolmogorovDocument12 pagesNotas Sobre o Teorema de Três Séries de KolmogorovRoberto Imbuzeiro OliveiraNo ratings yet

- Consertar Philips PTDocument18 pagesConsertar Philips PTEnrik VillaNo ratings yet

- Criando SQLite offline com HTML5Document6 pagesCriando SQLite offline com HTML5Ricardo RomeroNo ratings yet

- TObjectList - Como Trabalhar Com Coleções de Objetos No DelphiDocument20 pagesTObjectList - Como Trabalhar Com Coleções de Objetos No Delphisantos8santos-2No ratings yet

- Exercicios Balanço de MassaDocument5 pagesExercicios Balanço de MassaAlvaro BenattiNo ratings yet

- Treinamento ARBURG - Basico PDFDocument45 pagesTreinamento ARBURG - Basico PDFrauldd100% (5)

- Ficha Formativa 2Document6 pagesFicha Formativa 2Marisa Cardoso0% (1)

- Exercicios C++Document30 pagesExercicios C++venomvNo ratings yet

- Aprendendo a utilizar a classe LATEX BeamerDocument49 pagesAprendendo a utilizar a classe LATEX Beamerleandro1281No ratings yet

- Programação em TI Voyage 200 Aplicado À EngenhariaDocument88 pagesProgramação em TI Voyage 200 Aplicado À EngenhariaTiago LopesNo ratings yet

- POO RobocodeDocument16 pagesPOO RobocodeMatthew HolmesNo ratings yet

- Signo, Significante e SignificadoDocument4 pagesSigno, Significante e SignificadocoimbravalerioNo ratings yet

- Lista Mestra DocsDocument2 pagesLista Mestra Docssidnei carraschiNo ratings yet

- Scrum - A Metodologia Ágil Explicada de Forma DefinitivaDocument10 pagesScrum - A Metodologia Ágil Explicada de Forma DefinitivabetobitkingNo ratings yet