Professional Documents

Culture Documents

3 D755 D 01

Uploaded by

Roberto C. ArandaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

3 D755 D 01

Uploaded by

Roberto C. ArandaCopyright:

Available Formats

Superficies y Vaco 22 (4) 6-9, diciembre de 2009

Sociedad Mexicana de Ciencia y Tecnologa de Superficies y Materiales

Weak-inversion topologies of analog median filters

Alejandro Daz-Snchez, Jos Miguel Rocha Prez, Javier Lemus-Lpez INAOE Luis E. Erro #1. Tonantzintla, Puebla, Mxico Jaime Ramrez-Angulo* Klipsch School of Electrical and Computer Engineering, New Mexico State University Las Cruces, New Mexico, USA. Germn Ardul Muoz-Hernndez+, Carlos Arturo Gracios-Marn Instituto Tecnolgico de Puebla Av. Tecnolgico 424, Puebla, Puebla, Mxico (Recibido: 10 de julio de 2009; Aceptado: 20 de octubre de 2009)

Design and implementation of two analog median filter cells are described. The first topology is a differential pairs array, which drain currents are driven into two nodes in a differential fashion. The second topology is based on a wide range OTA, which is used as basic block to maximize the dynamic range. Fabrication parameters for a MOSIS process of 1.6 m are used. Experimental results of two three-input fabricated prototypes are shown. Palabras clave: Non-linear Filters; Median Filters; Weak-Inversion

1. Introduction Nonlinear characteristics have made of median filters one of the most widely used in prefiltering applications for signal and image processing [1]. Since median filters are capable of remove impulsive noise and pixel dropouts, while the overall image quality is preserved, they have a great advantage over classical linear image processing. Despite their popularity, real-time digital implementations of median filters are computationally expensive [2, 3]. This is due to the fact that a sorting operation is required for each pixel. Since each element of data must be compared to the others, the circuitry needed to perform the median of a set of data is highly complex and very silicon area intensive. Some works have been directed to reduce the number of data involved in the median computations [3], but parallel implementations of median filters using digital techniques are still not available. Another limitation of digital implementations of median filters is the fact that they are restrained to sequences that require double median computation, increasing hardware complexity. In recent research, some analog implementations of median filters have been reported [2-5]. Their simplicity has allowed some parallelism in image processing applications [6]. However, the most of these applications were based in bipolar transistors or MOS transistors working in the linear or saturation regions, and the total power consumption of those implementations sets a limit in the parallel capabilities of their applications. The present work presents two implementations of median filters, with all the transistors working in the 6

email: adiasan@inaoep.mx *e-mail: jramirez@nmsu.edu +e-mail: gmunoz64@hotmail.com

subthreshold region. The very low power consumption of MOS transistors allows overcoming the power limitations for massive parallel processing implementations. 2. Circuit Description The previously reported applications were based in bipolar transistors or MOS transistors working in the linear or saturation regions [4-6]. The total power consumption of those implementations sets a limit in the parallel capabilities of their applications. Analog circuits using subthreshold CMOS are of common use in applications with very low power consumption requirements [7]. Furthermore, since all the MOS transistors are operating in the limit of the weak-inversion region (~8nA), their current gain is comparable to bipolar transistors; that fact allows the use of single-stage comparators to implement median filters with very low power consumption requirements [8]. The drain-source current in an NMOS transistor operating in the weak-inversion region is given by the equation [8]:

V V V IDS = I0Wexp GB exp SB - exp DB U L Ut Ut t

(1)

where VGB is the gate to bulk voltage, VSB is the source to bulk voltage, VDB is the drain to bulk voltage, I0 is the zero bias current, is the electrostatic source-drain coupling, and Ut is the thermal voltage. It can be observed some similarity with the Ebers-Moll equations, which can be

Superficies y Vaco 22 (4) 6-9, diciembre de 2009

VDD

ML1 ML2

Sociedad Mexicana de Ciencia y Tecnologa de Superficies y Materiales

explained because similar mechanisms are responsible of the current flow in both cases [9]. In a differential pair, if we assume V1 = VCM + VDM/2 and V2 = VCM - VDM/2 [7]:

Vout

Vin1

MA1

MB1

Vin2

MA2

MB2

Vin3

MA3

MB3

V I DM = I b tanh DM 2 Ut

(2)

Vbias

MC1 MC2 MC3

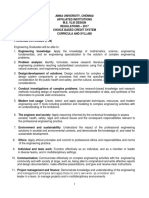

Figure 1. Differential pair-based median detector.

Figure 1 shows a median filter based on basic differential pairs, which transistors, MA1-A3 and MB1-B3 operate in subthreshold region, while MC1-C3 transistors are current sources controlled by voltage Vbias. Transistors ML1 and ML2 are used as active loads at figure 1. A high current gain is obtained for small variations of the input voltage for Vout greater than 0.5 (saturation condition [7]). Since input signal is limited to a minimum of 0.5 volts, all six transistors will be in saturation. During circuit operation, the output of the OTA's that can not follow the input will saturate in an alternate way, compensating these output saturation currents. Meanwhile, the other OTA will try to maintain the differences between the positive and negative inputs equal to zero, and that will maintain the median of the voltages at the output. Figure 2 shows the performance of a simulated three input median circuit. 3. Wide range median detector

Q4

Figure 2. Performance of simulated three input median circuit.

VDD

Q3 Q5 Q6

Q11 Q21 V1 QB1 Vbias V2

Q12 Q22 V3 QB2

V out Q 13 Q23

QB3

Q7

Q8

Figure 3. Wide band range median detector.

Figure 3 shows a 3-input standard cell median, using a parallel structure [10]. In this approximation, the median filter is implemented using an extended-range amplifier [10]. Since a simple operational transconductance amplifier will not generate output voltages below Vmin [8], the wide range amplifier uses two current mirrors to reflect the currents in the differential pair into the output node. Drain currents of Q11-13 are connected to the output through the current mirrors formed by Q5-Q6 and Q7-Q8, while drain currents of Q21-23 are connected to the output using the current mirror Q3-Q4. Since the output voltage has no effect on the input transistors, it has a range from VDD to ground. During circuit operation, the output of the input cells that can not follow the input will saturate in an alternate way, compensating these output saturation currents, while the other input cell will try to maintain the differences between the positive and negative inputs equal to zero, and that will maintain the median of the voltages at the output. 4. Results A microphotography of the differential-pair based median filter fabricated prototype is shown in Figure 4. Nchannel transistors have dimensions of W= 8 m and L=5m, and a bias currents of 3 nA. Figure 5 shows the experimental results. Figure 6 shows the fabricated prototype of a wide range median detector, while Figure 7 shows the experimental results. 7

Figure 4. Microphotograph of the differential-pair based prototype.

Superficies y Vaco 22 (4) 6-9, diciembre de 2009

Sociedad Mexicana de Ciencia y Tecnologa de Superficies y Materiales

a)

(b)

Figure 5. Experimental results of the differential-pair based prototype.

(c) Figure. 8. a). Original Image, b). Image corrupted with 15% salt and pepper noise, c). Reconstructed image.

Figure 6. Fabricated prototype of a wide range median detector.

Figure 8.b shows an image of 89 x 79 pixels corrupted with fifteen percent of additive impulsive noise. The range of the input signal will be from 0.25 volts to 1.15 volts, above the minimum voltage allowed. That input image is applied to an array of 88 x 78 basic median standard cell of 3 x 3 and the output is shown in figure 8.c. The total power consumption of the array will be less than 800 microwatts. The image was generated and corrupted using MATLAB. A single 2.5 V voltage is used as power supply. The presented median filters operate with very low power consumption. For a 3 x 3 median filtering cell, the estimated total power is less than 80 nanowatts. 5. Conclusions Two analog median filters, operating at the subthreshold region, have been described. Experimental results for threeinput median detectors have been presented. The image filters have nine inputs, presented as a cell array of 3 x 3, and a single input. Simulated results demonstrate the feasibility of the approximation. The main characteristic of the systems is the very low power consumption of each cell. In addition, their simplicity will allow the massive implementation of median filters array for prefiltering applications. Since power consumption has been overcome, the possibility of using a median filter for each individual pixel in an image acquisition system is possible. The mean convergence time was around 2 microseconds. Despite the circuits simplicity, the interconnection problem remains. Some masks with reduced neighborhood interconnection can be used to solve the problem.

Figure 7. Experimental results of the wide range median detector.

Superficies y Vaco 22 (4) 6-9, diciembre de 2009

Sociedad Mexicana de Ciencia y Tecnologa de Superficies y Materiales

Referencias [1]. I. Pitas and A. Venetsanopoulos, Nonlinear Digital Filters: Principles and Applications (Kluwer Academic Publishers, Boston, 1990). [2]. D. Richards, VLSI Median Filters, IEEE Trans. on Acoustic, Speech and Signal Proc, 38, 2, (1990). [3]. M. Karaman, L. Onural and A. Atalar, in: VLSI Signal Processing III, Eds. R.W. Brodersen and H.S. Moscowitz (IEEE Press, New York, 1988). [4]. P. H. Dietz and L.R. Carley, An Analog Technique for Finding the Median, in Proc. IEEE Custom Int. Circ. Conf., (1993).

[5]. I. Opris and G. Kovacs, Improved Analogue Median Filter, Elect. Letters, 30, 4 (1994). [6]. A. Diaz-Sanchez, J. Ramirez-Angulo, A. Lopez and E. Sanchez-Sinencio, A Fully Parallel Analog Median Filter, IEEE Trans. on Circ. and Syst. II, (2004). [7]. P. Furth and A. Andreou, Transconductors in Subthreshold MOS, 29th Conf. on Inf. Sci. and Syst., (Baltimore, 1993). [8]. A.G. Andreou and K. Boahen, in: Analog VLSI Signal and Information Processing, Eds. M. Ismail and T. Feiz, (McGrawHill, 1994). [9]. Y. Tsividis, Operation and Modeling of the MOS Transistor, (McGraw-Hill International Editions, Singapore, 1999). [10]. C. Mead, Analog VLSI and Neural Systems, (AddisonWesley, Reading, MA, 1989).

You might also like

- Cross-Layer Resource Allocation in Wireless Communications: Techniques and Models from PHY and MAC Layer InteractionFrom EverandCross-Layer Resource Allocation in Wireless Communications: Techniques and Models from PHY and MAC Layer InteractionNo ratings yet

- Spline and Spline Wavelet Methods with Applications to Signal and Image Processing: Volume III: Selected TopicsFrom EverandSpline and Spline Wavelet Methods with Applications to Signal and Image Processing: Volume III: Selected TopicsNo ratings yet

- Methodology For Efficient Substrate Noise Analysis in Large-Scale Mixed-Signal CircuitsDocument14 pagesMethodology For Efficient Substrate Noise Analysis in Large-Scale Mixed-Signal Circuits원성규No ratings yet

- Microstrip Coupled Line Filter Design For Ultra Wideband ApplicationsDocument9 pagesMicrostrip Coupled Line Filter Design For Ultra Wideband Applicationsjmicrojouranl1No ratings yet

- Macromodel ExtractionDocument11 pagesMacromodel Extractionapi-19668941No ratings yet

- Fault IdentificationDocument5 pagesFault IdentificationRajesh Kumar PatnaikNo ratings yet

- Parametros de Cables SubterraneosDocument8 pagesParametros de Cables SubterraneosMarcos EmmanuelNo ratings yet

- Impedance Spectroscopy Cell Analysis in Microchannels Impedance Spectroscopy Cell Analysis in MicrochannelsDocument2 pagesImpedance Spectroscopy Cell Analysis in Microchannels Impedance Spectroscopy Cell Analysis in MicrochannelsPankaj AgarwalNo ratings yet

- ةىةDocument7 pagesةىةWiam KhettabNo ratings yet

- Printed BPF For L BandDocument3 pagesPrinted BPF For L Bandalokcena007No ratings yet

- New Formulas For Synthesizing Microstrip BandpassDocument3 pagesNew Formulas For Synthesizing Microstrip Bandpassagmnm1962No ratings yet

- Evolution of Base Stations in Cellular Networks: Denser Deployment Versus CoordinationDocument5 pagesEvolution of Base Stations in Cellular Networks: Denser Deployment Versus Coordinationsans00nNo ratings yet

- Improved Coupled-Microstrip Filter Design Using Effective Even-Mode and Odd-Mode Characteristic ImpedancesDocument7 pagesImproved Coupled-Microstrip Filter Design Using Effective Even-Mode and Odd-Mode Characteristic ImpedancesAli SigNo ratings yet

- A Circuit-Theoretic ApproachDocument5 pagesA Circuit-Theoretic Approachesra8No ratings yet

- Fault Identification of Overhead Transmission Lines Terminated With Underground CablesDocument7 pagesFault Identification of Overhead Transmission Lines Terminated With Underground CablesVikash Vicky KumarNo ratings yet

- Leakage Reduction in CmosDocument9 pagesLeakage Reduction in CmosPawan SehgalNo ratings yet

- A Linear Programming Based Static Power Optimization Scheme For Digital CMOS Circuits AMSC 662 - Project ProposalDocument3 pagesA Linear Programming Based Static Power Optimization Scheme For Digital CMOS Circuits AMSC 662 - Project ProposalSatish Babu BodakuntaNo ratings yet

- Skin Effect and Dielectric Loss Models of Power Cables 04784562Document8 pagesSkin Effect and Dielectric Loss Models of Power Cables 04784562Gilberto Mejía100% (1)

- Using Parametric Simulation To Optimize Wimax Antenna PerformanceDocument10 pagesUsing Parametric Simulation To Optimize Wimax Antenna PerformanceAntonioNo ratings yet

- 1361 AbdelkrimTDocument6 pages1361 AbdelkrimTLiviu BadeaNo ratings yet

- A Four Electrode BIOZ Physio Measur 2013Document16 pagesA Four Electrode BIOZ Physio Measur 2013Humaira ZulkifliNo ratings yet

- Bioelectronics For Amperometric Biosensors - 43463Document34 pagesBioelectronics For Amperometric Biosensors - 43463Jose TrianoNo ratings yet

- 3 - Two Methods For The Measurement of Substrate Dielectric Constant-Das-D PozarDocument7 pages3 - Two Methods For The Measurement of Substrate Dielectric Constant-Das-D PozarKunal NateNo ratings yet

- Power Splitter 08Document3 pagesPower Splitter 08Umar KhanNo ratings yet

- Random Dopant Induced Variability in Nano CMOSDocument10 pagesRandom Dopant Induced Variability in Nano CMOSsunilkmch505682No ratings yet

- Microwave Filter DesignDocument50 pagesMicrowave Filter Designsimsook91100% (1)

- A Design Methodology Using The Inversion Coefficient For Low-Voltage Low-Power CMOS Voltage ReferencesDocument11 pagesA Design Methodology Using The Inversion Coefficient For Low-Voltage Low-Power CMOS Voltage ReferencesVenkatesh DonepudiNo ratings yet

- Ungrounded System Fault Section Detection Method by Comparison of Phase Angle of Zero-Sequence CurrentDocument7 pagesUngrounded System Fault Section Detection Method by Comparison of Phase Angle of Zero-Sequence Currentjobpei2No ratings yet

- Nano 5Document18 pagesNano 5caralbmarbat_3207679No ratings yet

- k1 FCL DigSilentDocument8 pagesk1 FCL DigSilentksg9731No ratings yet

- Application of Artificial Neural Network For Path Loss Prediction in Urban Macrocellular EnvironmentDocument6 pagesApplication of Artificial Neural Network For Path Loss Prediction in Urban Macrocellular EnvironmentAJER JOURNALNo ratings yet

- On The Analysis and Design of Reconfigurable Multimode MIMO Microstrip AntennasDocument11 pagesOn The Analysis and Design of Reconfigurable Multimode MIMO Microstrip AntennasraktimguhaNo ratings yet

- Evaluation of Three-Phase Transformerless Photovoltaic Inverter TopologiesDocument10 pagesEvaluation of Three-Phase Transformerless Photovoltaic Inverter TopologiesLuis Cáceres VergaraNo ratings yet

- Broadside CouplerDocument6 pagesBroadside CouplerBen WalpoleNo ratings yet

- Conducted EMI Simulation of Switched Mode PDFDocument6 pagesConducted EMI Simulation of Switched Mode PDFPrabhu KumaraswamyNo ratings yet

- Identification of Brushless Excitation System Model Parameters at Different Operating Conditions Via Field TestsDocument7 pagesIdentification of Brushless Excitation System Model Parameters at Different Operating Conditions Via Field TestsFrozzy17No ratings yet

- Work RDDS EBSCO 12635660 6614716d8d2b8Document13 pagesWork RDDS EBSCO 12635660 6614716d8d2b8asNo ratings yet

- 05682957Document4 pages05682957Praveenkumar ViswanathanNo ratings yet

- Characterization of Atmospheric Pressure Discharges: R.Barni, S.Zanini, R.Siliprandi, P.Esena, C.RiccardiDocument8 pagesCharacterization of Atmospheric Pressure Discharges: R.Barni, S.Zanini, R.Siliprandi, P.Esena, C.RiccardiRodrigo RamosNo ratings yet

- A - New - Process - Simulator - For - The - Optimization of Electron Beam Crosslinking ProcessesDocument7 pagesA - New - Process - Simulator - For - The - Optimization of Electron Beam Crosslinking ProcessesAroop Ratan SenNo ratings yet

- CIRED2011 1286 Final Universidad de OviedoDocument4 pagesCIRED2011 1286 Final Universidad de OviedopipotxNo ratings yet

- Versatile Insensitive Current-Mode Universal Biquad Implementation Using Current ConveyorsDocument5 pagesVersatile Insensitive Current-Mode Universal Biquad Implementation Using Current ConveyorsMohamed DhiebNo ratings yet

- Design and Optimization of ÷8/9 Divider in PLL Frequency Synthesizer With Dynamic Logic (E - TSPC)Document5 pagesDesign and Optimization of ÷8/9 Divider in PLL Frequency Synthesizer With Dynamic Logic (E - TSPC)himaja1No ratings yet

- Modeling and Characterizing Supercapacitors Using An Online MethodDocument11 pagesModeling and Characterizing Supercapacitors Using An Online MethodEdu Daryl MacerenNo ratings yet

- 2009 EMC Industrial Inverter Aime CN57Document2 pages2009 EMC Industrial Inverter Aime CN57Juan Gil RocaNo ratings yet

- Subthreshold Source-Coupled Logic Circuits For Ultra-Low-Power ApplicationsDocument12 pagesSubthreshold Source-Coupled Logic Circuits For Ultra-Low-Power ApplicationsSonu SangwanNo ratings yet

- The Monte Carlo Method For Semiconductor Device SimulationDocument5 pagesThe Monte Carlo Method For Semiconductor Device SimulationPRATEEK1469WOWNo ratings yet

- 2009 Pim RC Self OrganizationDocument6 pages2009 Pim RC Self OrganizationSawsan SaadNo ratings yet

- A Wavelet-Based Algorithm For Disturbances Detection Using Oscillographic DataDocument6 pagesA Wavelet-Based Algorithm For Disturbances Detection Using Oscillographic DataVijay KrishnaNo ratings yet

- CORPOELECDocument33 pagesCORPOELECjoelNo ratings yet

- Doppler Frequency...Document6 pagesDoppler Frequency...noumsi briceNo ratings yet

- Paper 13Document5 pagesPaper 13Reena PalNo ratings yet

- Multichannel Wireless Cortical Recording: System: Circuits, Design Assembly ChallengesDocument4 pagesMultichannel Wireless Cortical Recording: System: Circuits, Design Assembly ChallengesAlex WongNo ratings yet

- Design of A Patch Antenna With Integration Cellular Automata and Genetic AlgorithmDocument6 pagesDesign of A Patch Antenna With Integration Cellular Automata and Genetic AlgorithmjozammNo ratings yet

- Electric Field Mapping in High Voltage Substation Using The Finite Elements MethodDocument5 pagesElectric Field Mapping in High Voltage Substation Using The Finite Elements MethodRafael BarrosNo ratings yet

- Low Power-Area Designs of 1bit Full Adder in Cadence Virtuoso PlatformDocument10 pagesLow Power-Area Designs of 1bit Full Adder in Cadence Virtuoso PlatformAnonymous e4UpOQEPNo ratings yet

- EIS Guide v2Document12 pagesEIS Guide v2gpaivNo ratings yet

- 6 Shielded MicrostripDocument5 pages6 Shielded MicrostripV'nod Rathode BNo ratings yet

- Passive Trap Filter For Harmonic ReductionDocument9 pagesPassive Trap Filter For Harmonic ReductionShiva KumarNo ratings yet

- Series Impedance of Distribution Cables With Sector-Shaped ConductorsDocument8 pagesSeries Impedance of Distribution Cables With Sector-Shaped Conductorstees220510No ratings yet

- Ficha Técnica Contactores Allen BradleyDocument2 pagesFicha Técnica Contactores Allen BradleyAndrea NeyraNo ratings yet

- bq769x0 3-Series To 15-Series Cell Battery Monitor Family For Li-Ion and Phosphate ApplicationsDocument66 pagesbq769x0 3-Series To 15-Series Cell Battery Monitor Family For Li-Ion and Phosphate ApplicationsĐạt Trần DoãnNo ratings yet

- Backend (Physical Design) Interview Questions and Answers GGDocument6 pagesBackend (Physical Design) Interview Questions and Answers GGRohith RajNo ratings yet

- Low Power VLSI Circuits and Systems Prof. Ajit Pal Department of Computer Science and Engineering Indian Institute of Technology, KharagpurDocument23 pagesLow Power VLSI Circuits and Systems Prof. Ajit Pal Department of Computer Science and Engineering Indian Institute of Technology, KharagpurHimaja DasariNo ratings yet

- Cable Sizing CalculationDocument28 pagesCable Sizing CalculationEmmanuel IfedioraNo ratings yet

- Minew BLE Module Roadmap Q1 2021Document12 pagesMinew BLE Module Roadmap Q1 2021Bieng Loic parfaitNo ratings yet

- Low Cost, Precision 2.5 V IC References AD1403/AD1403ADocument4 pagesLow Cost, Precision 2.5 V IC References AD1403/AD1403AaseelNo ratings yet

- Low-Power Digital VLSI DesignDocument530 pagesLow-Power Digital VLSI DesignAllanki Sanyasi Rao50% (2)

- High Performance ALU Design Using Energy Efficient Borrow Select SubtractorDocument65 pagesHigh Performance ALU Design Using Energy Efficient Borrow Select SubtractorKarthiga MuruganNo ratings yet

- THINGSYS-4G GPS TrackersCatalog QuotationList 202312 ENDocument1 pageTHINGSYS-4G GPS TrackersCatalog QuotationList 202312 ENdesarrollostecnologicosfjcaNo ratings yet

- Innovative Line SensorDocument4 pagesInnovative Line SensorXavier Pacheco PaulinoNo ratings yet

- Techniques For Low Power VLSI Design: A Novel Analysis of Leakage Power ReductionDocument4 pagesTechniques For Low Power VLSI Design: A Novel Analysis of Leakage Power ReductionSaranya RamaswamyNo ratings yet

- Design Report For The White Russian Unmanned Ground Vehicle: York College of PennsylvaniaDocument17 pagesDesign Report For The White Russian Unmanned Ground Vehicle: York College of Pennsylvaniasteve4ovenNo ratings yet

- Sam 4 LqwecDocument1,207 pagesSam 4 LqwecBogdan VladNo ratings yet

- Thesis On LFSRDocument104 pagesThesis On LFSRKaran RoyNo ratings yet

- 15A04802 Low Power VLSI Circuits & SystemsDocument1 page15A04802 Low Power VLSI Circuits & SystemsMALLAVARAPU NARASAREDDYNo ratings yet

- 2.5nW Subthreshold VCO Based CMOS Temperature Sensor: Waseem Arshad, Rashad Ramzan, Azam Beg, and Nabil BastakiDocument4 pages2.5nW Subthreshold VCO Based CMOS Temperature Sensor: Waseem Arshad, Rashad Ramzan, Azam Beg, and Nabil BastakiMuhammad YousafNo ratings yet

- Low Power Vlsi Designphd ThesisDocument8 pagesLow Power Vlsi Designphd ThesisJim Jimenez100% (2)

- Chapter 12 - AVR Microcontrollers-Features, Architecture Assembly LanguageDocument131 pagesChapter 12 - AVR Microcontrollers-Features, Architecture Assembly LanguageErgin Özdikicioğlu100% (1)

- Energy Efficient Cmos Full-Adders For Arthmetic ApplicationsDocument24 pagesEnergy Efficient Cmos Full-Adders For Arthmetic Applicationsbalakrishna_battaNo ratings yet

- Amv01 3928375Document2 pagesAmv01 3928375Oscar RamirezNo ratings yet

- Position Sensing in Gaming, AR, and VR ControllersDocument3 pagesPosition Sensing in Gaming, AR, and VR Controllersthomas yenNo ratings yet

- M.E.VLSI DesignDocument43 pagesM.E.VLSI DesignThahsin ThahirNo ratings yet

- Low-Power VLSI Design TOCDocument3 pagesLow-Power VLSI Design TOCkipanderson21No ratings yet

- Stpmic 1Document140 pagesStpmic 1Riko AndiaNo ratings yet

- Is 63 LV 1024Document8 pagesIs 63 LV 1024dragon-red0816No ratings yet

- Document Title: GM76C256CDocument11 pagesDocument Title: GM76C256CFrenk EndyNo ratings yet

- Pipelining and Parallel ProcessingDocument37 pagesPipelining and Parallel ProcessingvinyroseNo ratings yet

- Low Power ROMDocument5 pagesLow Power ROMParul JohariNo ratings yet

- A New Design 6T Full Adder Circuit Using Novel 2T XNOR GatesDocument7 pagesA New Design 6T Full Adder Circuit Using Novel 2T XNOR GatesdycsteiznNo ratings yet