Professional Documents

Culture Documents

Hy27uf084g2m Series (Rev.0.7)

Uploaded by

Pt DuongOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Hy27uf084g2m Series (Rev.0.7)

Uploaded by

Pt DuongCopyright:

Available Formats

This document is a general product descript ion and is subj ect t o change wit hout not ice.

ice. Hynix does not assume any responsibilit y for

use of circuit s described. No pat ent licenses are implied.

Rev. 0.7 / Dec. 2006 1

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

4Gb NAND FLASH

HY27UF084G2M

Rev. 0.7 / Dec. 2006 2

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Document Ti t l e

4Gbi t ( 512Mx8bi t ) NAND Fl ash Memor y

Revi si on Hi st or y

Revi si on

No.

Hi st or y Dr af t Dat e Remar k

0.0 I nit ial Draft . Dec. 2004 I nit ial

0.1

1) Add ULGA Package.

- Figures & t ext s are added.

2) Add Read I D Table

3) Correct t he t est Condit ions (DC Charact erist ics t able)

3) Change AC Condit ions t able

4) Add t WW paramet er ( t WW = 100ns, min)

- Text s & Figures are added.

- t WW is added in AC t iming charact erist ics t able.

4) Edit Syst em I nt erface Using CE dont care.

5) Add Marking I nformat ion.

6) Correct Address Cycle Map.

7) Correct PKG dimension ( TSOP PKG)

8) Delet e t he 1.8V devices feat ures.

Aug. 08. 2005 Preliminary

Test Condit ions (I LI , I LO)

Before VI N= VOUT= 0 t o 3.6V

Aft er VI N= VOUT= 0 t o Vcc (max)

CP

Before 0.050

Aft er 0.100

Rev. 0.7 / Dec. 2006 3

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Revi si on Hi st or y -Cont i nued-

Revi si on

No.

Hi st or y Dr af t Dat e Remar k

0.2

1) Change AC Charact erist ics

2) Add t CRRH (100ns, Min)

- t CRRH : Cache Read RE High

3) Change 3rd Read I D

- 3rd Read I D is changed t o 80h

- 3rd Byt e of Device I dent ifier Table is added.

4) Change NOP

- Number of part ial Program Cycle in t he same page is changed t o 4.

Oct . 08. 2005 Preliminary

0.3

1) Change AC Charact erist ics

Nov. 16. 2005 Preliminary

0.4

1) Add ECC algorit hm. (1bit / 512byt es)

2) Change NOP

3) Correct Read I D naming

Jun. 20. 2006 Preliminary

0.5 1) Delet Preliminary. Jul. 10. 2006

0.6 1) Correct copy back funct ion. Oct . 02. 2006

0.7

1) Delet e PRE funct ion.

2) Delet e Lock & Unlock funct ion.

3) Delet e Aut o Read funct ion.

Dec. 26. 2006

t R t AR t REA t RHZ t CHZ t CEA

Before 20 10 18 30 30 25

Aft er 25 15 20 50 50 35

t CLS t WP t DS t WC t ADL t RP t RC

Before 12 12 12 25 70 12 25

Aft er 15 15 15 30 100 15 30

t REA t CEA t CS

Before 20 35 20

Aft er 25 30 25

Rev. 0.7 / Dec. 2006 4

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

FEATURES SUMMARY

HI GH DENSI TY NAND FLASH MEMORI ES

- Cost effect ive solut ions for mass st orage applicat ions

NAND I NTERFACE

- x8 widt h.

- Mult iplexed Address/ Dat a

- Pinout compat ibility for all densit ies

SUPPLY VOLTAGE

- 3.3V device: VCC = 2.7 t o 3.6V : HY27UF084G2M

Memor y Cel l Ar r ay

= (2K+ 64) Byt es x 64 Pages x 4,096 Blocks

PAGE SI ZE

- x8 device : (2K + 64 spare) Byt es

: HY27UF084G2M

BLOCK SI ZE

- x8 device: (128K + 4K spare) Byt es

PAGE READ / PROGRAM

- Random access: 25us (max.)

- Sequent ial access: 30ns (min.)

- Page program t ime: 200us (t yp.)

COPY BACK PROGRAM MODE

- Fast page copy wit hout ext ernal buffering

CACHE PROGRAM MODE

- I nt ernal Cache Regist er t o improve t he program

t hroughput

FAST BLOCK ERASE

- Block erase t ime: 2ms ( Typ.)

STATUS REGI STER

ELECTRONI C SI GNATURE

- 1st cycle : Manufact urer Code

- 2nd cycle: Device Code

CHI P ENABLE DON' T CARE

- Simple int erface wit h microcont roller

SERI AL NUMBER OPTI ON

HARDWARE DATA PROTECTI ON

- Program/ Erase locked during Power t ransit ions

DATA I NTEGRI TY

- 100,000 Program/ Erase cycles (wit h 1bit / 512byt e ECC)

- 10 years Dat a Ret ent ion

PACKAGE

- HY27UF084G2M-T(P)

: 48-Pin TSOP1 (12 x 20 x 1.2 mm)

- HY27UF084G2M-T (Lead)

- HY27UF084G2M-TP (Lead Free)

- HY27UF084G2M-UP

: 52-ULGA (12 x 17 x 0.65 mm)

- HY27UF084G2M-UP (Lead Free)

Rev. 0.7 / Dec. 2006 5

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

1. SUMMARY DESCRI PTI ON

The HYNI X HY27UF084G2M series is a 512Mx8bit wit h spare 16Mx8 bit capacit y. The device is offered in 3.3V Vcc

Power Supply.

I t s NAND cell provides t he most cost-effect ive solut ion for t he solid st at e mass st orage market .

The memory is divided int o blocks t hat can be erased independent ly so it is possible t o preserve valid dat a while old

dat a is erased.

The device cont ains 4096 blocks, composed by 64 pages consist ing in t wo NAND st ruct ures of 32 series connect ed

Flash cells.

A program operat ion allows t o writ e t he 2112-byt e page in typical 200us and an erase operat ion can be performed in

typical 2ms on a 128K-byt e(X8 device) block.

Dat a in t he page mode can be read out at 30ns cycle t ime per byt e. The I / O pins serve as t he port s for address and

dat a input / out put as well as command input . This int erface allows a reduced pin count and easy migrat ion t owards dif-

ferent densit ies, wit hout any rearrangement of foot print .

Commands, Dat a and Addresses are synchronously int roduced using CE, WE, ALE and CLE input pin.

The on-chip Program/ Erase Cont roller aut omat es all program and erase funct ions including pulse repet it ion, where

required, and int ernal verificat ion and margining of dat a.

The modifying can be locked using t he WP input pin.

The out put pin R/ B (open drain buffer) signals t he st at us of t he device during each operat ion. I n a syst em wit h mult i-

ple memories t he R/ B pins can be connect ed all t oget her t o provide a global st at us signal.

Even t he writ e-int ensive syst ems can t ake advant age of t he HY27UF084G2M ext ended reliability of 100K program/

erase cycles by providing ECC ( Error Correct ing Code) wit h real t ime mapping-out algorit hm.

The chip could be offered wit h t he CE dont care funct ion. This funct ion allows t he direct download of t he code from

t he NAND Flash memory device by a microcont roller, since t he CE t ransit ions do not st op t he read operat ion.

The copy back funct ion allows t he opt imizat ion of defect ive blocks management : when a page program operat ion fails

t he dat a can be direct ly programmed in anot her page inside t he same array sect ion wit hout t he t ime consuming serial

dat a insert ion phase.

The cache program feat ure allows t he dat a insert ion in t he cache regist er while t he dat a regist er is copied int o t he

flash array. This pipelined program operat ion improves t he program t hroughput when long files are writ t en inside t he

memory.

A cache read feat ure is also implement ed. This feat ure allows t o dramat ically improve t he read t hroughput when con-

secut ive pages have t o be st reamed out .

This device includes also ext ra feat ures like OTP/ Unique I D area, Read I D2 ext ension.

The HYNI X HY27UF084G2M series is available in 48 - TSOP1 12 x 20 mm, 52-ULGA 12 x 17 mm.

1.1 Pr oduct Li st

PART NUMBER ORI ZATI ON VCC RANGE PACKAGE

HY27UF084G2M x8 2.7V - 3.6 Volt 48TSOP1 / 52-ULGA

Rev. 0.7 / Dec. 2006 6

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Fi gur e1: Logi c Di agr am

VCC

VSS

WP

CLE

ALE

RE

WE

CE IO0~IO7

RJB

I O7 - I O0 Dat a I nput / Out put s

CLE Command lat ch enable

ALE Address lat ch enable

CE Chip Enable

RE Read Enable

WE Writ e Enable

WP Writ e Prot ect

R/ B Ready / Busy

Vcc Power Supply

Vss Ground

NC No Connect ion

Tabl e 1: Si gnal Names

Rev. 0.7 / Dec. 2006 7

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Fi gur e 2. 48TSOP1 Cont act i ons, x8 Devi ce

NC

NC

NC

NC

NC

NC

RfB

RE

CE

NC

NC

vcc

vss

NC

NC

CLE

ALE

WE

WP

NC

NC

NC

NC

NC

NC

NC

NC

NC

!fO7

!fO6

!fOS

!fO+

NC

NC

NC

vcc

vss

NC

NC

NC

!fO3

!fO2

!fO1

!fO0

NC

NC

NC

NC

12

13

37

36

2S

+8 1

2+

NAND Flash

TSOP1

{xS)

Rev. 0.7 / Dec. 2006 8

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

/WE

/WP

VSS

O0

O1

O2 O6

O7

O5

O4

VSS

O3

R/B

NC

NC

NC

NC

NC

NC NC NC

NC

VSS

VSS

VCC

VCC

NC

CLE

ALE

/CE

/RE

NC

NC NC

NC

NC

NC

NC

NC

NC

A

B

C

D

E

F

G

H

J

K

L

M

N

1 2 3 4 5 6 7

Fi gur e 3. 52- ULGA Cont act i ons, x8 Devi ce ( Top vi ew t hr ough package)

Rev. 0.7 / Dec. 2006 9

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

1.2 PI N DESCRI PTI ON

Pi n Name Descri pt i on

I O0-I O7

DATA I NPUTS/ OUTPUTS

The I O pins allow t o input command, address and dat a and t o out put dat a during read / program

operat ions. The input s are lat ched on t he rising edge of Writ e Enable (WE). The I / O buffer float t o

High-Z when t he device is deselect ed or t he out put s are disabled.

CLE

COMMAND LATCH ENABLE

This input act ivat es t he lat ching of t he I O input s inside t he Command Regist er on t he Rising edge of

Writ e Enable (WE) .

ALE

ADDRESS LATCH ENABLE

This input act ivat es t he lat ching of t he I O input s inside t he Address Regist er on t he Rising edge of

Writ e Enable (WE) .

CE

CHI P ENABLE

This input cont rols t he select ion of t he device. When t he device is busy CE low does not deselect t he

memory.

WE

WRI TE ENABLE

This input act s as clock t o lat ch Command, Address and Dat a. The I O input s are lat ched on t he rise

edge of WE.

RE

READ ENABLE

The RE input is t he serial dat a-out cont rol, and when act ive drives t he dat a ont o t he I / O bus. Dat a is

valid t REA aft er t he falling edge of RE which also increment s t he int ernal column address count er by

one.

WP

WRI TE PROTECT

The WP pin, when Low, provides an Hardware prot ect ion against undesired modify (program / erase)

operat ions.

R/ B

READY BUSY

The Ready/ Busy out put is an Open Drain pin t hat signals t he st at e of t he memory.

VCC

SUPPLY VOLTAGE

The VCC supplies t he power for all t he operat ions (Read, Writ e, Erase).

VSS GROUND

NC NO CONNECTI ON

Tabl e 2: Pi n Descr i pt i on

NOTE:

1. A 0.1uF capacit or should be connect ed bet ween t he VCC Supply Volt age pin and t he VSS Ground pin t o decouple

t he current surges from t he power supply. The PCB t rack widt hs must be sufficient t o carry t he current s required

during program and erase operat ions.

Rev. 0.7 / Dec. 2006 10

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

I O0 I O1 I O2 I O3 I O4 I O5 I O6 I O7

1st Cycl e A0 A1 A2 A3 A4 A5 A6 A7

2nd Cycl e A8 A9 A10 A11 L

(1)

L

(1)

L

(1)

L

(1)

3r d Cycl e A12 A13 A14 A15 A16 A17 A18 A19

4t h Cycl e A20 A21 A22 A23 A24 A25 A26 A27

5t h Cycl e A28 A29 L

(1)

L

(1)

L

(1)

L

(1)

L

(1)

L

(1)

Tabl e 3: Addr ess Cycl e Map( x8)

NOTE:

1. L must be set t o Low.

FUNCTI ON 1st CYCLE 2nd CYCLE 3r d CYCLE

Accept abl e command

dur i ng busy

READ 1 00h 30h -

READ FOR COPY-BACK 00h 35h -

READ I D 90h - -

RESET FFh - - Yes

PAGE PROGRAM ( st art ) 80h 10h -

COPY BACK PGM ( st ar t ) 85h 10h -

CACHE PROGRAM 80h 15h -

BLOCK ERASE 60h D0h -

READ STATUS REGI STER 70h - - Yes

RANDOM DATA I NPUT 85h - -

RANDOM DATA OUTPUT 05h E0h -

CACHE READ START 00h 31h -

CACHE READ EXI T 34h - -

Tabl e 4: Command Set

Rev. 0.7 / Dec. 2006 11

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

CLE ALE CE WE RE WP MODE

H L L Rising H X

Read Mode

Command I nput

L H L Rising H X Address I nput (5 cycles)

H L L Rising H H

Writ e Mode

Command I nput

L H L Rising H H Address I nput (5 cycles)

L L L Rising H H Dat a I nput

L L

L

(1)

H Falling X Sequent ial Read and Dat a Out put

L L L H H X During Read ( Busy)

X X X X X H During Program ( Busy)

X X X X X H During Erase ( Busy)

X X X X X L Writ e Prot ect

X X H X X 0V/ Vcc St and By

Tabl e 5: Mode Sel ect i on

NOTE:

1. Wit h t he CE high during lat ency t ime does not st op t he read operat ion

Rev. 0.7 / Dec. 2006 12

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

2. BUS OPERATI ON

There are six st andard bus operat ions t hat cont rol t he device. These are Command I nput , Address I nput , Dat a I nput ,

Dat a Out put , Writ e Prot ect , and St andby.

Typically glit ches less t han 5 ns on Chip Enable, Writ e Enable and Read Enable are ignored by t he memory and do not

affect bus operat ions.

2.1 Command I nput .

Command I nput bus operat ion is used t o give a command t o t he memory device. Command are accept ed wit h Chip

Enable low, Command Lat ch Enable High, Address Lat ch Enable low and Read Enable High and lat ched on t he rising

edge of Writ e Enable. Moreover for commands t hat st art s a modifying operat ion (writ e/ erase) t he Writ e Prot ect pin

must be high. See figure 5 and t able 12 for det ails of t he t imings requirement s. Command codes are always applied on

I O7: 0, disregarding t he bus configurat ion (X8).

2.2 Addr ess I nput .

Address I nput bus operat ion allows t he insert ion of t he memory address. To insert t he 29 addresses needed t o access

t he 4Gbit 5 clock cycles are needed. Addresses are accept ed wit h Chip Enable low, Address Lat ch Enable High, Com-

mand Lat ch Enable low and Read Enable high and lat ched on t he rising edge of Writ e Enable. Moreover for commands

t hat st art s a modify operat ion (writ e/ erase) t he Writ e Prot ect pin must be high. See figure 6 and t able 12 for det ails of

t he t imings requirement s. Addresses are always applied on I O7: 0, disregarding t he bus configurat ion (X8).

2.3 Dat a I nput .

Dat a I nput bus operat ion allows t o feed t o t he device t he dat a t o be programmed. The dat a insert ion is serially and

t imed by t he Writ e Enable cycles. Dat a are accept ed only wit h Chip Enable low, Address Lat ch Enable low, Command

Lat ch Enable low, Read Enable High, and Writ e Prot ect High and lat ched on t he rising edge of Writ e Enable. See figure

7 and t able 12 for det ails of t he t imings requirement s.

2.4 Dat a Out put .

Dat a Out put bus operat ion allows t o read dat a from t he memory array and t o check t he st at us regist er cont ent , t he I D

dat a. Dat a can be serially shift ed out t oggling t he Read Enable pin wit h Chip Enable low, Writ e Enable High, Address

Lat ch Enable low, and Command Lat ch Enable low. See figures 8,10,11 and t able 12 for det ails of t he t imings require-

ment s.

2.5 Wr i t e Pr ot ect .

Hardware Writ e Prot ect ion is act ivat ed when t he Writ e Prot ect pin is low. I n t his condit ion modify operat ion do not

st art and t he cont ent of t he memory is not alt ered. Writ e Prot ect pin is not lat ched by Writ e Enable t o ensure t he pro-

t ect ion even during t he power up.

2.6 St andby.

I n St andby mode t he device is deselect ed, out puts are disabled and Power Consumpt ion is reduced.

Rev. 0.7 / Dec. 2006 13

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

3. DEVI CE OPERATI ON

3.1 Page Read.

Page read operat ion is init iat ed by writ ing 00h and 30h t o t he command regist er along wit h five address cycles. I n t wo

consecut ive read operat ions, t he second one doesnt need 00h command, which five address cycles and 30h com-

mand init iat es t hat operat ion. Two types of operat ions are available : random read, serial page read. The random read

mode is enabled when t he page address is changed. The 2112 byt es (X8 device) of dat a wit hin t he select ed page are

t ransferred t o t he dat a regist ers in less t han 25us(t R). The syst em cont roller may det ect t he complet ion of t his dat a

t ransfer ( t R) by analyzing t he out put of R/ B pin. Once t he dat a in a page is loaded int o t he dat a regist ers, t hey may be

read out in 30ns cycle t ime by sequent ially pulsing RE. The repet it ive high t o low t ransit ions of t he RE clock make t he

device out put t he dat a st art ing from t he select ed column address up t o t he last column address.

The device may out put random dat a in a page inst ead of t he consecut ive sequent ial dat a by writ ing random dat a out -

put command.

The column address of next dat a, which is going t o be out , may be changed t o t he address which follows random dat a

out put command.

Random dat a out put can be operat ed mult iple t imes regardless of how many t imes it is done in a page.

3.2 Page Pr ogr am.

The device is programmed basically by page, but it does allow mult iple part ial page programming of a word or consec-

ut ive byt es up t o 2112 (X8 device) , in a single page program cycle. The number of consecut ive part ial page program-

ming operat ion wit hin t he same page wit hout an int ervening erase operat ion must not exceed 4 t imes for main array

(X8 device: 1t ime/ 512byt e) and 4 t imes for spare array (X8 device: 1t ime/ 16byt e).

The addr essi ng shoul d be done i n sequent i al or der i n a bl ock

1

. A page program cycle consist s of a serial dat a

loading period in which up t o 2112byt es (X8 device) of dat a may be loaded int o t he dat a regist er, followed by a non-

volat ile programming period where t he loaded dat a is programmed int o t he appropriat e cell.

The serial dat a loading period begins by input t ing t he Serial Dat a I nput command (80h), followed by t he five cycle

address input s and t hen serial dat a. The words ot her t han t hose t o be programmed do not need t o be loaded. The

device support s random dat a input in a page. The column address of next dat a, which will be ent ered, may be

changed t o t he address which follows random dat a input command (85h). Random dat a input may be operat ed mult i-

ple t imes regardless of how many t imes it is done in a page.

The Page Program confirm command (10h) init iat es t he programming process. Writ ing 10h alone wit hout previously

ent ering t he serial dat a will not init iat e t he programming process. The int ernal writ e st at e cont roller aut omat ically exe-

cut es t he algorit hms and t imings necessary for program and verify, t hereby freeing t he syst em cont roller for ot her

t asks. Once t he program process st art s, t he Read St at us Regist er command may be ent ered t o read t he st at us regist er.

The syst em cont roller can det ect t he complet ion of a program cycle by monit oring t he R/ B out put , or t he St at us bit (I /

O 6) of t he St at us Regist er. Only t he Read St at us command and Reset command are valid while programming is in

progress. When t he Page Program is complet e, t he Writ e St at us Bit (I / O 0) may be checked. The int ernal writ e verify

det ect s only errors for "1"s t hat are not successfully programmed t o "0"s. The command regist er remains in Read St a-

t us command mode unt il anot her valid command is writ t en t o t he command regist er. Figure 14 det ails t he sequence.

Rev. 0.7 / Dec. 2006 14

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

3.3 Bl ock Er ase.

The Erase operat ion is done on a block basis. Block address loading is accomplished in t hree cycles init iat ed by an

Erase Set up command (60h). Only address A18 t o A29 (X8) is valid while A12 t o A17 (X8) is ignored. The Erase Con-

firm command (D0h) following t he block address loading init iat es t he int ernal erasing process. This t wo-st ep sequence

of set up followed by execut ion command ensures t hat memory cont ent s are not accident ally erased due t o ext ernal

noise condit ions. At t he rising edge of WE aft er t he erase confirm command input , t he int ernal writ e cont roller handles

erase and erase-verify. Once t he erase process st art s, t he Read St at us Regist er command may be ent ered t o read t he

st at us regist er. The syst em cont roller can det ect t he complet ion of an erase by monit oring t he R/ B out put , or t he St at us

bit (I / O 6) of t he St at us Regist er. Only t he Read St at us command and Reset command are valid while erasing is in

progress. When t he erase operat ion is complet ed, t he Writ e St at us Bit (I / O 0) may be checked.

Figure 19 det ails t he sequence.

3.4 Copy-Back Pr ogr am.

The copy-back program is configured t o quickly and efficient ly rewrit e dat a st ored in one page wit hout ut ilizing an

ext ernal memory. Since t he t ime-consuming cycles of serial access and re-loading cycles are removed, t he syst em per-

formance is improved. The benefit is especially obvious when a port ion of a block is updat ed and t he rest of t he block

also need t o be copied t o t he newly assigned free block. The operat ion for performing a copy-back program is a

sequent ial execut ion of page-read wit hout serial access and copying-program wit h t he address of dest inat ion page. A

read operat ion wit h "35h" command and t he address of t he source page moves t he whole 2112byt e (X8 device) dat a

int o t he int ernal dat a buffer. As soon as t he device ret urns t o Ready st at e, Copy Back command (85h) wit h t he address

cycles of dest inat ion page may be writ t en. The Program Confirm command (10h) is required t o act ually begin t he pro-

gramming operat ion. Dat a input cycle for modifying a port ion or mult iple dist ant port ions of t he source page is allowed

as shown in Figure 16.

" When t here i s a program-f ai l ure at Copy-Back operat i on, er r or i s r epor t ed by pass/ f ai l st at us. But , i f

Copy-Back oper at i ons ar e accumul at ed over t i me, bi t er r or due t o char ge l oss i s not checked by ext er nal

er r or det ect i on/ cor r ect i on scheme. For t hi s r eason, t wo bi t er r or cor r ect i on i s r ecommended f or t he use

of Copy- Back operat i on."

Figure 16 shows t he command sequence for t he copy-back operat ion.

The Copy Back Pr ogr am oper at i on r equi r es t hr ee st eps:

1. The source page must be read using t he Read A command (one bus writ e cycle t o set up t he command and t hen

5 bus writ e cycles t o input t he source page address). This operat ion copies all 2KByt es from t he page int o t he Page

Buffer.

2. When t he device ret urns t o t he ready st at e (Ready/ Busy High), t he second bus writ e cycle of t he command is given

wit h t he 5bus cycles t o input t he t arget page address. A29 must be t he same for t he Source and Target Pages.

3. Then t he confirm command is issued t o st art t he P/ E/ R Cont roller.

Not e:

1. Copy-Back Program operat ion is allowed only wit hin t he same memory plane.

2. On t he same plane, I t s prohibit ed t o operat e copy-back program from an odd address page (source page) t o an

even address page (t arget page) or from an even address page (source page) t o an odd address page (t arget page).

Therefore, t he copy-back program is permit t ed j ust bet ween odd address pages or even address pages.

Rev. 0.7 / Dec. 2006 15

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

3.5 Read St at us Regi st er .

The device cont ains a St at us Regist er which may be read t o find out whet her read, program or erase operat ion is com-

plet ed, and whet her t he program or erase operat ion is complet ed successfully. Aft er writ ing 70h command t o t he com-

mand regist er, a read cycle out put s t he cont ent of t he St at us Regist er t o t he I / O pins on t he falling edge of CE or RE,

whichever occurs last . This t wo line cont rol allows t he syst em t o poll t he progress of each device in mult iple memory

connect ions even when R/ B pins are common-wired. RE or CE does not need t o be t oggled for updat ed st at us. Refer

t o t able 13 for specific St at us Regist er definit ions. The command regist er remains in St at us Read mode unt il furt her

commands are issued t o it . Therefore, if t he st at us regist er is read during a random read cycle, t he read command

(00h) should be given before st art ing read cycles. See figure 10 for det ails of t he Read St at us operat ion.

3.6 Read I D.

The device cont ains a product ident ificat ion mode, init iat ed by writ ing 90h t o t he command regist er, followed by an

address input of 00h. Four read cycles sequent ially out put t he manufact urer code (ADh), and t he device code and 3rd

cycle I D, 4t h cycle I D, respect ively. The command regist er remains in Read I D mode unt il furt her commands are

issued t o it . Figure 20 shows t he operat ion sequence, while t ables 15 explain t he byt e meaning.

3.7 Reset .

The device offers a reset feat ure, execut ed by writ ing FFh t o t he command regist er. When t he device is in Busy st at e

during random read, program or erase mode, t he reset operat ion will abort t hese operat ions. The cont ent s of memory

cells being alt ered are no longer valid, as t he dat a will be part ially programmed or erased. The command regist er is

cleared t o wait for t he next command, and t he St at us Regist er is cleared t o value E0h when WP is high. Refer t o t able

13 for device st at us aft er reset operat ion. I f t he device is already in reset st at e a new reset command will not be

accept ed by t he command regist er. The R/ B pin t ransit ions t o low for t RST aft er t he Reset command is writ t en. Refer

t o figure 25.

Rev. 0.7 / Dec. 2006 16

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

3.8 Cache Pr ogr am.

Cache Program is an ext ension of Page Program, which is execut ed wit h 2112byt e (X8 device) dat a regist ers, and is

available only wit hin a block. Since t he device has 1 page of cache memory, serial dat a input may be execut ed while

dat a st ored in dat a regist er are programmed int o memory cell. Aft er writ ing t he first set of dat a up t o 2112byt e (X8

device) int o t he select ed cache regist ers, Cache Program command (15h) inst ead of act ual Page Program (10h) is

input t o make cache regist ers free and t o st art int ernal program operat ion. To t ransfer dat a from cache regist ers t o

dat a regist ers, t he device remains in Busy st at e for a short period of t ime (t CBSY) and has it s cache regist ers ready for

t he next dat a-input while t he int ernal programming get s st art ed wit h t he dat a loaded int o dat a regist ers. Read St at us

command (70h) may be issued t o find out when cache regist ers become ready by polling t he Cache-Busy st at us bit (I /

O 6). Pass/ fail st at us of only t he previous page is available upon t he ret urn t o Ready st at e. When t he next set of dat a

is input wit h t he Cache Program command, t CBSY is affect ed by t he progress of pending int ernal programming. The

programming of t he cache regist ers is init iat ed only when t he pending program cycle is finished and t he dat a regist ers

are available for t he t ransfer of dat a from cache regist ers. The st at us bit (I / O5) for int ernal Ready/ Busy may be polled

t o ident ify t he complet ion of int ernal programming.

I f t he syst em monit ors t he progress of programming only wit h R/ B, t he last page of t he t arget programming sequence

must be programmed wit h act ual Page Program command (10h). I f t he Cache Program command (15h) is used

inst ead, st at us bit (I / O5) must be polled t o find out when t he last programming is act ually finished before st art ing

ot her operat ions such as read. Pass/ fail st at us is available in t wo st eps. I / O 1 ret urns wit h t he st at us of t he previous

page upon Ready or I / O6 st at us bit changing t o "1", and lat er I / O 0 wit h t he stat us of current page upon t rue Ready

(ret urning from int ernal programming) or I / O 5 st at us bit changing t o "1". I / O 1 may be read t oget her when I / O 0 is

checked. See figure 17 for more det ails.

NOTE : Since programming t he last page does not employ caching, t he program t ime has t o be t hat of Page Program.

However, if t he previous program cycle wit h t he cache dat a has not finished, t he act ual program cycle of t he

last page is init iat ed only aft er complet ion of t he previous cycle, which can be expressed as t he following

formula.

t PROG= Program t ime for t he last page+ Program t ime for t he ( last -1 )t h page

- (Program command cycle t ime + Last page dat a loading t ime)

The value for A29 from second t o t he last page address must be same as t he value given t o A29 in first address.

Rev. 0.7 / Dec. 2006 17

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

3.9 Cache Read

Cache read operat ion allows aut omat ic download of consecut ive pages, up t o t he whole device. I mmediat ely aft er 1st

lat ency end, while user can st art reading out dat a, device int ernally st art s reading following page.

St art address of 1st page is at page st art (A< 10: 0> = 00h), aft er 1st lat ency t ime (t r) , aut omat ic dat a download will

be unint errupt ed. I n fact lat ency t ime is 25us, while download of a page require at least 100us for x8 device.

Cache read operat ion command is like st andard read, except for confirm code (30h for st andard read, 31h for cache

read) user can check operat ion st at us using :

- R/ B ( 0 means lat ency ongoing, download not possible, 1 means download of n page possible, even if device

int ernally is act ive on n+ 1 page

- St at us regist er (SR< 6> behave like R/ B, SR< 5> is 0 when device is int ernally reading and 1 when device is idle)

To exit cache read operat ion a cache read exit command (34h) must be issued. t his command can be given any t ime

(bot h device idle and reading) .

I f device is act ive (SR< 5> = 0) it will go idle wit hin 5us, while if it is not act ive, device it self will go busy for a t ime

short er t hen t RBSY before becoming again idle and ready t o accept any furt her commands.

I f user arrives reading last byt e/ word of t he memory array, t hen has t o st op by giving a cache read exit command.

Random dat a out put is not available in cache read.

Cache read operat ion must be done only block by block if syst em needs t o avoid reading also from invalid blocks.

Rev. 0.7 / Dec. 2006 18

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

4. OTHER FEATURES

4.1 Dat a Pr ot ect i on & Power on/ of f Sequence

The device is designed t o offer prot ect ion from any involunt ary program/ erase during power-t ransit ions. An int ernal

volt age det ect or disables all funct ions whenever Vcc is below about 2V(3.3V device). WP pin provides hardware pro-

t ect ion and is recommended t o be kept at VI L during power-up and power-down. A recovery t ime of minimum 10us is

required before int ernal circuit get s ready for any command sequences as shown in Figure 26. The t wo-st ep command

sequence for program/ erase provides addit ional soft ware prot ect ion.

I f t he power is dropped during t he ready read/ writ e/ erase operat ion, Power prot ect ion funct ion may not guarant eed

t he dat a. Power prot ect ion funct ion is only available during t he power on/ off sequence.

4.2 Ready/ Busy.

The device has a Ready/ Busy out put t hat provides met hod of indicat ing t he complet ion of a page program, erase,

copy-back, cache program and random read complet ion. The R/ B pin is normally high and goes t o low when t he device

is busy (aft er a reset , read, program, erase operat ion). I t ret urns t o high when t he int ernal cont roller has finished t he

operat ion. The pin is an open-drain driver t hereby allowing t wo or more R/ B out put s t o be Or-t ied. Because pull-up

resist or value is relat ed t o t r(R/ B) and current drain during busy (I busy), an appropriat e value can be obt ained wit h

t he following reference chart ( Fig 27) . I t s value can be det ermined by t he following guidance.

Rev. 0.7 / Dec. 2006 19

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Par amet er Symbol Mi n Typ Max Uni t

Valid Block Number NVB 4016 4096 Blocks

Tabl e 6: Val i d Bl ocks Number

NOTE:

1. The 1st block is guarant eed t o be a valid block up t o 1K cycles wit h ECC. (1bit / 512byt es)

Symbol Par amet er

Val ue

Uni t

3.3V

TA

Ambient Operat ing Temperat ure (Commercial Temperat ure Range) 0 t o 70

Ambient Operat ing Temperat ure (Ext ended Temperat ure Range) -25 t o 85

Ambient Operat ing Temperat ure (I ndust ry Temperat ure Range) -40 t o 85

TBI AS Temperat ure Under Bias -50 t o 125

TSTG St orage Temperat ure -65 t o 150

VI O

(2)

I nput or Out put Volt age -0.6 t o 4.6 V

Vcc Supply Volt age -0.6 t o 4.6 V

Tabl e 7: Absol ut e maxi mum r at i ngs

NOTE:

1. Except for t he rat ing Operat ing Temperat ure Range, st resses above t hose list ed in t he Table Absolut e

Maximum Rat ings may cause permanent damage t o t he device. These are st ress rat ings only and operat ion of

t he device at t hese or any ot her condit ions above t hose indicat ed in t he Operat ing sect ions of t his specificat ion is

not implied. Exposure t o Absolut e Maximum Rat ing condit ions for ext ended periods may affect device reliability.

2. Minimum Volt age may undershoot t o -2V during t ransit ion and for less t han 20ns during t ransit ions.

Rev. 0.7 / Dec. 2006 20

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

ADDRESS

REG!STERf

COUNTER

PROGRAN

ERASE

CONTROLLER

Hv GENERAT!ON

CONNAND

!NTERFACE

LOG!C

CONNAND

REG!STER

DATA

REG!STER

!O

RE

BUFFERS

Y DECODER

PAGE BUFFER

X

D

E

C

O

D

E

R

4096 Mbit + 12SMbit

NAND Flash

MEMORY ARRAY

WP

CE

WE

CLE

ALE

A29 ~ A0

Fi gur e 4: Bl ock Di agr am

Rev. 0.7 / Dec. 2006 21

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Paramet er Symbol Test Condi t i ons

3.3Vol t

Uni t

Mi n Typ Max

Operat ing

Current

Sequent ial

Read

I CC1

t RC= 30ns

CE= VI L, I OUT= 0mA

- 15 30 mA

Program I CC2 - - 15 30 mA

Erase I CC3 - - 15 30 mA

St and-by Current ( TTL) I CC4

CE= VI H,

WP= 0V/ Vcc

- 1 mA

St and-by Current (CMOS) I CC5

CE= Vcc-0.2,

WP= 0V/ Vcc

- 10 50 uA

I nput Leakage Current I LI VI N= 0 t o Vcc (max) - - 10 uA

Out put Leakage Current I LO VOUT = 0 t o Vcc (max) - - 10 uA

I nput High Volt age VI H - Vccx0.8 - Vcc+ 0.3 V

I nput Low Volt age VI L - -0.3 - Vccx0.2 V

Out put High Volt age Level VOH I OH= -400uA 2.4 - - V

Out put Low Volt age Level VOL I OL= 2.1mA - - 0.4 V

Out put Low Current (R/ B)

I OL

(R/ B)

VOL= 0.4V 8 10 - mA

Tabl e 8: DC and Oper at i ng Char act er i st i cs

Par amet er

Val ue

3.3Vol t

I nput Pulse Levels 0V t o Vcc

I nput Rise and Fall Times 5ns

I nput and Out put Timing Levels Vcc/ 2

Out put Load (2.7V - 3.3V) 1 TTL GATE and CL= 50pF

Out put Load (3.0 - 3.6V) 1 TTLGATE and CL= 100pF

Tabl e 9: AC Condi t i ons

Rev. 0.7 / Dec. 2006 22

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

I t em Symbol Test Condi t i on Mi n Max Uni t

I nput / Out put Capacit ance CI / O VI L= 0V - 10 pF

I nput Capacit ance CI N VI N= 0V - 10 pF

Tabl e 10: Pi n Capaci t ance ( TA= 25C, F= 1.0MHz)

Par amet er Symbol Mi n Typ Max Uni t

Program Time t PROG - 200 700 us

Dummy Busy Time for Cache Program t CBSY - 3 700 us

Dummy Busy Time for Cache Read t RBSY - 5 - us

Number of part ial Program Cycles in t he same page

Main Array NOP - - 4 Cycles

Spare Array NOP - - 4 Cycles

Block Erase Time t BERS - 2 3 ms

Tabl e 11: Pr ogr am / Er ase Char act er i st i cs

Rev. 0.7 / Dec. 2006 23

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Par amet er Symbol

3.3Vol t

Uni t

Mi n Max

CLE Set up t ime t CLS 15 ns

CLE Hold t ime t CLH 5 ns

CE set up t ime t CS 25 ns

CE hold t ime t CH 5 ns

WE pulse widt h t WP 15 ns

ALE set up t ime t ALS 15 ns

ALE hold t ime t ALH 5 ns

Dat a set up t ime t DS 15 ns

Dat a hold t ime t DH 5 ns

Writ e Cycle t ime t WC 30 ns

WE High hold t ime t WH 10 ns

Address t o Dat a Loading Time t ADL

(2)

100 ns

Dat a Transfer from Cell t o regist er t R 25 us

ALE t o RE Delay t AR 15 ns

CLE t o RE Delay t CLR 15 ns

Ready t o RE Low t RR 20 ns

RE Pulse Widt h t RP 15 ns

WE High t o Busy t WB 100 ns

Read Cycle Time t RC 30 ns

RE Access Time t REA 25 ns

RE High t o Out put High Z t RHZ 50 ns

CE High t o Out put High Z t CHZ 50 ns

Cache read RE High t CRRH 100 ns

RE High t o Out put Hold t RHOH 15 ns

RE Low t o Out put Hold t RLOH 5 ns

CE High t o Out put Hold t COH 15 ns

RE High Hold Time t REH 10 ns

Out put High Z t o RE low t I R 0 ns

CE Access Time t CEA 30 ns

WE High t o RE low t WHR 60 ns

Device Reset t ing Time

(Read / Program / Copy-Back Program / Erase)

t RST 5/ 10/ 40/ 500

( 1)

us

Writ e Prot ect ion t ime t WW

(3)

100 ns

Tabl e 12: AC Ti mi ng Char act er i st i cs

NOTE:

1. I f Reset Command (FFh) is writ t en at Ready st at e, t he device goes int o Busy for maximum 5us

2. t ADL is t he t ime from t he WE rising edge of final address cycle t o t he WE rising edge of first dat a cycle.

3. Program / Erase Enable Operat ion : WP high t o WE High.

Program / Erase Disable Operat ion : WP Low t o WE High.

Rev. 0.7 / Dec. 2006 24

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

I O

Page

Pr ogr am

Bl ock

Er ase

Cache

Pr ogr am

Read

Cache

Read

CODI NG

0 Pass / Fail Pass / Fail Pass / Fail (N) NA Pass: 0 Fail: 1

1 NA NA Pass / Fail (N-1) NA

Pass: 0 Fail: 1

(Only for Cache Program,

else Dont care)

2 NA NA NA NA -

3 NA NA NA NA -

4 NA NA NA NA -

5 Ready/ Busy Ready/ Busy

P/ E/ R

Cont roller Bit

Ready/ Busy

P/ E/ R

Cont roller Bit

Act ive: 0 I dle: 1

6 Ready/ Busy Ready/ Busy

Cache Regist er

Free

Ready/ Busy Ready/ Busy Busy: 0 Ready: 1

7 Writ e Prot ect Writ e Prot ect Writ e Prot ect Writ e Prot ect

Prot ect ed: 0

Not Prot ect ed: 1

Tabl e 13: St at us Regi st er Codi ng

DEVI CE I DENTI FI ER CYCLE DESCRI PTI ON

1st Manufact urer Code

2nd Device I dent ifier

3rd

I nt ernal chip number, cell Type, Number of Simult aneously Programmed

pages.

4t h Page Size, Block Size, Spare Size, Organizat ion

Tabl e 14: Devi ce I dent i f i er Codi ng

Par t Number Vol t age Bus Wi dt h

1st cycl e

( Manuf act ur e Code)

2nd cycl e

( Devi ce Code)

3r d Cycl e 4t h Cycl e

HY27UF084G2M 3.3V x8 ADh DCh 80h 95h

Tabl e 15: Read I D Dat a Tabl e

Rev. 0.7 / Dec. 2006 25

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Descri pt i on I O7 I O6 I O5 I O4 I O3 I O2 I O1 I O0

I nt ernal Chip Number

1

2

4

8

0 0

0 1

1 0

1 1

Cell Type

2 Level Cell

4 Level Cell

8 Level Cell

16 Level Cell

0 0

0 1

1 0

1 1

Number of

Simult aneously

Programmed Pages

1

2

4

8

0 0

0 1

1 0

1 1

I nt erleave Program

Belween mult iple chips

Not Support

Support

0

1

Cache Program

Not Support

Support

0

1

Tabl e 16: 3r d Byt e of Devi ce I dent i f i er Descr i pt i on

Descr i pt i on I O7 I O6 I O5-4 I O3 I O2 I O1-0

Page Size

(Wit hout Spare Area)

1K

2K

Reserved

Reserved

0 0

0 1

1 0

1 1

Spare Area Size

(Byt e / 512Byt e)

8

16

0

1

Serial Access Time

50ns/ 30ns

25ns

Reserved

Reserved

0

1

0

1

0

0

1

1

Block Size

(Wit hout Spare Area)

64K

128K

256K

Reserved

0 0

0 1

1 0

1 1

Organizat ion

X8

X16

0

1

Tabl e 17: 4t h Byt e of Devi ce I dent i f i er Descr i pt i on

Rev. 0.7 / Dec. 2006 26

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Fi gur e 5: Command Lat ch Cycl e

tCLS

tCS

tWP

Command

CLE

CE

WE

ALE

!fO x

tDH tDS

tALS tALH

tCLH

tCH

Rev. 0.7 / Dec. 2006 27

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

tCLS

tCS

tWP

tWC tWC tWC

tWP tWP tWP

tALS

tWH tWH tWH tWH

tALH tALS tALS tALS tALS

Col. Add1

tALH tALH tALH

tALH

tDH

Col. Add2 Row Add1 Row Add2 Row Add3

tWC

tDH tDH tDH tDH

tDS tDS tDS tDS tDS

CLE

CE

WE

ALE

IJOx

Fi gur e 6: Addr ess Lat ch Cycl e

Fi gur e 7. I nput Dat a Lat ch Cycl e

lwC

lAL3

lCLl

lCl

lwP

lwl

0lN 0 0lN 1 0lN l|ra|

l0l l0l l0l

l03 l03 l03

lwP lwP

CLE

ALE

CE

I/Ox

WE

Notes: DN final means 2,112

Rev. 0.7 / Dec. 2006 28

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Fi gur e 8: Sequent i al Out Cycl e af t er Read ( CLE= L, WE= H, ALE= L)

tRC

CE

RE

!fOx

RfB

tREA

tRR

Dout Dout Dout

Notes: Transition is measured +f-200mv from steady state voltage with load.

This parameter is sampled and not 100 tested. (tCHZ, tRHZ)

tRLOH is valid when frequency is higher than 33NHz.

tRHOH starts to be valid when frequency is lower than 33NHz.

tREA

tRHZ tRHZ

tREA

tCHZ

tCOH

tRHOH

tREH

tRC

tRP tREH

tREA

tCEA

tRLOH

tRR

tREA

tCHZ

tCOH

tRHZ

tRHOH

Dout Dout

CE

RE

!fOx

RfB

Notes: Transition is measured +f-200mv from steady state voltage with load.

This parameter is sampled and not 100 tested. (tCHZ, tRHZ)

tRLOH is valid when frequency is higher than 33NHz.

tRHOH starts to be valid when frequency is lower than 33NHz.

Fi gur e 9: Sequent i al Out Cycl e af t er Read ( EDO Type CLE= L, WE= H, ALE= L)

Rev. 0.7 / Dec. 2006 29

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Fi gur e 10: St at us Read Cycl e

lCL3

lCLR

lCLl

lC3

lCl

lwP

lwlR

lCEA

l03

lREA

lClZ

lC0l

lRlZ

lRl0l

Z0| or Z8| 3lalus 0ulpul

l0l

llR

CE

WE

I/Ox

CLE

RE

CLE

ALE

CE

I/Ox

WE

RE

R/B

lwC

lCLR

lRR

00h 30h Col.Add1

Column Address Row Address

Col.Add2 Row Add1 Row Add2

8usy

0oul N 0oul N1 0oul V

lw8

lAR

lR lRC

lRlZ

Row Add3

Fi gur e 11: Read1 Oper at i on ( Read One Page)

Rev. 0.7 / Dec. 2006 30

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

tWB

tAR

tCHZ

tCOH

tRC

tR

tRR

Busy

00h 30h

Dout

N

Dout

N+1

Dout

N+2

Col.

Add1

Col.

Add2

Row

Add1

Row

Add2

Row

Add3

Column Address Row Address

CLE

CE

WE

ALE

RE

!fOx

RfB

Fi gur e 12: Read1 Oper at i on i nt er cept ed by CE

Rev. 0.7 / Dec. 2006 31

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

C

L

E

A

L

E

C

E

R

E

R

/

B

I

/

O

x

W

E

t

C

L

R

0

0

h

C

o

l

u

m

n

A

d

d

r

e

s

s

R

o

w

A

d

d

r

e

s

s

B

u

s

y

3

0

h

0

S

h

E

0

h

D

o

u

t

N

D

o

u

t

N

D

o

u

t

N

+

1

D

o

u

t

N

+

1

C

o

l

.

A

d

d

1

R

o

w

A

d

d

1

R

o

w

A

d

d

2

R

o

w

A

d

d

3

C

o

l

.

A

d

d

2

C

o

l

u

m

n

A

d

d

r

e

s

s

C

o

l

.

A

d

d

1

C

o

l

.

A

d

d

2

t

R

t

R

C

t

W

B

t

A

R

t

R

R

t

W

H

R

t

R

E

A

t

R

H

W

Fi gur e 13 : Random Dat a out put

Rev. 0.7 / Dec. 2006 32

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Fi gur e 14: Page Pr ogr am Oper at i on

CLE

ALE

CE

RE

RJB

IJOx

WE

lwC

80|

Co|.

Add1

Serial Data

nput Command

Column Address Row Address

Read Status

Command

Program

Command

/Oo=0 Successful Program

/Oo=1 Error in Program

1 up to m Byte

Serial nput

Co|.

Add2

RoW

Add1

RoW

Add2

RoW

Add3

0|r

N

0|r

V

10| Z0| l/0o

lwC

lw8 lPR00

lwC

lA0L

Rev. 0.7 / Dec. 2006 33

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

C

L

E

A

L

E

C

E

R

E

R

/

B

I

/

O

x

W

E

t

W

C

8

0

h

D

i

n

N

D

i

n

N

D

i

n

J

D

i

n

K

8

S

h

1

0

h

7

0

h

!

f

O

0

C

o

l.

A

d

d

1

C

o

l.

A

d

d

2

C

o

l.

A

d

d

1

C

o

l.

A

d

d

2

R

w

o

A

d

d

1

R

w

o

A

d

d

2

R

w

o

A

d

d

3

t

W

C

t

W

B

t

P

R

O

G

S

e

r

i

a

l

D

a

t

a

!

n

p

u

t

C

o

m

m

a

n

d

R

a

n

d

o

m

D

a

t

a

!

n

p

u

t

C

o

m

m

a

n

d

C

o

l

u

m

n

A

d

d

r

e

s

s

C

o

l

u

m

n

A

d

d

r

e

s

s

R

o

w

A

d

d

r

e

s

s

S

e

r

i

a

l

!

n

p

u

t

S

e

r

i

a

l

!

n

p

u

t

P

r

o

g

r

a

m

C

o

m

m

a

n

d

R

e

a

d

S

t

a

t

u

s

C

o

m

m

a

n

d

t

W

C

t

A

D

L

t

A

D

L

Fi gur e 15 : Random Dat a I n

Rev. 0.7 / Dec. 2006 34

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

B

u

s

y

t

W

B

t

W

B

t

A

D

L

t

P

R

O

G

t

W

C

C

L

E

C

E

W

E

R

E

!

f

O

x

R

f

B

A

L

E

C

o

l

u

m

n

A

d

d

r

e

s

s

0

0

h

3

S

h

8

S

h

D

a

t

a

1

D

a

t

a

N

1

0

h

!

f

O

x

7

B

h

f

7

0

h

C

o

l

.

A

d

d

1

C

o

l

.

A

d

d

2

R

o

w

A

d

d

1

R

o

w

A

d

d

2

R

o

w

A

d

d

3

C

o

l

.

A

d

d

1

C

o

l

.

A

d

d

2

R

o

w

A

d

d

1

R

o

w

A

d

d

2

R

o

w

A

d

d

3

R

o

w

A

d

d

r

e

s

s

C

o

l

u

m

n

A

d

d

r

e

s

s

R

o

w

A

d

d

r

e

s

s

t

R

B

u

s

y

C

o

p

y

-

B

a

c

k

D

a

t

a

!

n

p

u

t

C

o

m

m

a

n

d

Fi gur e 16 : Copy Back Pr ogr am

Rev. 0.7 / Dec. 2006 35

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

C

L

E

A

L

E

C

E

R

E

R

/

B

I

/

O

x

W

E

R

/

B

I

/

O

x

E

x

.

)

C

a

c

h

e

P

r

o

g

r

a

m

t

W

C

8

0

h

7

0

h

!

f

O

P

r

o

g

r

a

m

C

o

n

f

i

r

m

C

o

m

m

a

n

d

(

T

r

u

e

)

L

a

s

t

P

a

g

e

!

n

p

u

t

8

P

r

o

g

r

a

m

N

a

x

.

6

3

t

i

m

e

s

r

e

p

e

a

t

a

b

l

e

t

C

B

S

Y

:

m

a

x

.

7

0

0

u

s

t

C

B

S

Y

C

o

l

A

d

d

1

,

2

8

R

o

w

A

d

d

1

,

2

D

a

t

a

t

C

B

S

Y

t

C

B

S

Y

t

P

R

O

G

S

e

r

i

a

l

D

a

t

a

C

o

l

u

m

n

A

d

d

r

e

s

s

R

o

w

A

d

d

r

e

s

s

S

e

r

i

a

l

!

n

p

u

t

P

r

o

g

r

a

m

C

o

m

m

a

n

d

(

D

u

m

m

y

)

8

0

h

1

S

h

A

d

d

r

e

s

s

8

D

a

t

a

!

n

p

u

t

A

d

d

r

e

s

s

8

D

a

t

a

!

n

p

u

t

A

d

d

r

e

s

s

8

D

a

t

a

!

n

p

u

t

A

d

d

r

e

s

s

8

D

a

t

a

!

n

p

u

t

1

S

h

1

S

h

1

0

h

7

0

h

8

0

h

8

0

h

8

0

h

1

S

h

1

0

h

D

i

n

N

D

i

n

N

D

i

n

N

D

i

n

N

C

o

l

.

A

d

d

1

C

o

l

.

A

d

d

2

R

o

w

A

d

d

1

R

o

w

A

d

d

2

C

o

l

.

A

d

d

1

C

o

l

.

A

d

d

2

R

o

w

A

d

d

1

R

o

w

A

d

d

2

t

W

B

t

P

R

O

G

t

W

B

t

C

B

S

Y

Fi gur e 17 : Cache Pr ogr am

Rev. 0.7 / Dec. 2006 36

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

00h Add1 Add2 Add3 Add4 Add5 31h D0 D0 D1 D1 D2 D2 D3 D4

tCRRH

Read 1st page Read 2nd page

D2110 D2111

CLE

ALE

O

R/B

RE

WE

Fi gur e 18 : Cache Read RE hi gh

Rev. 0.7 / Dec. 2006 37

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

tWC

CLE

CE

WE

ALE

RE

IJOx

RJB

tWB tBERS

BUSY

70h !fO0 D0h

Row

Add1

Row

Add2

Row

Add3

60h

Auto Block Erase

Setup Command

Erase Command

Read Status

Command

!fO0=0 Successful Erase

!fO0=1 Error in Erase

Row Address

Fi gur e 19: Bl ock Er ase Oper at i on ( Er ase One Bl ock)

90h

CLE

CE

WE

ALE

RE

!fO x

00h

tREA

Read !D Command Address 1 cycle Naker Code Device Code

ADh

+th Cycle 3rd Cycle

DCh 9Sh 80h

tAR

Fi gur e 20: Read I D Oper at i on

Rev. 0.7 / Dec. 2006 38

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

00|

!dle !dle

Add1 Add2 Add3 Add1 Add5 31|

01 00 11 11 01 01

V V V

V

V V V

CLE

ALE

WE

RE

nternal operation

Status Register

SR < 5:6 >

Fi gur e 21: st ar t addr ess at page st ar t : af t er 1st l at ency uni nt er r upt ed dat a f l ow

00

ld|e ld|e

5s (lR83Y)

01 01 11 11

r1 pae

r pae

Read r1 pae

00 01 31| 01 02 03 01 2111

CLE

ALE

WE

RE

R/B

nternal

operation

Status Register

SR < 5:6 >

User can

here finish

reading N

page

N+2 page

cannot be

read

25s

100s

lrlerrupled

Read

r2 pae

Fi gur e 22: exi t f r om cache r ead i n 5us when devi ce i nt er nal l y i s r eadi ng

Rev. 0.7 / Dec. 2006 39

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Syst em I nt er f ace Usi ng CE dont car e

To simplify syst em int erface, CE may be deassert ed during dat a loading or sequent ial dat a-reading as shown below.

So, it is possible t o connect NAND Flash t o a microporcessor. The only funct ion t hat was removed from st andard NAND

Flash t o make CE dont care read operat ion was disabling of t he aut omat ic sequent ial read funct ion.

CE don't-care

80h Start Add.(SCycle) Data !nput 10h Data !nput

CLE

CE

WE

ALE

IJOx

Fi gur e 23: Pr ogr am Oper at i on wi t h CE dont -car e.

!f sequential row read enabled,

CE must be held low during tR. CE don't-care

00h 30h

CLE

CE

RE

ALE

RfB

WE

!fOx Start Add.(SCycle) Data Output(sequential)

tR

Fi gur e 24: Read Oper at i on wi t h CE dont - car e.

Rev. 0.7 / Dec. 2006 40

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Fi gur e 25: Reset Oper at i on

FFh

t

RST

WE

ALE

CLE

RE

IOx

RJB

WP

WE

Vcc

20us

t

VTH

Fi gur e 26: Power On and Dat a Pr ot ect i on Ti mi ng

VTH = 2.5 Vol t f or 3.3 Vol t Suppl y devi ces

Rev. 0.7 / Dec. 2006 41

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Rp value guidence

Rp(min, 3.3v part) = =

where !L is the sum of the input currnts of all devices tied to the RfB pin.

Rp(max) is determined by maximum permissible limit of tr

@ Vcc = 3.3V, Ta = 25C, CL=100pF

vcc (Nax.) - vOL (Nax.) 3.2v

8mA + !L !OL + !L

Rp

ibusy

CL

Rp (ohm)

ibusy

i

b

u

s

y

[

A

|

t

r

,

t

f

[

s

|

tf

2.+ 200

1S0

1.2

S0

100

0.8

0.6

1.8 1.8 1.8 1.8

Busy

Ready vcc

vOH

tr tf

vOL

vcc

1S0n 3m

1k 2k 3k +k

100n 2m

S0n 1m

GND

Device

open drain output

R/B

Fi gur e 27: Ready/ Busy Pi n el ect r i cal speci f i cat i ons

Rev. 0.7 / Dec. 2006 42

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Fi gur e 28 : page pr ogr ammi ng wi t hi n a bl ock

From lhe LSB paqe lo MSB paqe

DATA N Dala !) Dala 64)

Dala ressler

Paqe 63

Paqe 3!

Paqe 2

Paqe !

Paqe 0

64)

32)

3)

2)

!)

Ex.) Pandom paqe proqram Prohblon)

DATA N Dala !) Dala 64)

Dala ressler

Paqe 63

Paqe 3!

Paqe 2

Paqe !

Paqe 0

64)

!)

3)

32)

!)

Rev. 0.7 / Dec. 2006 43

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Bad Bl ock Management

Devices wit h Bad Blocks have t he same quality level and t he same AC and DC charact erist ics as devices where all t he

blocks are valid. A Bad Block does not affect t he performance of valid blocks because it is isolat ed from t he bit line and

common source line by a select t ransist or.

The devices are supplied wit h all t he locat ions inside valid blocks erased(FFh). The Bad Block I nformat ion is writ t en

prior t o shipping. Any block where t he 1st Byte in t he spare area of t he 1st or 2nd page(if t he 1st page is Bad) does

not cont ain FFh is a Bad Block. The Bad Block I nformat ion must be read before any erase is at t empt ed as t he Bad

Block I nformat ion may be erased. For t he syst em t o be able t o recognize t he Bad Blocks based on t he original informa-

t ion it is recommended t o creat e a Bad Block t able following t he flowchart shown in Figure 29. The 1st block, which is

placed on 00h block address is guarant eed t o be a valid block.

Bad Repl acement

Over t he lifet ime of t he device addit ional Bad Blocks may develop. I n t his case t he block has t o be replaced by copying

t he dat a t o a valid block. These addit ional Bad Blocks can be ident ified as at t empt s t o program or erase t hem will give

errors in t he St at us Regist er.

As t he failure of a page program operat ion does not affect t he dat a in ot her pages in t he same block, t he block can be

replaced by re-programming t he current dat a and copying t he rest of t he replaced block t o an available valid block.

The Copy Back Program command can be used t o copy t he dat a t o a valid block.

See t he Copy Back Program sect ion for more det ails.

Refer t o Table 18 for t he recommended procedure t o follow if an error occurs during an operat ion.

Operat i on Recommended Pr ocedur e

Erase Block Replacement

Program Block Replacement or ECC (wit h 1bit / 512byt e)

Read ECC (wit h 1bit / 512byt e)

Tabl e 18: Bl ock Fai l ur e

Fi gur e 29: Bad Bl ock Management Fl owchar t

Yes

Yes

No

No

START

Block Address=

Block 0

Data

=FFh?

Last

block?

END

!ncrement

Block Address

Update

Bad Block table

Rev. 0.7 / Dec. 2006 44

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Wr i t e Pr ot ect Oper at i on

The Erase and Program Operat ions are aut omat ically reset when WP goes Low (t WW = 100ns, min) . The operat ions

are enabled and disabled as follows (Figure 30~ 33)

WW

t

80h 10h

WE

/Ox

WP

R/B

80h 10h

t

WW

WE

/Ox

WP

R/B

Fi gur e 30: Enabl e Pr ogr ammi ng

Fi gur e 31: Di sabl e Pr ogr ammi ng

Rev. 0.7 / Dec. 2006 45

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

60h

t

D0h

WW

WE

/Ox

WP

R/B

60h

t

WW

D0h

WE

/Ox

WP

R/B

Fi gur e 32: Enabl e Er asi ng

Fi gur e 33: Di sabl e Er asi ng

Rev. 0.7 / Dec. 2006 46

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

5. APPENDI X : Ext r a Feat ur es

5.1 Addr essi ng f or pr ogr am oper at i on

Wit hin a block, t he pages must be programmed consecut ively from LSB ( least significant bit ) page of t he block t o MSB

(most significant bit ) page of t he block. Random address programming is prohibit ed. See Fig. 34.

Rev. 0.7 / Dec. 2006 47

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Tabl e 19: 48-TSOP1 - 48-l ead Pl ast i c Thi n Smal l Out l i ne,

12 x 20mm, Package Mechani cal Dat a

Symbol

mi l l i met er s

Mi n Typ Max

A 1.200

A1 0.050 0.150

A2 0.980 1.030

B 0.170 0.250

C 0.100 0.200

CP 0.100

D 11.910 12.000 12.120

E 19.900 20.000 20.100

E1 18.300 18.400 18.500

e 0.500

L 0.500 0.680

alpha 0 5

Fi gur e 34. 48- TSOP1 - 48-l ead Pl ast i c Thi n Smal l Out l i ne, 12 x 20mm, Package Out l i ne

25

48

24

D

A2

DE

A1

e

B

L

E1

E

C

CP

A

Rev. 0.7 / Dec. 2006 48

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

Symbol

mi l l i met er s

Mi n Typ Max

A 16.90 17.00 17.10

A1 13.00

A2 12.00

B 11.90 12.00 12.10

B1 10.00

B2 6.00

C 1.00

C1 1.50

C2 2.00

D 1.00

D1 1.00

E 0.55 0.60 0.65

CP1 0.65 0.70 0.75

CP2 0.95 1.00 1.05

Tabl e 20: 52- ULGA, 12 x 17mm, Package Mechani cal Dat a

Fi gur e 35. 52- ULGA, 12 x 17mm, Package Out l i ne

( Top vi ew t hr ough package)

B

A A1 A2

cp1

E

cp2

C2

C

C1

B1

B2

D D1

0.1 M C AB

0.1 M C AB

Rev. 0.7 / Dec. 2006 49

HY27UF084G2M Ser i es

4Gbi t ( 512Mx8bi t ) NAND Fl ash

MARKI NG I NFORMATI ON- TSOP1/ ULGA

Pack ag e Mar k i n g Ex am p l e

TSOP1

/

ULGA

K O R

H Y 2 7 U F 0 8 4 G 2 M

x x x x Y W W x x

- h y n i x

- KOR

- HY2 7 UF0 8 4 G2 M x x x x

HY: Hy n i x

2 7 : NAND Fl ash

U: Po w er Su p p l y

F: Cl assi f i cat i on

0 8 : Bi t Or g an i zat i on

4 G: Den si t y

2 : Mo d e

M: Ver si o n

x : Pack ag e Ty p e

x : Pack ag e Mat er i al

x : Op er at i n g Tem p er at u r e

x : Bad Bl o ck

- Y: Year ( ex : 5= y ear 20 0 5 , 06 = y ear 20 0 6 )

- w w : Wo r k Week ( ex : 12 = w or k w eek 12 )

- x x : Pr ocess Co d e

No t e

- Cap i t al Let t er

- Sm al l Let t er

: Hy n i x Sy m b o l

: Or i g i n Cou n t r y

: U( 2 . 7 V~ 3 . 6 V)

: Si n g l e Lev el Cel l

: 0 8 ( x 8 )

: 4 Gb i t

: 2 ( 1 n CE & 1 R/ n B; Seq u en t i al Ro w Read Di sab l e)

: 1 st Gen er at i o n

: T( 4 8- TSOP1 ) , U( 5 2 - ULGA)

: Bl an k ( Nor m al ) , P( Lead Fr ee)

: C( 0 ~ 7 0 ) , E( - 2 5~ 8 5 )

M( - 3 0~ 8 5 ) , I ( - 4 0~ 8 5 )

: B( I n cl u d ed Bad Bl ock ) , S( 1 ~ 5 Bad Bl ock ) ,

P( Al l Go od Bl o ck )

: Fi x ed I t em

: Non - f i x ed I t em

: Par t Nu m b er

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- IRF510Document8 pagesIRF510aj_oaomvNo ratings yet

- PS2251Document19 pagesPS2251ajoaomvNo ratings yet

- M33Document1 pageM33aj_oaomvNo ratings yet

- Compal La 6901p r01 SchematicsDocument60 pagesCompal La 6901p r01 Schematicsscobie_21No ratings yet

- At90Usbkey: Vt52, Vt100, AnsiDocument1 pageAt90Usbkey: Vt52, Vt100, Ansiaj_oaomvNo ratings yet

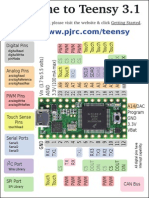

- Teensy++2.0 TopDocument1 pageTeensy++2.0 Topaj_oaomvNo ratings yet

- Teensy 3.1 BotDocument1 pageTeensy 3.1 Botaj_oaomvNo ratings yet

- Teensy 3.1 TopDocument1 pageTeensy 3.1 Topaj_oaomvNo ratings yet