Professional Documents

Culture Documents

9309 - CMOS Analog Design Chapter 8

Uploaded by

raju.kprr8862Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

9309 - CMOS Analog Design Chapter 8

Uploaded by

raju.kprr8862Copyright:

Available Formats

CMOS Analog Design Using All-Region MOSFET

Modeling

1

CMOS Analog Design Using

All-Region MOSFET Modeling

Chapter 8

Operational amplifiers

CMOS Analog Design Using All-Region MOSFET

Modeling

2

+

v

i

-

+

-

G

m

v

i

G

S

+

v

o

-

G

m

=AG

S

+

v

i

-

+

-

+

Av

i

-

R

S

+

v

o

-

A

R

S

=0

+

-

The ideal operational amplifier

CMOS Analog Design Using All-Region MOSFET

Modeling

3

2 2

1 1

2

1

1

1 1

1

1 1

o

i

v R R

v R R

R

A R

| |

= + ~ +

|

| |

\ .

+ +

|

\ .

+

v

i

-

-

+

R

2

R

1

+

v

o

-

Inverting amplifier

2 2

1 1

2

1

1

1

1 1

o

i

v R R

v R R

R

A R

= ~

| |

+ +

|

\ .

-

+

R

2

R

1

+

v

i

-

+

v

o

-

Non inverting amplifier

Applications of operational amplifiers - 1

CMOS Analog Design Using All-Region MOSFET

Modeling

4

Transimpedance amplifier

2 2 2

1

1

1

o

v A

R R R

i A A

| |

= ~ ~

|

+

\ .

-

+

R

2

i

+

v

o

-

- Continuous-time filters

- SC filters

- D/A & A/D converters

- Sensor signal conditioning

- Voltage & current references

- Comparators

- Nonlinear analog functions,

- .......

(d)

C

+

v

o

-

-

+

R

+

v

i

-

Applications of operational amplifiers - 2

CMOS Analog Design Using All-Region MOSFET

Modeling

5

C

+

v

o

-

-

+

R

+

v

i

-

R

|

1

|

2

C

2

+

v

o

-

-

+

+

v

i

-

C

1

|

1

|

2

|

2

|

1

S/H circuit

Switched-capacitor

integrator

Applications of operational amplifiers - 3

CMOS Analog Design Using All-Region MOSFET

Modeling

6

Performance parameters of op amps - 1

Table 8.1 Measured dc and ac characteristics

of the buffered op amp of reference [7].

10 mW Power dissipation

0.88 V Vout-

4.12 V Vout+

1 mV Offset voltage

18.8 V/s SR

-

(50 O|| 33 pF load)

20.4 V/s SR

+

(50 O|| 33 pF load)

11.4 MHz Gain-bandwidth product

67.2 dB DC gain (163O|| 33 pF load)

5 V Supply voltage

CMOS Analog Design Using All-Region MOSFET

Modeling

7

Performance parameters of op amps - 2

Table 8.2 Experimental performance of the operational amplifiers

of [8] (V

supply

= 1 V, Technology: 1.2-m CMOS, C = 15 pF).

56.7 dB

51.5 dB

54.4 dB

52.1 dB

PSRR

+

PSRR

-

58 dB 62 dB CMRR

359 nV/\Hz

171 nV/\Hz

82 nV/\Hz

267 nV/\Hz

91 nV/\Hz

74 nV/\Hz

v

ni

(@ 1 kHz)

v

ni

(@ 10 kHz)

v

ni

(@ 1 MHz)

-77 dB

-57 dB

-54 dB

-32 dB

THD (0.5 V

pp

@ 1 kHz)

THD (0.5 V

pp

@ 40 kHz)

0.9 V/s

1.7 V/s

0.8 V/s

1 V/s

SR

+

SR

-

73

o

61

o

Phase margin

2.1 MHz 1.9 MHz Unity-gain frequency

70.5 dB 87 dB DC gain

208 A 410 A I

DD

(supply current)

0.26 mm

2

0.81 mm

2

Active die area

Amplifier II Amplifier I Parameter

CMOS Analog Design Using All-Region MOSFET

Modeling

8

C

L

I

2

I

T

I

1

= I

3

i

0

M

4

M

3

I

4

v

O

+

v

G1

-

M

1

M

2

+

v

G2

-

+ -

1:1

V

SS

Low gain

Reduced output swing

What is the maximum output swing

when the conventional differential pair is

used for a buffer?

The differential amplifier as an op amp - 1

CMOS Analog Design Using All-Region MOSFET

Modeling

9

What is the maximum output swing

when the telescopic-cascode

differential pair is used for a buffer?

V

O

M

7

M

6

+

V

G1

-

V

DD

+

V

G2

-

M

5

I

T

M

1

M

2

V

X

M

3

M

4

M

8

V

BN

V

BP

Telescopic-cascode differential amplifier

The differential amplifier as an op amp - 2

CMOS Analog Design Using All-Region MOSFET

Modeling

10

The symmetric op amp - 1

V

SS

I

T

+

v

G1

-

M

1

M

2

I

1

I

2

+

v

G2

-

Current

Mirror

B:1

C

L

BI

1

BI

2

BI

1

I

o

= B(I

2

-I

1

)

Current

Mirror

1:B

1:1

Current

Mirror

CMOS Analog Design Using All-Region MOSFET

Modeling

11

V

O

M

1

M

2

+

V

G1

-

+

V

G2

-

M

4

1:B

I

T

V

X

M

3

M

5

V

DD

M

6

M

7

M

8

B:1

1:1

C

L

I

L

V

Y

-1

I

1

/I

T

I

2

/I

T

0 4 2 -2 -4

1

I

L

/BI

T

V

ID

(a.

u.)

The symmetric op amp - 2

CMOS Analog Design Using All-Region MOSFET

Modeling

12

Common-mode input range:

see diff. amp.

( )

T

L P

BI

SR

C C

=

+

( )

( )

1

1

m o

d

o L P

Bg R

A s

sR C C

=

+ +

( )

1

1

(Hz)

2

m

L P

Bg

GB

C C t

=

+

Current mirrors delays were

neglected

I

o

= B(I

2

-I

1

)

V

SS

I

T

+

v

G1

-

M

1

M

2

I

1

I

2

+

v

G2

-

B:1 1:B

1:1

BI

1

BI

2

BI

1

C

L

asymmetry

The symmetric op amp - 3

1 2 id g g

v v v =

C

L

+C

P

1 m id

Bg v

o

R

+

v

o

-

CMOS Analog Design Using All-Region MOSFET

Modeling

13

Telescopic differential amplifier with

high-swing cascode current mirror

Suppose that the high-swing telescopic

op amp will be used in an application

such that V

ICM

is constant and chosen

as equal to the minimum voltage such

that I

SS

remains in saturation. In this

case, what would be the maximum

output swing when V

b1

and V

b2

are

optimally biased?

V

O

M

7

M

6

+

V

G1

-

V

DD

+

V

G2

-

M

5

I

T

M

1

M

2

V

X

M

3

M

4

M

8

V

BN

V

BP

Problem:

CMOS Analog Design Using All-Region MOSFET

Modeling

14

Folded cascode amplifiers - 1

I

T

I

T

/2 I

T

/2

Ai

Ai

2Ai

M

1

M

2

M

3

M

4

M

5

M

6

M

7

M

8

M

9

M

10

M

11

+ -

I

B

I

B

Ai

Ai

Ai

V

DD

V

SS

V

bias2

+

v

o

-

C

L

v

i1

v

i2

V

bias1

N2 N1

V

bias3

Can be replaced with

high-swing current

mirror to increase

positive output swing

CMOS Analog Design Using All-Region MOSFET

Modeling

15

I

T

i

o

M

1

M

2

M

3

M

4

M

5

M

6

M

7

M

8

M

9

M

10

M

11

+ -

I

T

I

T

V

DD

V

SS

V

B3

+

v

o

-

C

L

v

i1

v

i2

V

B2

V

B1

V

B4

V

D

D

I

REF

M

16

M

12

V

SS

M

13

M

14

M

15

to

V

B

1

to

V

B2

to

V

B3

to

V

B4

M

17

M

18

Bias network

What is the maximum achievable

output swing?

The common-mode input range is

V

ICM,min

~V

SS

;

V

ICM,max

=V

DD

-V

DSsat11

-V

SG1

Folded cascode amplifiers - 2

CMOS Analog Design Using All-Region MOSFET

Modeling

16

( )

( )

1 2 01 02

1 2

1 1 2

5

5 6 05 06

1

5 6

1 5 6

9

9 10 09 010

1

9 10

1 9 10

2( / 2)

2

OS T T

S S T

m S S

m

OS T T

m

S S B T

m S S

m

OS T T

m

S S B

m S S

V V V

I I I

g I I

g

V V V

g

I I I I

g I I

g

V V V

g

I I I

g I I

= +

+

= +

+

=

+

I

T

i

o

M

1

M

2

M

3

M

4

M

5

M

6

M

7

M

8

M

9

M

10

M

11

+ -

I

T

I

T

V

DD

V

SS

V

B3

+

v

o

-

C

L

v

i1

v

i2

V

B2

V

B1

V

B4

Folded cascode amplifiers - 3

Offset voltage

CMOS Analog Design Using All-Region MOSFET

Modeling

17

0

0

1

d

d

L

A

A

sC R

~

+

Note: The output swing can be

around -V

SS

+2V

DSsatn

to V

DD

-

2V

SDsatp

for optimized bias.

R

o

T

L

I

SR

C

=

0 d m o

A G R =

& doublet

1 m m

G g =

( )

8

6

8

4

10 2

4

1

md

o ds

o ms

md

md md

ms

g

G g

R g

g

g g

g

= =

+ +

I

T

i

o

M

1

M

2

M

3

M

4

M

5

M

6

M

7

M

8

M

9

M

10

M

11

+ -

I

T

I

T

V

DD

V

SS

V

B3

+

v

o

-

C

L

v

i1

v

i2

V

B2

V

B1

V

B4

Folded cascode amplifiers - 4

CMOS Analog Design Using All-Region MOSFET

Modeling

18

1 2

(1 )

2

o d mir d

cm

icm icm

mi mi

t mir

t mi mi

i i i

G

v v

g g

y

y ng g

c

c

= = ~

| |

A

|

+

\ .

N-well of input transistors to V

DD

/ 1 2 /

/

o id mi t

mi

o icm

mir

mi

i v ng y

CMRR

g

i v

g

c

+

= ~

A

CMRR

Folded cascode amplifiers - 5

I

T

i

o

M

1

M

2

M

3

M

4

M

5

M

6

M

7

M

8

M

9

M

10

M

11

+ -

I

T

I

T

V

DD

V

SS

V

B3

+

v

o

-

C

L

v

i1

v

i2

V

B2

V

B1

V

B4

CMOS Analog Design Using All-Region MOSFET

Modeling

19

( )( ) ( )

1 9 2 10

1 2

10 9 9

1 2

1

2

d d mir d d o

vss

ss ss

ms ms ss

ss ds ds mir ds

ms ms

i i i i i

G

v v

g g g

g g g g

g g

c

c

+ +

= =

| |

~ + + +

|

+

\ .

1

1 2 10 9 9

1 2 1 1 1 1

1

2

vss

vss m

ms ms ss ds ds ss ds

mir

ms ms m m m m

G

PSRR g

g g g g g g g

g g g g g g

c

=

| |

= + + +

|

+

\ .

PSRR

vss

I

T

i

o

M

1

M

2

M

3

M

4

M

5

M

6

M

7

M

8

M

9

M

10

M

11

+ -

I

T

I

T

V

DD

V

SS

V

B3

+

v

o

-

C

L

v

i1

v

i2

V

B2

V

B1

V

B4

Folded cascode amplifiers - 6

CMOS Analog Design Using All-Region MOSFET

Modeling

20

Noise

2 2 2 2

1 5 9

2

no n n n

i i i i

f f

| |

+ +

~ |

|

A A

\ .

Input-referred noise

2 2 2 2

1 5 9

2

1

2

ni n n n

m

e i i i

f g f

| |

+ +

~ |

|

A A

\ .

Folded cascode amplifiers - 7

I

T

i

o

M

1

M

2

M

3

M

4

M

5

M

6

M

7

M

8

M

9

M

10

M

11

+ -

I

T

I

T

V

DD

V

SS

V

B3

+

v

o

-

C

L

v

i1

v

i2

V

B2

V

B1

V

B4

CMOS Analog Design Using All-Region MOSFET

Modeling

21

Output swing:

6 7 DD DSsat o SS DSsat

V V V V V > > +

For systematic offset 0.

V

DD

C

L

V

SS

M

4

M

3

M

1

M

2

M

8

M

5

M

7

M

6

I

T

v

i

+

-

C

C

v

o

1:1

1:B

1:1

1:2B

inv

non inv

1:2B

( )

6 4 7 5

/ 2 / S S S S =

0

0

2

2

SN T

OS T N

mn SN

mp

SP T

T P

mn mn SP

I I

V V

g I

g

I I

V

g g I

A

= A +

A

A +

~ same offset voltage as diff. amp.

Two-stage amplifiers - 1

Common-mode input range:

see diff. amp.

CMOS Analog Design Using All-Region MOSFET

Modeling

22

v

oI

g

oI

+

v

id

-

g

mI

+

-

C

oI

v

o

g

oII

C

L

-g

mII

Frequency

compensation

i

oI

V

DD

C

L

V

SS

M

4

M

3

M

1

M

2

M

5

M

7

M

6

I

T

v

i

+

-

C

C

v

o

1:B

1:1

1:2B

inv

non inv

Two-stage amplifiers - 2

CMOS Analog Design Using All-Region MOSFET

Modeling

23

Equivalent differential circuit

1 mI m

g g =

( )

1

2 4

2 4 6 6

I ds ds

I db db gb gs

R g g

C C C C C

= +

= + + +

6 mII m

g g =

( )

1

6 7

6 7

II ds ds

II db db L

R g g

C C C C

= +

= + +

For C

C

0

( )

( ) ( )

1 1

o mI mII I II

in I I II II

V g g R R

s

V sR C sR C

~

+ +

Poles relatively close phase margin

can be low or even negative !!!

Exercise: Derive the transfer function A

d

(s)

of the compensated operational amplifier

Two-stage amplifiers - 3

+

v

in

-

R

I

gm

I

v

in

C

I

+

v

I

-

gm

II

v

I

R

II

C

II

+

v

o

-

C

C

CMOS Analog Design Using All-Region MOSFET

Modeling

24

v

oI

g

oI

+

v

id

-

g

mI

+

-

C

oI

v

o

g

oII

C

L

-g

mII

Frequency

compensation

i

oI

Frequency

compensation

C

C

( )( )

0

/

1 / 1 /

C

o mI mII oI oII

id oI oI L oII

C

V g g g g

V sC g sC g

=

=

+ +

C

C

=0

( ) ( )

( )

( )( )

0

1 2

1

1 / 1 /

d

o

d

id

A s z

V

A s s

V s p s p

= =

0 d mI mII I II

A g g R R =

( ) ( )

1

1 1

I I C II II C mII I II c mII I II c

p

R C C R C C g R R C g R R C

~ ~

+ + + +

( )

2

mII c

I II

mII

I I I C I I

g C

p

C C C C C

g

C

~ ~

+ +

mII

c

g

z

C

=

Two-stage amplifiers - 4

C

C

=0

CMOS Analog Design Using All-Region MOSFET

Modeling

25

( ) ( )

( )

( )( )

0

1 2

1

1 / 1 /

d

o

d

in

A s z

V

A s s

V s p s p

= =

( ) ( )

1

1 1

I I C II II C mII I II c mII I II c

p

R C C R C C g R R C g R R C

~ ~

+ + + +

( )

2

mII c

I II

mII

I I I C I I

g C

p

C C C C C

g

C

~ ~

+ +

mII

c

g

z

C

=

s-plane

je

p

1

p

2

-g

oI

/C

oI

-g

oII

/C

L

z

o

Poles for C

C

=0

Poles for C

C

=0

Two-stage amplifiers - 5

Pole splitting

CMOS Analog Design Using All-Region MOSFET

Modeling

26

When you design an op amp

you must take into account

both load and feedback loop.

|A

V

|

dB

g

oI

/C

oI

0

e

u

g

oII

/C

L

(a) Uncompensated op amp

| (rad)

0

-t/2

-t

e

u

g

oII

/C

L

g

oI

/C

oI

loge

|A

V

|

dB

z

0

e

u

-p

1

-p

2

loge

(b) Compensated op amp

| (rad)

0

-t/2

-t

e

u

z

-p

2

-p

1

PM

Two-stage amplifiers - 6

CMOS Analog Design Using All-Region MOSFET

Modeling

27

( ) ( )

( )

( )( )

0

1 2

1

1 / 1 /

d

o

d

in

A s z

V

A s s

V s p s p

= =

( ) ( )

1

1 1

I I C II II C mII I II c mII I II c

p

R C C R C C g R R C g R R C

~ ~

+ + + +

( )

2

mII c

I II

mII

I I I C I I

g C

p

C C C C C

g

C

~ ~

+ +

mII

c

g

z

C

=

1 1 1 1

2

tan tan tan 1 tan

2 2

u u mI oI oI mI L

mII C C L mII

g C C g C

PM

p z g C C C g

e e t t

| |

| | | | | |

| |

= = + +

|

| | | |

|

\ .

\ . \ . \ .

\ .

1 1

tan 1 tan

2

u L oI oI u L C

mII C L mII L

C C C C C

PM

g C C g C

e e t

| |

| | | |

= + +

|

| |

|

\ . \ .

\ .

Two-stage amplifiers - 7

CMOS Analog Design Using All-Region MOSFET

Modeling

28

CMRR: same as in differential amplifier

0 0

ssII ssI

o iII oI vssII ssII

v v

i A i Y v

= =

= + ( )

0

ssI

o iII mI id mvssI ssI mvssII ssII

v

i A Y v Y v Y v

=

= + +

1 1 1

mvssII oI

vss vssI iII mI vssI mI vssII

Y Y

PSRR PSRR A Y PSRR Y PSRR

= + = +

( )

mI mI mI

oI oI C oI oI C

Y g g

Y g s C C g sC

= ~

+ + +

7

mII mII

vssII

mvssII ss ds L

Y g

PSRR

Y Bg g sC

= ~

+ +

Two-stage amplifiers - 8

CMOS Analog Design Using All-Region MOSFET

Modeling

29

Noise

v

oI

g

oI

g

mI

+

-

C

oI

v

o

g

oII

C

L

-g

mII

e

nII

e

nI

C

C

2 2 2

2

2 2

,

2

0

1

nII i

nII oI nII

mI u V I u

e

e g e

f f g f A

e e

e e

( (

| | | | | |

( ( = + = +

| | |

A A A

( (

\ . \ . \ .

Input-referred noise of the second stage

Two-stage amplifiers - 9

2

2

2 2 2 2

,

2

0

1

nII i

ni nI nI nII

V I u

e

e e e e

f f f f f A

e

e

(

| |

( = + = + +

|

A A A A A

(

\ .

Noise of 1

st

stage prevails over

that of the 2

nd

stage

except for

frequencies approaching e

u

CMOS Analog Design Using All-Region MOSFET

Modeling

30

/

T C

SR I C

+

=

M

5

V

O

M

1

M

2

+

V

G1

-

V

DD

+

V

G2

-

I

T

C

L

M

3

M

4

I

L

1:1 1:2B

C

C

M

6

M

7

inv

ninv

V

OI

I

C

BI

T

I

D6

( )

1

min ,

T

T

L C

B I

I

SR

C C

| |

=

|

\ .

Two-stage amplifiers - 10

CMOS Analog Design Using All-Region MOSFET

Modeling

31

0 0

max

; sin ;

o o

o

dv dv

SR v A t A SR

dt dt

e e s = = s

Amplitude x frequency limitation due to SR

J. Dostl, Operational Amplifiers, 2nd.

Ed., Butterworth-Heinemann, Boston,

1993.

Amplitude limitation

SR-limited slope

Two-stage amplifiers - 11

CMOS Analog Design Using All-Region MOSFET

Modeling

32

Elimination of the feed forward

effect of C

C

using a buffer

C

L

M

5

V

O

M

1

M

2

V

DD

I

T

M

3

M

4

1:1

1:2B

C

C

M

6

M

7

BI

T

I

B

M

8

V

DD

+1

Two-stage amplifiers - 12

v

oI

g

oI

+

v

id

-

g

mI

+

-

C

oI

v

o

g

oII

C

L

-g

mII

i

oI

C

C

+1

CMOS Analog Design Using All-Region MOSFET

Modeling

33

Nulling resistor

g

oII

v

oI

g

oI

+

v

id

-

g

mI

+

-

C

oI

v

o

C

L

-g

mII

i

oI

C

C

R

Z

M

5

V

O

M

1

M

2

V

DD

I

T

C

L

M

3

M

4

1:1 1:2B

C

C

M

6

M

7

BI

T

M

8

Bias

Two-stage amplifiers - 13

CMOS Analog Design Using All-Region MOSFET

Modeling

34

No general rules

Specs depend on the application:

-

+

-

+

CMIR changes (diff. amp. with

complementary input pairs can

be required)

-

+

CMIR =0

Capacitive load

-

+

RC load

Some comments on op amp design - 1

CMOS Analog Design Using All-Region MOSFET

Modeling

35

Scalable design:

-

+

C

-

+

m

mC

Switched circuits with f

sample

>>f

Nyquist

- SR is not important

but settling time is

Some comments on op amp design - 2

Improved SNR and

matching for m>1

CMOS Analog Design Using All-Region MOSFET

Modeling

36

+

v

id

-

g

mI

+

-

g

mII

v

o

C

L

-g

mIII

C

mII

C

mI

-g

mfII

g

mfI

+

-

3-stage op amp with nested Miller compensation (NMC). The nested

transconductance-capacitance compensation (NGCC) amplifier is the

NMC + two transconductors (dashed lines).

Three-stage amplifiers

CMOS Analog Design Using All-Region MOSFET

Modeling

37

I

T

M

1

M

2

M

9

M

10

M

11

+ -

V

SS

V

bias1

V

bias3

V

SDsat11

V

SG1

V

SD1

V

DS9

~V

DSsat9

Problem of the p-channel input

differential pair : V

ICM

<V

DD

Similarly, for the n-channel

input pair : V

ICM

>V

SS

How to get a rail-to-rail

differential amplifier ?

Combine p- and n-channel

input differential pairs

Rail-to-rail input stages - 1

CMOS Analog Design Using All-Region MOSFET

Modeling

38

Transconductance, noise, and offset voltage are not constant over the

input range. The current switches block is included to keep the

transconductance approximately constant over the input range.

Combining p- and n-channel input differential pairs

I

T1

i

o

M

1

M

2

M

3

M

4

M

5

M

6

M

7

M

8

M

10

V

DD

V

SS

+v

in

-v

in

V

B2

V

B1

I

T2

I

B

I

B

M

9

Current

switches

V

SS

V

DD

Rail-to-rail input

differential amplifier

Rail-to-rail input stages - 2

CMOS Analog Design Using All-Region MOSFET

Modeling

39

Class-A amplifiers: poor efficiency and high quiescent power

V

I

V

DD

V

SS

V

O

I

B

I

O

R

L

-R

L

I

B

V

O

V

DD

-V

DSsat

V

I

(a) CMOS class-A

source follower

(b) voltage transfer curve

0

1

1

O

V

I

m L

V

A

V

n

g R

= =

+

Class-AB output stages - 1

CMOS Analog Design Using All-Region MOSFET

Modeling

40

V

O

V

DD

-V

Dssat1

V

I

V

SS

+|V

Dssat2

|

(b)

V

DD

V

I

V

SS

V

O

I

O

(a)

M

1

M

2

(a) CMOS class-B source follower

(b) voltage transfer curve

Class-AB output stages - 2

CMOS Analog Design Using All-Region MOSFET

Modeling

41

(a)

V

DD

V

SS

V

O

I

O

V

I

I

B

M

1

M

2

M

4

M

3

1:N

1:N

V

O

V

DD

-V

DSsat1

V

I

V

SS

+|V

DSsat2

|

(b)

V

I0

(a) CMOS class-AB source follower

(b) voltage transfer curve

Problem for low-voltage supply: Output voltage cannot

swing close to the supply rails & stacked diodes

Class-AB output stages - 3

CMOS Analog Design Using All-Region MOSFET

Modeling

42

CMOS common-source output stage and push (I

P

)

and pull (I

N

) currents versus output current.

Class-AB output stages - 4

CMOS Analog Design Using All-Region MOSFET

Modeling

43

Rail-to-rail output stage and bias circuit for class-AB operation

Class-AB output stages - 5

CMOS Analog Design Using All-Region MOSFET

Modeling

44

Two-stage op amp with rail-to-rail class-AB output stage

Class-AB output stages - 6

CMOS Analog Design Using All-Region MOSFET

Modeling

45

R

2

+

v

od

-

-

+

R

1

+

v

id

-

R

1

+

-

R

2

v

o1

v

o2

t

t

t

t

v

od

V

ocm

V

ocm

FD = Fully-differential

SE = Single-ended

FD SE

V

opp

2: 1

Noise power 2: 1

SNR 2: 1

Even-order harm. No (match) Yes

CMRR, PSRR Improved

CMFB circuit Yes No

Area ~2: 1

Fully-differential amplifiers - 1

CMOS Analog Design Using All-Region MOSFET

Modeling

46

M

1

M

2

M

6

M

3

M

4

+

-

V

DD

V

SS

V

bias

v

o2

v

i1

v

i2

v

o1

+ -

M

5

I

T

/2

I

T

/2

+

M

3r

I

T

/2

M

1r

M

5r

V

cm,ref

A

A

1

Example of idealized FD amplifier (transistors assumed to be matched) and

bias network employed to set the common-mode output voltage to V

cm,ref

.

Fully-differential amplifiers - 2

CMOS Analog Design Using All-Region MOSFET

Modeling

47

V

DD

I

T

M

1

M

2

M

5

M

3

M

4

+

-

V

SS

V

bias

v

o2

v

i1

v

i2

v

o1

+

V

cm,ref

R R

A

V

DD

I

T

M

1r

M

2r

M

5r

M

3r

M

4r

+

-

V

SS

V

bias

out

Simplified scheme of an FD amplifier. On the right is the low-gain

amplifier, a replica of the main amplifier but with diode connected loads.

Fully-differential amplifiers - 3

CMOS Analog Design Using All-Region MOSFET

Modeling

48

V

DD

I

T

/4

M

2

M

1

M

5

M

4

M

3

-

+

V

cm,ref

I

T

M

1

M

2

M

5

M

3

/2

+

-

v

o2

v

i1

v

i2

v

o1

R R

V

ocm

V

ocm

2M

3

M

5

I

T

V

SS

I

T

/4

I

T

C

L

C

L

M

3

/2

M

4

/2

M

4

/2

FD amplifier with resistive CM detector and the error amplifier on the

right employed to set the common-mode output voltage to V

cm,ref

.

Fully-differential amplifiers - 4

CMOS Analog Design Using All-Region MOSFET

Modeling

49

V

cm,ref

V

SS

I

T

4M

1

8M

1

2M

5

2I

T

4M

1

4M

1

M

5

M

3

+

-

v

o2

v

i1

v

i2

v

o1

V

ocm

M

3

M

5

I

T

I

T

I

T

M

3

4M

1

to

V

cm,ref

(or V

SS

)

R R

V

ocm

An FD amplifier where the two CM transconductors are

replicas of the DM transconductor

Fully-differential amplifiers - 5

CMOS Analog Design Using All-Region MOSFET

Modeling

50

M

1

v

i1

2M

1

V

DD

4M

1

4M

1

M

3

+

-

v

o2

v

i2

v

o1

I

T

M

3

V

SS

M

1

2M

1

V

cm,ref

M

1

v

o1

M

1

v

o2

2M

3

I

T

/2

I

T

/2

I

T

/2

I

T

/2

I

T

/4 I

T

/4

An FD amplifier employing CM detection based on differential

pairs which are replicas of the DM transconductor

Fully-differential amplifiers - 6

CMOS Analog Design Using All-Region MOSFET

Modeling

51

2M

4C

V

DD

I

T

M

1A

M

2A

M

5A

M

3A

M

4A

+

-

V

SS

v

o2

v

i1

v

i2

v

o1

V

cm,ref

M

5B

V

cm,ref

I

T

/2

I

T

/2

I

T

M

6A

M

7A

M

6B

M

7B

2M

4B

An FD amplifier using transistors in the triode region

to set the common-mode output voltage to Vcm,ref

Fully-differential amplifiers - 7

CMOS Analog Design Using All-Region MOSFET

Modeling

52

Complete schematic of an FD two-stage op amp

including the CM control circuit

Fully-differential amplifiers - 8

CMOS Analog Design Using All-Region MOSFET

Modeling

53

Complete schematic of an FD folded-cascode op

amp fabricated in 1.75 m CMOS technology

Fully-differential amplifiers - 9

CMOS Analog Design Using All-Region MOSFET

Modeling

54

I

T

A

4M

1

4M

2

M

3

M

4

M

5

M

6

M

7

M

8

M

9

M

10

M

11

+ -

I

T

I

T

V

DD

V

SS

V

B3

v

o1

v

i1

v

i2

V

B2

V

B1

V

B4

v

o2

B

+

-

(a)

I

T

/2

I

T

/2

M

1

2M

2

M

12

M

12

V

SS

M

1

2M

2

V

cm,ref

M

1

v

o1

M

1

v

o2

2M

12

I

T

/2

I

T

/2

I

T

/2

I

T

/4 I

T

/4

(b)

A

B

i

oA

i

oB

Simplified schematics of (a) folded-cascode op amp

and (b) common-mode feedback circuit

Fully-differential amplifiers - 10

You might also like

- CAPE Caribbean Studies Solutions 2005Document15 pagesCAPE Caribbean Studies Solutions 2005timahNo ratings yet

- DC/DC Converters For Electric Vehicles: Monzer Al Sakka, Joeri Van Mierlo and Hamid GualousDocument25 pagesDC/DC Converters For Electric Vehicles: Monzer Al Sakka, Joeri Van Mierlo and Hamid Gualousme_droidNo ratings yet

- Gương Dòng TH Đ NG Và Tích C CDocument45 pagesGương Dòng TH Đ NG Và Tích C Cngoc an nguyenNo ratings yet

- AnalogicdesignDocument42 pagesAnalogicdesignPrabhu SakinalaNo ratings yet

- Electric VLSI Manual by DR Arnold PaglinawanDocument8 pagesElectric VLSI Manual by DR Arnold PaglinawanJJ AcotNo ratings yet

- 7.chapter7 - Operational AmplifierDocument36 pages7.chapter7 - Operational Amplifierngoc an nguyenNo ratings yet

- 9085 CMOS Analog Design Chapter 5Document25 pages9085 CMOS Analog Design Chapter 5istlyyNo ratings yet

- (PPT) Noise and Matching in CMOS (Analog) CircuitsDocument49 pages(PPT) Noise and Matching in CMOS (Analog) CircuitsAdam112211No ratings yet

- Analog Circuits: GATE EC Topic Wise QuestionsDocument50 pagesAnalog Circuits: GATE EC Topic Wise Questionsdeepthi1993100% (1)

- Đáp Ứng Tần Số Của Mạch Khuếch ĐạiDocument51 pagesĐáp Ứng Tần Số Của Mạch Khuếch Đạingoc an nguyenNo ratings yet

- Gate Solved Paper Ec Analog ElectronicsDocument77 pagesGate Solved Paper Ec Analog ElectronicssaiNo ratings yet

- CH 2: Basic MOS Device PhysicsDocument20 pagesCH 2: Basic MOS Device PhysicsMuhammad FaizanNo ratings yet

- Ac-Ac ConverterDocument79 pagesAc-Ac ConverterMr. Amit Kumar SinghNo ratings yet

- MmuDocument113 pagesMmuSunny SanNo ratings yet

- Analog Ic Design LabDocument43 pagesAnalog Ic Design LabDileep KumarNo ratings yet

- 4.chapter4 CMOS Multistages Differential AmplifierDocument60 pages4.chapter4 CMOS Multistages Differential Amplifierngoc an nguyenNo ratings yet

- Lab (GPDK)Document49 pagesLab (GPDK)Murali MurariNo ratings yet

- CMOS Inverter SchematicDocument19 pagesCMOS Inverter SchematicdileshwarNo ratings yet

- Vtu NotesDocument91 pagesVtu NotesSanthosh Chandu CNo ratings yet

- Vtu Lab Manuals VlsiDocument79 pagesVtu Lab Manuals VlsisrikanthuasNo ratings yet

- Eee Formula SheetDocument147 pagesEee Formula SheetNaveen Kumar100% (1)

- 9086 CMOS Analog Design Chapter 6Document24 pages9086 CMOS Analog Design Chapter 6Yogindr SinghNo ratings yet

- 1 Introduction To Analog IC DesignDocument41 pages1 Introduction To Analog IC Designnavinkumarrr588No ratings yet

- 7+Diode+Circuits RectifiersDocument31 pages7+Diode+Circuits RectifiersRyan Anthony AndalNo ratings yet

- AC Voltage Contoller Circuits by MMRDocument124 pagesAC Voltage Contoller Circuits by MMRananthashyam201No ratings yet

- Basic Building BlockDocument34 pagesBasic Building BlockAmmar Ajmal100% (1)

- CMOS Analog Design Using All-Region MOSFET Modeling: Advanced MOS Transistor ModelingDocument101 pagesCMOS Analog Design Using All-Region MOSFET Modeling: Advanced MOS Transistor ModelingashishmanyanNo ratings yet

- Notes On WL RatioDocument2 pagesNotes On WL Ratiohenz Josh100% (1)

- CMOS BasicsDocument41 pagesCMOS BasicsYeshoda MallikarjunaNo ratings yet

- RM-11 Metronic Primary Watthour StandardDocument2 pagesRM-11 Metronic Primary Watthour StandardMiko QuijanoNo ratings yet

- SEL 4283 Analog CMOS IC Design Single Stage Amplifiers: Small Signal Model 1Document52 pagesSEL 4283 Analog CMOS IC Design Single Stage Amplifiers: Small Signal Model 1jitendraNo ratings yet

- A Survey of 5G Network: Architecture and Emerging TechnologiesDocument27 pagesA Survey of 5G Network: Architecture and Emerging TechnologiesDijar VrellaNo ratings yet

- Introduction To Power ElectronicsDocument71 pagesIntroduction To Power ElectronicsAshwini SinghNo ratings yet

- AVR492: Brushless DC Motor Control Using AT90PWM3: Application NoteDocument26 pagesAVR492: Brushless DC Motor Control Using AT90PWM3: Application NotenicoletabytaxNo ratings yet

- EEE3002 Microprocessors Tutorial 1Document5 pagesEEE3002 Microprocessors Tutorial 1Ricky Kwan Ki KwokNo ratings yet

- CMOS Inverter LayoutDocument2 pagesCMOS Inverter LayoutRen ValerosoNo ratings yet

- EE8353 - Electrical Drives and Controls MCQDocument41 pagesEE8353 - Electrical Drives and Controls MCQMadhesh RajuNo ratings yet

- Documentation of PMSMDocument89 pagesDocumentation of PMSM07be1a0213No ratings yet

- Circuits Devices and ApplicationsDocument30 pagesCircuits Devices and ApplicationsTe NgNo ratings yet

- V.C.U (Vehicle Control Unit) PDFDocument5 pagesV.C.U (Vehicle Control Unit) PDFrahul kNo ratings yet

- Advanced Battery Management System Using MATLAB SimulinkDocument6 pagesAdvanced Battery Management System Using MATLAB SimulinkAkash KumarNo ratings yet

- PSIM User Manual PDFDocument280 pagesPSIM User Manual PDFHelenio Salvador PizarroNo ratings yet

- Low Power Vlsi Circuits and Systems - Ajit PalDocument26 pagesLow Power Vlsi Circuits and Systems - Ajit PalAnushaNo ratings yet

- Cs8351 Digital Principles and System Design MCQDocument53 pagesCs8351 Digital Principles and System Design MCQveluNo ratings yet

- Presentation On Analog ElectronicsDocument334 pagesPresentation On Analog ElectronicssamuelNo ratings yet

- Switched Reluctance MotorDocument75 pagesSwitched Reluctance Motor15BEE1120 ISHAV SHARDANo ratings yet

- Vlsi Laboratory: List of ExperimentsDocument49 pagesVlsi Laboratory: List of ExperimentssantoshNo ratings yet

- CMOS IntroDocument45 pagesCMOS IntroNishanth Nish0% (1)

- Sensorless BLDC Control With Back-EMF FilteringDocument28 pagesSensorless BLDC Control With Back-EMF FilteringRomeo Đạp Xíck LôNo ratings yet

- Ec8452 Ec-Ii Unit-2Document103 pagesEc8452 Ec-Ii Unit-2Ananda Sailesh KNo ratings yet

- Design of Brushless Permanent Magnet Motor For Electric Vehicle ApplicationDocument55 pagesDesign of Brushless Permanent Magnet Motor For Electric Vehicle ApplicationDeepak sawNo ratings yet

- Digital Ic Design Module 3 InverterDocument37 pagesDigital Ic Design Module 3 InvertervmspraneethNo ratings yet

- Ec8452 Ec-Ii Unit-1Document122 pagesEc8452 Ec-Ii Unit-1Ananda Sailesh KNo ratings yet

- E-Book PPT On Embedded Embedded Automotive, NewDocument30 pagesE-Book PPT On Embedded Embedded Automotive, NewMishmy T ShibukumarNo ratings yet

- Tms 320 F 28379 DDocument222 pagesTms 320 F 28379 DJuan Ku LosanoNo ratings yet

- Analog Circuit Design Notes-2Document85 pagesAnalog Circuit Design Notes-2itsnirosNo ratings yet

- Analog Circuits With SolutionsDocument98 pagesAnalog Circuits With SolutionsvikramvivNo ratings yet

- Fixed Point NumbersDocument12 pagesFixed Point NumbersDramane BonkoungouNo ratings yet

- Driver Motor BrushlesDocument48 pagesDriver Motor BrushlesGONAJ2008No ratings yet

- 9311 - CMOS Analog Design Chapter 10Document23 pages9311 - CMOS Analog Design Chapter 10raju.kprr8862No ratings yet

- MIT6 012S09 Ex03 Final 07Document18 pagesMIT6 012S09 Ex03 Final 07Gopi KrishnaNo ratings yet

- Presentation No 05Document83 pagesPresentation No 05gary2ndhome2182No ratings yet

- 9D06106c Low Power VLSI DesignDocument1 page9D06106c Low Power VLSI Designraju.kprr8862No ratings yet

- 9A02406 Network TheoryDocument8 pages9A02406 Network TheorysivabharathamurthyNo ratings yet

- CyberDocument2 pagesCyberraju.kprr8862No ratings yet

- 9A04601 Digital CommunicationsDocument4 pages9A04601 Digital Communicationsraju.kprr8862No ratings yet

- Analog Electronics Quiz-2 For All Participants (14th June 2013 To 21st June 2013) 3Document4 pagesAnalog Electronics Quiz-2 For All Participants (14th June 2013 To 21st June 2013) 3raju.kprr8862No ratings yet

- 5 Linear Block CodesDocument29 pages5 Linear Block CodesSuprit PaulNo ratings yet

- 9311 - CMOS Analog Design Chapter 10Document23 pages9311 - CMOS Analog Design Chapter 10raju.kprr8862No ratings yet

- RR310406 Digital CommunicationsDocument1 pageRR310406 Digital Communicationsraju.kprr8862No ratings yet

- ELEN-610: Data Converters: Assignment #5Document1 pageELEN-610: Data Converters: Assignment #5raju.kprr8862No ratings yet

- Lesson Plan: S.No Week No Topics To Be Covered Planned Hours Actual HoursDocument31 pagesLesson Plan: S.No Week No Topics To Be Covered Planned Hours Actual Hoursraju.kprr8862No ratings yet

- Lecture 4Document51 pagesLecture 4tuyambaze jean claudeNo ratings yet

- Smartycam HD GP Smartycam HDDocument4 pagesSmartycam HD GP Smartycam HDAhmet KöseleciNo ratings yet

- Adf4110 4111 4112 4113Document28 pagesAdf4110 4111 4112 4113condejhonnyNo ratings yet

- HEATING ELEMENT (With or Without Fuse) : Service Bulletin Washing 2520-2530Document1 pageHEATING ELEMENT (With or Without Fuse) : Service Bulletin Washing 2520-2530Torozan RomicaNo ratings yet

- Design and Analysis of Phase Locked Loop in 90mm CmosDocument7 pagesDesign and Analysis of Phase Locked Loop in 90mm CmosabhishekNo ratings yet

- Sony KV - 29fs150Document85 pagesSony KV - 29fs150GustavoTovarNo ratings yet

- 9IS90004 EWTQ 500 7-05 MultilinguaDocument3 pages9IS90004 EWTQ 500 7-05 MultilinguatouchmemoryNo ratings yet

- Brine Solution Power BankDocument14 pagesBrine Solution Power BankVisar Mae Fullo LagoNo ratings yet

- TX 5 KW ElettronikaDocument3 pagesTX 5 KW Elettronikayulimedan919No ratings yet

- Samsung Level Over Manual PDFDocument296 pagesSamsung Level Over Manual PDFSotiris KousoutNo ratings yet

- SW-HF 5.1 5005 (V2) Service Manual (Without G9 Input) - 12.15Document30 pagesSW-HF 5.1 5005 (V2) Service Manual (Without G9 Input) - 12.15Costin BeldicaNo ratings yet

- Ground Penetrating Radar - Shawna Jones, Meghan McGinn, Nicholas RiordanDocument19 pagesGround Penetrating Radar - Shawna Jones, Meghan McGinn, Nicholas RiordanRafael Manfrin MendesNo ratings yet

- Data Sheet L298 PDFDocument13 pagesData Sheet L298 PDFbaymax love spideyNo ratings yet

- SW-5.1 3005 Service ManualDocument17 pagesSW-5.1 3005 Service ManualBizoo76No ratings yet

- Bicotest Model T272 US A4v2Document2 pagesBicotest Model T272 US A4v2Jusril A HidayatNo ratings yet

- Chapter 7 - Frequency ResponseDocument47 pagesChapter 7 - Frequency ResponseFakrul HanifNo ratings yet

- Crest Factor - Wikipedia, The Free EncyclopediaDocument2 pagesCrest Factor - Wikipedia, The Free Encyclopediadonodoni0008100% (1)

- Microstrip Patch Antenna and Its ApplicationDocument20 pagesMicrostrip Patch Antenna and Its ApplicationBrhane DadsoNo ratings yet

- Exp No8Document9 pagesExp No8Mohd Syamsul Ramli100% (1)

- Mdrs155ec IntroDocument84 pagesMdrs155ec Introshohagpt81No ratings yet

- UC3848Document9 pagesUC3848Sergio Daniel BarretoNo ratings yet

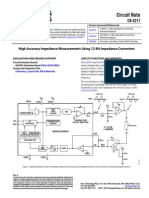

- High Accuracy Impedance Measurements Using 12-Bit Impedance ConvertersDocument6 pagesHigh Accuracy Impedance Measurements Using 12-Bit Impedance Converterschristobal_huntaNo ratings yet

- Ads 1298Document80 pagesAds 1298Juan GiraldoNo ratings yet

- Am Balanced ModulatorDocument9 pagesAm Balanced ModulatorjucxxxNo ratings yet

- The Cellular Concept - System Design FundamentalsDocument54 pagesThe Cellular Concept - System Design FundamentalsREHMAN MALIK100% (1)

- GladiatorDocument12 pagesGladiatorvickyaryanNo ratings yet

- Cellphone Based Remote Controller For Water PumpDocument5 pagesCellphone Based Remote Controller For Water Pumpalokedas1No ratings yet