Professional Documents

Culture Documents

Jntu, Hyderabad

Uploaded by

Senthil Kumar0 ratings0% found this document useful (0 votes)

22 views34 pagesEXPERT SYSTEMS AND SOLUTIONS

Center for Research Projects

Email: expertsyssol@gmail.com,

Cell:9952749533, 8608603634

www.researchprojects.info

Neyveli - Indra Nagar, Near to Neyveli Arch GATE Branches also at Chennai and Chidambaram

IEEE and Non IEEE based Projects For

Final year students of B.E in EEE, ECE, EIE, Mech, Automobile, Mechatronics ,

M.E (Power Systems)

M.E (Applied Electronics)

M.E (Power Electronics)

M.E (VLSI Design)

M.E ( Control Systems )

M.E ( Process Control )

Ph.D Electrical and Electronics.

Power Systems

Power Electronics

Students can assemble their hardware in our Research labs. Experts will be guiding the projects.

We provide you with

• Confirmation letter, Project Estimation, Completion Certificate

• Abstracts Block Diagram, Circuit Diagram of the project

• Supporting documents- notes

• Datasheets, Reference Papers

• Software tools and Real time support.

• Online Classes for Master degree and PhD Projects

• Journal Publication for researchers in Power systems and Power electronics

Short term and Online courses

• C and C++, Embedded C,

• MicroController 8051,PIC 16F877

• ARM 7 and ARM 9 Processors

• MATLAB Fundamental, MATLAB Simpower Systems,

• MATLAB Control systems

• MATLAB Fuzzy Toolbox

• MATLAB GA , ANN Toolbox

• Engineering MATHS MI, MII and MIII

POWER SYSTEMS PROJECTS

Deregulated Systems, Wind power Generation and Grid connection, Profit based Unit commitment, Economic dispatch, Using AI methods for Voltage stability FLC Control, Transformer Fault Identifications, SCADA in Power system Automation, FireFly Algorithm, PSO and QPSO , Genetic Algorithm, Fuzzy logic, Artifical Neural networks, PSCAD for Power systems.

POWER ELECTRONIC PROJECTS

Three phase inverter and converters, Buck Boost Converter Matrix Converter, Inverter and converter topologies, Fuzzy based control of Electric Drives, Optimal design of Electrical Machines, BLDC and SR motor Drives.

Copyright

© © All Rights Reserved

Available Formats

PPT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentEXPERT SYSTEMS AND SOLUTIONS

Center for Research Projects

Email: expertsyssol@gmail.com,

Cell:9952749533, 8608603634

www.researchprojects.info

Neyveli - Indra Nagar, Near to Neyveli Arch GATE Branches also at Chennai and Chidambaram

IEEE and Non IEEE based Projects For

Final year students of B.E in EEE, ECE, EIE, Mech, Automobile, Mechatronics ,

M.E (Power Systems)

M.E (Applied Electronics)

M.E (Power Electronics)

M.E (VLSI Design)

M.E ( Control Systems )

M.E ( Process Control )

Ph.D Electrical and Electronics.

Power Systems

Power Electronics

Students can assemble their hardware in our Research labs. Experts will be guiding the projects.

We provide you with

• Confirmation letter, Project Estimation, Completion Certificate

• Abstracts Block Diagram, Circuit Diagram of the project

• Supporting documents- notes

• Datasheets, Reference Papers

• Software tools and Real time support.

• Online Classes for Master degree and PhD Projects

• Journal Publication for researchers in Power systems and Power electronics

Short term and Online courses

• C and C++, Embedded C,

• MicroController 8051,PIC 16F877

• ARM 7 and ARM 9 Processors

• MATLAB Fundamental, MATLAB Simpower Systems,

• MATLAB Control systems

• MATLAB Fuzzy Toolbox

• MATLAB GA , ANN Toolbox

• Engineering MATHS MI, MII and MIII

POWER SYSTEMS PROJECTS

Deregulated Systems, Wind power Generation and Grid connection, Profit based Unit commitment, Economic dispatch, Using AI methods for Voltage stability FLC Control, Transformer Fault Identifications, SCADA in Power system Automation, FireFly Algorithm, PSO and QPSO , Genetic Algorithm, Fuzzy logic, Artifical Neural networks, PSCAD for Power systems.

POWER ELECTRONIC PROJECTS

Three phase inverter and converters, Buck Boost Converter Matrix Converter, Inverter and converter topologies, Fuzzy based control of Electric Drives, Optimal design of Electrical Machines, BLDC and SR motor Drives.

Copyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

22 views34 pagesJntu, Hyderabad

Uploaded by

Senthil KumarEXPERT SYSTEMS AND SOLUTIONS

Center for Research Projects

Email: expertsyssol@gmail.com,

Cell:9952749533, 8608603634

www.researchprojects.info

Neyveli - Indra Nagar, Near to Neyveli Arch GATE Branches also at Chennai and Chidambaram

IEEE and Non IEEE based Projects For

Final year students of B.E in EEE, ECE, EIE, Mech, Automobile, Mechatronics ,

M.E (Power Systems)

M.E (Applied Electronics)

M.E (Power Electronics)

M.E (VLSI Design)

M.E ( Control Systems )

M.E ( Process Control )

Ph.D Electrical and Electronics.

Power Systems

Power Electronics

Students can assemble their hardware in our Research labs. Experts will be guiding the projects.

We provide you with

• Confirmation letter, Project Estimation, Completion Certificate

• Abstracts Block Diagram, Circuit Diagram of the project

• Supporting documents- notes

• Datasheets, Reference Papers

• Software tools and Real time support.

• Online Classes for Master degree and PhD Projects

• Journal Publication for researchers in Power systems and Power electronics

Short term and Online courses

• C and C++, Embedded C,

• MicroController 8051,PIC 16F877

• ARM 7 and ARM 9 Processors

• MATLAB Fundamental, MATLAB Simpower Systems,

• MATLAB Control systems

• MATLAB Fuzzy Toolbox

• MATLAB GA , ANN Toolbox

• Engineering MATHS MI, MII and MIII

POWER SYSTEMS PROJECTS

Deregulated Systems, Wind power Generation and Grid connection, Profit based Unit commitment, Economic dispatch, Using AI methods for Voltage stability FLC Control, Transformer Fault Identifications, SCADA in Power system Automation, FireFly Algorithm, PSO and QPSO , Genetic Algorithm, Fuzzy logic, Artifical Neural networks, PSCAD for Power systems.

POWER ELECTRONIC PROJECTS

Three phase inverter and converters, Buck Boost Converter Matrix Converter, Inverter and converter topologies, Fuzzy based control of Electric Drives, Optimal design of Electrical Machines, BLDC and SR motor Drives.

Copyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

You are on page 1of 34

DSP OVERVIEW

DSPs are like traditional embedded

microprocessors

DSPs are designed to meet sophisticated signal

processing algorithms

DSPs are used in drives, audio & video

applications, image applications, bio medical,

industrial automations etc.,

ADVANTAGES OF DSP

Easy to change applications

Better control & accuracy

Easy to execute complex algorithms like svpwm,

vector control , dtc etc.,

Compact in size (ic)

Cost effective (ic) for particular applications.

DSP LEADING MANUFACTURERS

Texas instruments

Analog devices

Motorola

TEXAS INSTRUMENTS DSP FAMILY

TMS320C2000

C24x, C28x

TMS320C5000

C54x,C55x

TMS320C6000

C62x,C64x,C67x

TMS320 DEVICE NOMENCLATURE

DSP BASED MOTOR CONTROL

TMS320C2000 series offers various processors for motor

control applications

Based on the requirements user can choose the

following processors

TMS320C240

TMS320LF2407

TMS320LF2812

LF2407 KEY FEATURES

3.3v operating volts

16 bit fixed point processor with 144 pins

40MHz operating frequency

32KWord FLASH memory, 2.5 K Word RAM

40 general-purpose I/O (GPIO) lines

Event manager

10 bit, 16 channel ADC with 500ns as conversion time

Serial communication interface (SCI)

Serial peripheral interface (SPI)

Watchdog timer

In-built space vector hardware

TMS320LF2407 ARCHITECTURE

CENTRAL PROCESSING UNIT

A 32-bit central arithmetic logic unit (CALU)

A 32-bit accumulator

Data-scaling shifters

A 16-bit X 16-bit multiplier

A 32-bit product register

8 auxiliary registers and an auxiliary register arithmetic unit

MEMORY

544 words * 16 bits of on-chip data/program dual-

access RAM

32K words * 16 bits of on-chip program

Flash EEPROM

2K words * 16 bits of single-access RAM

External memory interface module

PLL CLOCK MODULE

PLL Clock Module provides all of the clocks required

for the entire device.

CPUCLK This is the highest frequency clock

provided by the module and is used by the CPU, all

memories and any peripherals tied directly to the

CPUs buses, including an external memory interface

if used.

SYSCLK This clock is a half or a quarter the rate of

CPUCLK. It is used to clock all the peripherals on the

TI peripheral bus.

WDCLK This is the low power clock used by the

watchdog timer/real- time interrupt module.

WATCHDOG TIMER MODULE

Internal 8 bit re-settable up counting timer, that

reset the system if software fails to operate

properly.

If the software goes into an improper loop, or if

the CPU becomes temporarily disrupted, the WD

timer overflows to assert a system reset.

The watchdog increases the reliability of the

CPU, thus ensuring system integrity.

SERIAL COMMUNICATION INTERFACE MODULE

The programmable SCI module supports digital

communications between the CPU and other

asynchronous peripherals.

To ensure data integrity, the SCI checks data that

has been received for break detection, parity,

overrun, and framing errors.

The speed of the bit rate (baud) is programmable to

over 64K different speeds through a 16-bit baud-

select register.

SERIAL PERIPHERAL INTERFACE MODULE

The SPI is a high-speed synchronous serial input/

output (I/O) port that allows a serial bit stream of

programmed length (one to eight bits) to be shifted

into and out of the device at a programmed bit-

transfer rate.

The SPI is normally used for communications

between the DSP controller and external peripherals

or another controller.

SPI applications include external I/O or peripheral

expansion via devices such as shift registers,

display drivers, and analog-to-digital converters

(ADCs).

DIGITAL I/O MODULE

The digital I/O ports module provides a

flexible method for controlling both

dedicated I/O and shared pin functions

The LF2407 has a total of 40 shared I/O lines

I/O ports can be used as i/o lines or as pwm

lines

EVENT MANAGER (EV) MODULE

The EV module provides functions and features that are required for motor

control applications

LF2407 has two event managers EVA & EVB

Features:

2 general-purpose (GP) timers

3 compare units

3 capture units

quadrature encoder pulse(QEP) circuit

space vector pwm circuits

dead band generation units

output logic circuits

EV BLOCK DIAGRAM

PWM OUTPUT

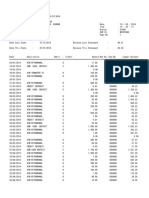

EVENT MANAGER REGISTERS

EVENT MANAGER TIMER REGISTERS

GPTCONA - General purpose timer control register

T1CNT - Timer1 counter register

T1CMPR - Timer1 compare register

T1PR - Timer1 period register

T1CON - Timer1 control register

EVENT MANAGER COMPARE CONTROL REGISTERS

COMCONA - Compare control register

ACTRA - Action control register

DBTCONA - Dead-band control register

CPMR1 - Compare register1

CMPR2 - Compare register2

CMPR3 - Compare register3

SPACE VECTOR PWM MODULE

The EV module has built-in hardware to

generate svpwm

Software is used to generate svpwm outputs

CAPTURE & QEP UNITS

The capture & QEP units can be used to

interface with an optical encoder to get speed

information from the rotating machine

Capture unit is used to sense the actual speed of

the machine

QEP is used to find the direction of rotation of

the machine

ANALOG TO DIGITAL CONVERTER

Features:

10-bit ADC core with built-in S/H circuit

Fast conversion time of 500ns

16 multiplexed analog input

Two independent 8 state sequencer can be

operated in dual-sequencer or cascaded mode

16 result registers to store the digital values

ADC BLOCK DIAGRAM

ADC CONTROL REGISTERS

ADCTRL1 - Adc control register1

ADCTRL2 - Adc control register2

MAXCONV - Maximum conversion reg

CHSELSEQn - Channel select registers

RESULTn - Adc result registers

PROGRAM MEMORY ADDRESS FOR TRAINER KIT

Starting

address

Ending

address

Description

Memory

Type

0000 BFFF

ASSEMBLER,

DISASSEMBLER,

SERIAL MONITOR

PROGRAM AREA

EEPROM

C000

FFFF

USER

PROGRAM

MEMORY

AREA

RAM

LF2407 DATA MEMORY

Total memory = 0000h FFFFh (64KW)

Total no. pages = 200h

Every page contains 80h locations

Page 0 = 0h * 80h = 0000 to 007F

Page 1 = 1h * 80h = 0080 to 00FF

. . . . . . .

. . . . . . .

. . . . . . .

Page 100 = 100h * 80h = 8000 to 807F

Page 1FF = 1FFh * 80h = FF80 to FFFF

DATA MEMORY ADDRESS FOR TRAINER KIT

Starting

address

Ending

address

Description

Memory

Type

0000 7FFF

8000

FFFF

RAM

ON-CHIP RAM

USER DATA

MEMORY AREA

RAM

ASSEMBLEY LANGUAGE PROGRAMS

ADDI TI ON

.TEXT

.MMREGS

START:

LDP #100H

LACC 0H

ADD 1H

SACL 2H

H: B H

Input:

8000 3333

8001 2222

Output:8002 - 5555

.TEXT

.MMREGS

START:

LDP #100H

LACC #3333H

ADD #2222H

SACL 0H

H: B H

Output:

8000 5555

SIMPLE PROGRAM FOR PWM GENERATION

.include 2407regs.h

.text

Start:

LDP #232

SPLK #2000,T1PR

SPLK #1000,T1CMPR

SPLK #1000,T2CMPR

SPLK #1000,T3CMPR

SPLK #0999H,ACTRA

SPLK #8200H,COMCONA

SPLK #0000,T1CNT

SPLK #0000,T2CNT

SPLK #0000,T3CNT

SPLK #0802H,T1CON

SPLK #0842H,T1CON

END B END

You might also like

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Business Testimony 3Document14 pagesBusiness Testimony 3Sapan BanerjeeNo ratings yet

- 7Document101 pages7Navindra JaggernauthNo ratings yet

- Sacmi Vol 2 Inglese - II EdizioneDocument416 pagesSacmi Vol 2 Inglese - II Edizionecuibaprau100% (21)

- ABB Price Book 524Document1 pageABB Price Book 524EliasNo ratings yet

- Outage Analysis of Wireless CommunicationDocument28 pagesOutage Analysis of Wireless CommunicationTarunav SahaNo ratings yet

- Sealant Solutions: Nitoseal Thioflex FlamexDocument16 pagesSealant Solutions: Nitoseal Thioflex FlamexBhagwat PatilNo ratings yet

- MEMORANDUMDocument8 pagesMEMORANDUMAdee JocsonNo ratings yet

- Random Variable N N Mean or Expected Value: Number of Ducks Type of Duck AmountDocument2 pagesRandom Variable N N Mean or Expected Value: Number of Ducks Type of Duck AmountAngie PastorNo ratings yet

- Bank Statement SampleDocument6 pagesBank Statement SampleRovern Keith Oro CuencaNo ratings yet

- T3A-T3L Servo DriverDocument49 pagesT3A-T3L Servo DriverRodrigo Salazar71% (7)

- Human Resource Management by John Ivancevich PDFDocument656 pagesHuman Resource Management by John Ivancevich PDFHaroldM.MagallanesNo ratings yet

- Revit 2019 Collaboration ToolsDocument80 pagesRevit 2019 Collaboration ToolsNoureddineNo ratings yet

- Quality in CRDocument10 pagesQuality in CRkaushikcrNo ratings yet

- Product Guide TrioDocument32 pagesProduct Guide Triomarcosandia1974No ratings yet

- UBITX V6 MainDocument15 pagesUBITX V6 MainEngaf ProcurementNo ratings yet

- La Salle Lipa Integrated School Senior High School Community 1 Quarter Summative Assessment Earth Science AY 2021-2022 Household Conservation PlanDocument4 pagesLa Salle Lipa Integrated School Senior High School Community 1 Quarter Summative Assessment Earth Science AY 2021-2022 Household Conservation PlanKarlle ObviarNo ratings yet

- COGELSA Food Industry Catalogue LDDocument9 pagesCOGELSA Food Industry Catalogue LDandriyanto.wisnuNo ratings yet

- Durga Padma Sai SatishDocument1 pageDurga Padma Sai SatishBhaskar Siva KumarNo ratings yet

- Vodafone M2M Integrated M2M Terminals Overview BrochureDocument4 pagesVodafone M2M Integrated M2M Terminals Overview BrochureJamie JordanNo ratings yet

- Paul Milgran - A Taxonomy of Mixed Reality Visual DisplaysDocument11 pagesPaul Milgran - A Taxonomy of Mixed Reality Visual DisplaysPresencaVirtual100% (1)

- BMT6138 Advanced Selling and Negotiation Skills: Digital Assignment-1Document9 pagesBMT6138 Advanced Selling and Negotiation Skills: Digital Assignment-1Siva MohanNo ratings yet

- EASY DMS ConfigurationDocument6 pagesEASY DMS ConfigurationRahul KumarNo ratings yet

- 0063 - Proforma Accompanying The Application For Leave WITHOUT ALLOWANCE Is FORWARDED To GOVERNMEDocument4 pages0063 - Proforma Accompanying The Application For Leave WITHOUT ALLOWANCE Is FORWARDED To GOVERNMESreedharanPN100% (4)

- Residential BuildingDocument5 pagesResidential Buildingkamaldeep singhNo ratings yet

- ATLAS HONDA Internship ReportDocument83 pagesATLAS HONDA Internship ReportAhmed Aitsam93% (14)

- Bisleri 2.0Document59 pagesBisleri 2.0Dr Amit Rangnekar100% (4)

- Conflict WaiverDocument2 pagesConflict WaiverjlurosNo ratings yet

- Pilot'S Operating Handbook: Robinson Helicopter CoDocument200 pagesPilot'S Operating Handbook: Robinson Helicopter CoJoseph BensonNo ratings yet

- RCC Design of Toe-Slab: Input DataDocument2 pagesRCC Design of Toe-Slab: Input DataAnkitaNo ratings yet