Professional Documents

Culture Documents

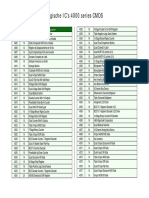

8 - Integrated Circuits

Uploaded by

Prabath De Silva0 ratings0% found this document useful (0 votes)

20 views28 pagesEncoding circuits are generally at the input end of a system to convert the input signal into a binary code necessary for the operation of the system. They convert an analogue signal to BCD or 4 bit binary code; take in a binary signal and convert it into another code to suit the system eg: OCTAL to BCD. In Flight Data recording some of the inputs into the system are in analogue form, such as dc, ac or syncro signals. This

Original Description:

Copyright

© © All Rights Reserved

Available Formats

PPT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentEncoding circuits are generally at the input end of a system to convert the input signal into a binary code necessary for the operation of the system. They convert an analogue signal to BCD or 4 bit binary code; take in a binary signal and convert it into another code to suit the system eg: OCTAL to BCD. In Flight Data recording some of the inputs into the system are in analogue form, such as dc, ac or syncro signals. This

Copyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

20 views28 pages8 - Integrated Circuits

Uploaded by

Prabath De SilvaEncoding circuits are generally at the input end of a system to convert the input signal into a binary code necessary for the operation of the system. They convert an analogue signal to BCD or 4 bit binary code; take in a binary signal and convert it into another code to suit the system eg: OCTAL to BCD. In Flight Data recording some of the inputs into the system are in analogue form, such as dc, ac or syncro signals. This

Copyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

You are on page 1of 28

These are generally at the input end of a

system to convert the input signal into a

binary code necessary for the operation of

the system.

Encoding circuits may take many forms eg:

convert an analogue signal to BCD or 4 bit

binary code; take in a binary signal and

convert it into another code to suit the

system eg: OCTAL to BCD.

The drawing shows a keyboard layout

(decimal input) to give a BCD output. By

pressing anyone key or switch (suitably

decimal numbered) the appropriate BCD code

is given at the output.

Assume "4" is pressed then diode D5 will

conduct through RC making the output (C) go

high, all the other inputs stay low (DBA), so

the output is 0100 (decimal 4).

This principle will be employed in

INS (Inertial Navigation Systems),

IRS (Inertial Reference Systems) and

FMS (Flight Management Systems) as all these have

keyboards.

So some form of encoding will convert the

input signals into the correct code for the

system.

In Flight Data recording some of the inputs

into the system are in analogue form, such as

dc, ac or syncro signals.

This means that they have to be encoded into

digital for use by the Central Processing Unit

(CPU).

This is done by an Analogue to Digital

Converter.

The diagram below shows the basic layout of

a digital ramp A to D converter

DAC

When the start pulse is applied, it becomes

logic 1, the counter is reset, no pulses are fed

through the AND gate as it is 'closed'.

A comparator is a device with two inputs

which compare the voltages at each input to

determine which is greater, the output is

logic 1 if A is larger than B and logic 0 if

input B is larger than A.

On start B is 0, A is the larger output, from

the comparator is logic state l and when the

START pulse goes low the AND gate 'opens'

and the clock pulses go to the counter. Each

pulse causes the counter to advance.

As the counter counts up, its value is

converted into its analogue equivalent by the

digital to analogue convertor (DAC or D to A

or D/A) and applied to the comparator at B.

The DAC output therefore increases in steps

until it reaches just above the analogue input

level ie, B input >A.

The comparator output goes low, AND gate

closes, the count stop, the digital read-out is

then taken from the counter.

The best approximation we can obtain,

depends on how much input B has to be

greater than A ie, the step size, this is known

as the quantization error.

This type of Analogue to Digital converter is

slow in operation and is unsuitable for high

speed operation, and of course the larger the

voltage the longer (more steps) time it takes.

The comparator would be an operational

amplifier.

This problem can be partly overcome by using an

up/down counter.

It counts up when the comparator is logic 1 and

down when the comparator output is logic 0.

As the analogue input varies it simply counts up

or down from the previous count rather than re-

setting to zero as did the digital ramp convertor.

This type is called the continuous digital-ramp

convertor and is a considerable improvement on

the previous one.

However, the fastest type of ADC of the ones

considered is the successive approximation type ADC.

This is similar to the previous circuit but the register

is used instead of a counter and a control logic block

is included between the comparator and register,

which controls the output of the register.

A TO D

Initially a reset signal puts all bits in the

register to 0.

The control logic sets the MSB in the register

to 1 and the rest to logic 0.

The output of the DAC is then compared to

the analogue input if B > A then this number

is too large and the MSB remains at 1.

At the next clock pulse the control changes

the next bit in the register, if B>A, it is set to

0, if B<A, it is set to 1 and so on until all the

bit values are found.

The digital read out can then be read.

This has a fast conversion time which does

not depend on the analogue voltage level but

just the number of bits in the convertor.

A decoder is a device which is usually at the

output end of a system and converts the

binary to decimal ie, changes the operational

working code into the code necessary to

operate the output system.

Some examples of this are where BCD is

converted into a code necessary to operate a

seven segment display

The next drawing shows a binary weighted

resistor method, so called as the values of the

resistors increase in accordance with the

binary system eg, R, 2R, 4R, 8R.

The output from the resistor chain is

connected to an operational amplifier as a

summing amplifier with a feedback resistor Rf

The output Vo is therefore

Also in the circuit there are four switches S1,

S2, S3, S4 which are electronic switches

(digitally controlled).

Each switch connects the resistor to a fixed

reference Vref when the input bit is logic 1

(+5v) and to ground (0v) when the input bit is

logic 0

Assuming that Rf= R = 1K then the output

formula becomes

If the input number is 0001then:

ie each of the electronic switches connecting

the input to ground.

V4 will be connected to Vref, we will assume

that Vref is - 8v so the formula becomes:

With an input of 0100 V1 = V3= V4=0

V2= Vref. Assume again Vref= -8v

The accuracy of this system depends on the

resistors and the precision of the input

supply.

Resistors can be made to reasonable accuracy

and the electronic switches can be replaced

by precision level amplifiers, these ensure

their outputs are exactly 5v or 0v depending

upon their outputs.

High input ensures 5v from the amplifier to

the input resistor of the op amp (operational

amplifier) and a low output ensures 0v

Another problem is the larger the bit word

the more the range of resistors is required ie,

for every extra bit the range of the required

resistors doubles.

So another method of converting digital to

analogue must be found for digital words

with a large number of bits it is called the

R - 2R type.

The circuit works on the principle that pair of

2R resistors at the end of the ladder can be

considered in parallel, forming an overall

resistance R.

This system does use twice the number of

resistors compared to the binary weighted

network, but the use of only two values of

resistors means the system can handle any

number of input bits, simply be extending the

resistor ladder.

You might also like

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Origins of Aerial HijackingDocument5 pagesThe Origins of Aerial HijackingPrabath De SilvaNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- JH Wascator FlyerDocument1 pageJH Wascator FlyerPrabath De SilvaNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- DS - In0002 - GB - 1372. en 837 PDFDocument4 pagesDS - In0002 - GB - 1372. en 837 PDFAldrin HernandezNo ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Manometros WikaDocument20 pagesManometros WikaDavid VargasNo ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Surface Sensor SDocument8 pagesSurface Sensor SPrabath De SilvaNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- EntebeDocument20 pagesEntebePrabath De SilvaNo ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- 3501e JDocument18 pages3501e JPartsGopher.comNo ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- MSL Technical Guide 25 Calibrating Balances: Ing and Calibration Laboratories by International AccrediDocument7 pagesMSL Technical Guide 25 Calibrating Balances: Ing and Calibration Laboratories by International AccrediPrabath De SilvaNo ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Good Practice GuideDocument14 pagesGood Practice GuidePrabath De SilvaNo ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- CalibrateDocument33 pagesCalibrateazurananNo ratings yet

- MSL Technical Guide 11 Thermometer Immersion and Dry-Block CalibratorsDocument3 pagesMSL Technical Guide 11 Thermometer Immersion and Dry-Block CalibratorsPrabath De SilvaNo ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Calibration ProceduresDocument24 pagesCalibration Procedurestingpadu83% (6)

- 258 - VeriVide Product Guide June09Document16 pages258 - VeriVide Product Guide June09Prabath De Silva0% (1)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Back Side of ChinaDocument30 pagesBack Side of ChinaPrabath De SilvaNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Failure TerminologiesDocument24 pagesFailure TerminologiesPrabath De SilvaNo ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Corporate Social ResponsibilityDocument17 pagesCorporate Social ResponsibilityPrabath De SilvaNo ratings yet

- Introducing Microsoft Project 2007Document226 pagesIntroducing Microsoft Project 2007Prof. Dr. Abdalla ElDaoushyNo ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Material Properties 1Document39 pagesMaterial Properties 1Prabath De SilvaNo ratings yet

- Nursing Division BudgetingDocument5 pagesNursing Division BudgetingPrabath De SilvaNo ratings yet

- Chinese Lunar CalendarDocument1 pageChinese Lunar CalendarPrabath De SilvaNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Material Properties 2Document28 pagesMaterial Properties 2Prabath De SilvaNo ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Elementry Stresses & Stress Concentration 36 TIDocument39 pagesElementry Stresses & Stress Concentration 36 TIPrabath De SilvaNo ratings yet

- In The Name of The Most Gracious, The Most Merciful: AllahDocument27 pagesIn The Name of The Most Gracious, The Most Merciful: AllahPrabath De SilvaNo ratings yet

- Basic Concept of QualityDocument18 pagesBasic Concept of QualityPrabath De SilvaNo ratings yet

- Battery ManualDocument76 pagesBattery ManualPrabath De Silva0% (1)

- Aircraft Corrosion For Off & Tech July 2010Document49 pagesAircraft Corrosion For Off & Tech July 2010Prabath De Silva100% (1)

- Metrology Lab Manual DimensionDocument30 pagesMetrology Lab Manual DimensionPrabath De SilvaNo ratings yet

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Elementry Stresses & Stress Concentration 36 TIDocument39 pagesElementry Stresses & Stress Concentration 36 TIPrabath De SilvaNo ratings yet

- A Guide To Effective Human Resources ManagementDocument39 pagesA Guide To Effective Human Resources ManagementPrabath De SilvaNo ratings yet

- Features: Buck-Boost Narrow VDC Battery Charger With Smbus Interface and Usb OtgDocument45 pagesFeatures: Buck-Boost Narrow VDC Battery Charger With Smbus Interface and Usb OtgMobile HackNo ratings yet

- tps54426 PDFDocument29 pagestps54426 PDFAldo LeivahNo ratings yet

- A 2GS/s 9-Bit 8-12x Time-Interleaved Pipeline-SAR ADC For A PMCW Radar in 28nm CMOSDocument4 pagesA 2GS/s 9-Bit 8-12x Time-Interleaved Pipeline-SAR ADC For A PMCW Radar in 28nm CMOSburakgonenNo ratings yet

- Electronic ComparatorsDocument20 pagesElectronic ComparatorsKumarChirraNo ratings yet

- A 53-nW 9.1-ENOB 1-kS/s SAR ADC in 0.13-m CMOS For Medical Implant DevicesDocument9 pagesA 53-nW 9.1-ENOB 1-kS/s SAR ADC in 0.13-m CMOS For Medical Implant DevicesAshish JoshiNo ratings yet

- LM 733Document11 pagesLM 733Bharavi K SNo ratings yet

- Ade Lab ManualDocument84 pagesAde Lab ManualRuthwik S GowdaNo ratings yet

- 3842 Ic DatasheetDocument13 pages3842 Ic DatasheetEngr Khalid IqbalNo ratings yet

- Fan 7530Document20 pagesFan 7530aldo_suviNo ratings yet

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- A Car Parking Guard Circuit Using Infrared SensorDocument9 pagesA Car Parking Guard Circuit Using Infrared Sensorhamed razaNo ratings yet

- Electronic Circuit Design and Analysis For Space ApplicationsDocument8 pagesElectronic Circuit Design and Analysis For Space ApplicationsH SMNo ratings yet

- 555 TimerDocument3 pages555 TimerPraveen KumarNo ratings yet

- LM3401 Hysteretic PFET Controller For High Power LED Drive: Literature Number: SNVS516BDocument20 pagesLM3401 Hysteretic PFET Controller For High Power LED Drive: Literature Number: SNVS516BVacunas AutismoNo ratings yet

- Smart HelmetDocument71 pagesSmart HelmetTejaswini Nimmagadda100% (2)

- Design of Area Efficient Low Power Ever Mixed LogiDocument10 pagesDesign of Area Efficient Low Power Ever Mixed LogiAnneNo ratings yet

- LED Based Snake PDFDocument6 pagesLED Based Snake PDFSalma SaleemNo ratings yet

- Jumo ControladoresDocument14 pagesJumo ControladoresKamillAL-akhrasNo ratings yet

- Ultra Fast Acting Electronic Circuit BreakerDocument6 pagesUltra Fast Acting Electronic Circuit BreakerHarish Kumar100% (1)

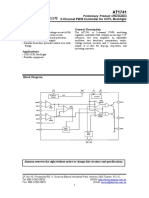

- 2-Channel PWM Controller For CCFL Backlight: Preliminary Product InformationDocument11 pages2-Channel PWM Controller For CCFL Backlight: Preliminary Product InformationMorales Avila NiorgeNo ratings yet

- PIC18F4550Document430 pagesPIC18F4550Leonardo Saldaña CabreraNo ratings yet

- Amplificador Irs2092 PDFDocument42 pagesAmplificador Irs2092 PDFTiago MizaelNo ratings yet

- Service Manual Pulse Oximeter Model 515Document138 pagesService Manual Pulse Oximeter Model 515Mojtaba TorkiNo ratings yet

- Tabla de Compuertas CMOSDocument2 pagesTabla de Compuertas CMOSPaola LorenzattoNo ratings yet

- Circuito Integrado para Control de DisplayDocument17 pagesCircuito Integrado para Control de DisplayGabriel ZorattiNo ratings yet

- Adc Multisim Based Lab Manual UpdatedDocument56 pagesAdc Multisim Based Lab Manual UpdatedPavan Sai100% (1)

- Digital TachometerDocument12 pagesDigital TachometerHariniNo ratings yet

- MP3398A - r1.05 Driver Les Board Flaco BellohorizonteDocument20 pagesMP3398A - r1.05 Driver Les Board Flaco BellohorizonteAndres AlegriaNo ratings yet

- Digital ElectronicsDocument386 pagesDigital ElectronicsVia Marie MesaNo ratings yet

- DM311Document16 pagesDM311Hernan Ortiz EnamoradoNo ratings yet