Professional Documents

Culture Documents

Intro PSoC5.0

Uploaded by

Nagarjuna SeelamneniCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Intro PSoC5.0

Uploaded by

Nagarjuna SeelamneniCopyright:

Available Formats

PSoC Designer

Module 1:

Introduction to PSoC

2

Module Outline

Section 1: Introduction to PSoC

Section 2: PSoC Designer IDE Software

Section 3: Hands-On Example Project

PSoC

An Introduction

4

What is a PSoC Mixed Signal Device?

PSoC combines:

the familiarity of a microcontroller

the configurability of an CPLD

the capabilities of an Mixed

Signal Array

P rogrammable

S ystem

o n

C hip

5

What is PSoC?

PSoC

Devices

Features:

Configurable Analog Blocks

Implement ADCs, DACs, filters, amplifiers, comparators, etc.

Configurable Digital Blocks

Implement timers, counters, PWMs, UART, SPI, IrDA, etc.

4KB to 32KB of Flash memory for program storage

256B to 2KB of SRAM for data storage

M8C Microcontroller: 4 Million Instructions Per Sec

6

What is PSoC?

Inputs

Each pin can sink 25mA

Programmable filters

Flexible sensor interface I/O

3 types of ADCs, up to 4

Processing

Fast M8 Microcontroller Core

Multiply Accumulate

Outputs

Each pin can source 10mA

Up to 16 PWMs, Timers, Counters

Up to 9-bit DACs, 14-bit ADCs

Support Functions

EEPROM

Sleep Options

Watch Dog Timer

Low voltage detect

7

1

6

k

F

l

a

s

h

POR

SROM

M8 CPU

BandGap

RAM

PUMP

MAC

PLL/Osc 32K Osc

Dec.

GPIO

CY8C27XXX PSoC 1208

PSoC Die

8

PSoC Architecture

Interrupt

Controller

LVD

Supervisor

Watchdog

Sleep Timer

Decimator

SMP

I

2

C

SRAM

Memory

(up to 2K)

M8C

CPU

Core

MAC Multiply

Accumulate (up to 2)

Flash

Program

Memory

(up to

32K)

System

Clocking

Generator

24 MHz

Internal

Oscillator

Digital PSoC Block Array

Analog PSoC Block Array

Programmable

Interconnect

and Logic

Analog Input

Muxing

Analog Output

Drivers

Port 5

Port 4

Port 3

Port 2

Port 1

Port 0

C

o

n

f

i

g

u

r

a

b

l

e

I

/

O

P

o

r

t

s

S

y

s

t

e

m

B

u

s

BB

BB

BB

BB

CB

CB CB

CB

CT CT CT CT

SC

SC

SC SC

SC SC

SC

SC

Clocks

BB BB CB CB

BB BB CB CB

Port 6

Port 7

UART

PWM_16

Filter

A

D

C

ADC

(Decimator)

ADC

I2C

Slave, Master,

Multimaster

LCD

9

Analog Functions (Subset)

ADC

Incremental 6-14 bits

Delta Sigma 6-13 bits

DAC

6, 8, and 9 bit

6 and 8 bit multiplying

Filters

2-pole Low-pass

2-pole Band-pass

DTMF Dialer

Modulator

Peak Detector

V to I Converter

Amplifiers

Programmable Gain

Instrumental

Inverting

Comparators

Programmable

Hysteresis

Zero-Crossing

CapSense

10

Digital Functions (subset)

Timer

8, 16, 24, 32 bit

Counter

8, 16, 24, 32 bit

PWM

8, 16, 24, 32 bit

Dead Band Generator

8, 16, 24, 32 bit

Pseudo Random Source

Cyclic Redundancy Check

Communication Interface

I2C Master

I2C Slave

SPI Master

SPI Slave

Full Duplex UART

Tx, Rx

Full Speed USB v2.0

11

Define connections

between pins and

function blocks

Define connections

between function

blocks

Define clock paths

Change

connections

dynamically too!

Interconnection Scheme

12

User Modules

Pre-configured and Pre-characterized Digital

and Analog PSoC Blocks

Greatly simplifies and shortens coding process

Analogous to On-chip Peripherals

ADCs, DACs, PGAs, Filters

Timers, Counters, PWMs

UART, SPI, I2C

Defines the Register Bits for Initial Configuration

Selected via Double Click in IDE

User Modules Include

Application Programmer Interfaces (APIs)

Interrupt Service Routines (ISRs)

Specific UM Data Sheets

13

Additional Features

Comprehensive Design Tools

Intuitive Resource Placement

Easy Routing

Powerful Logic

Dynamic Reconfiguration

14

PSoC Design Tools

Free Design Software

Device Editor

Application Editor

C Compiler

Assembler

Librarian

Debugger

Low Cost ICE

CY3215-DK

Trace, Dynamic Event Point

Every thing you need for

PSoC development

Graphical Application

Design Software

No MCU Coding!

15

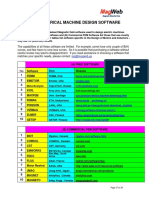

PSoC Designer 5.0

A New Paradigm in Embedded Design

An integration of PSoC software

PSoC Express - a visual embedded code free design environment

PSoC Designer 4.4 - a powerful and more traditional IDE

MS Visual Studio based GUIdock, tab, and float windows

Upgraded Debugger; new Run-to-Cursor breakpoint features

EASY-TO-USE, FAST, FLEXIBLE

16

PSoC Designer 5.0

System-Level View (Formerly PSoC Express)

17

PSoC Designer 5.0

Chip-Level View (Formerly PSoC Designer 4.4)

18

PSoC Designer 5.0

System-Level to Chip-Level Transitions

1

2

3

4

Design & Build

Open Chip-View

Optimize the Design

Customize the Code

19

PSoC Programmer 3.xx

Customize & Enhance your PSoC Programming Experience

Customizable GUImaximize & minimize what you want to see

COM object architectureopen access to programmer functionality

Automatic PSoC Programmable System on Chip Detection

Accelerated prototypingturn timely verification on/off as needed

Huge array of GUI enhancementscleaner, easier to use interface

Classic View

Modern View

Simple View

20

PSoC Programmer 3.xx

Classic View

21

PSoC Programmer 3.xx

Modern View

22

PSoC Programmer 3.xx

Simple View

Section 2: PSoC

Designer IDE

Software

24

3) Press Place User Module Button

1) Drag Green Target Placer from

default location

Intuitive Placement

2) Drag to desired location

(Target Placer box fills in green when place-able)

25

Easy GUI Routing

26

Powerful Combinational Logic

27

Powerful Combinational Logic

28

Dynamic Reconfiguration

More than meets the eye: Multiple Configurations

29

Integrated Development Environment

Device Editor

Application Editor

C Compiler

Assembler

Librarian

Debugger

30

PSoC Designer

Device Editor Interconnect View

Placing User Modules

View block architecture with

combined UM & port views

Generates routed block to

block schematic

Routed global I/O connection

schematic

Step through potential UM

placement options

Select desired placement

option for UM

Select UM and resource

interconnections

Select/configure UM and

global device resources

Define clocking for UMs

Configure mode and drive

level for GPIO pins

Global

resources table

User module

parameter table

Port table

UM

Workspace

User Module

window

31

For Users to Write Code

For Users to Assemble/Compile Code

* The C compiler needs to be enabled for use.

View and edit individual

source files

Set and remove

bookmarks (Editing tool)

Assemble/compile

individual files

Build entire project

including

assemble/compile* all

files in project

Source line error pointer

PSoC Designer Application Editor

32

PSoC Designer C Compiler

The C compiler by Hi Tech is an optional component of the

PSoC Designer IDE. Once enabled, it is fully integrated

into the IDE and allows PSoC Designer to support C

source level debugging.

Features Include:

ANSI C Compiler

Supports Inline Assembly and can interface with Assembly

Modules

Integrated code compressor

Modern Stack-Based Architecture

7 Basic Data Types Including IEEE 32-Bit Floating Point

Assembler and Linker

Math and String Libraries

C Interrupt Service Routines

Librarian

For more info on the C compiler, please see the C language compiler user guide in the

documentation folder of PSoC Designer.

33

Interface to ICE

View contents of Register

and Memory spaces

Change the contents of the

register banks and the RAM

Run/Halt /Single Step

Set breakpoints and event

points

Capture trace

PSoC Designer Debugger

Note: We will not be using the DeBugger during this workshop

PSoC Hands On

Example Project

35

PSoC Design Flow

Determine system requirements

Choose User Modules

Place User Modules

Set global and User Module parameters

Define the pin-out for the device

Generate the application

Review generated code

Demonstrate working configuration

36

Project Requirements

Blink two LEDs at approximately 2Hz, with duty

cycle of 40% and 20%

Implementation:

Create An MCU with Two Pulse Width Modulators:

Select Two PWM User Modules

Set the PWM parameters

Initialize the global clocks

Connect the PWM outputs to the PSoC Pup LEDs

37

Project Implementation

16 16

16-bit

PWM

65535

16-bit

PWM

65535

24MHz

VC1 VC2

(1.5MHz)

(94kHz)

P2[0]

P2[1]

(1.4Hz)

(1.4Hz)

PSoC

Pup

38

Starting a New Project

Open PSoC Designer

Select Start new

project

39

Starting a New Project

Select

Project Type

Name The

Project

40

Starting a New Project

Select Device and

Coding Method

CY8C29466-24PXI

C

OK

41

Select and Place User Modules

Select the PWM16 from

the User Modules page

Place User Modules for this Project

How do I know where to place the User

Modules?

How does PSoC Designer help me?

42

Place User Modules

Try-out the modules individually first

See how restrictive they are, then return to original location

PSoC Designer will only allow the modules to be placed where

the chip can support them

PSoC Designer will not prevent a placement that may create a

conflict for resources

Example: If you have an ADC and temperature sensor, they both

use the comparator bus. There is only one comparator bus per

column, therefore these two UMs must reside in separate

columns in order to be used simultaneously.

Read the UM Data Sheets for details

Use the Cypress Online Resources

www.cypress.com/support

43

Place User Modules

Place the two selected User Modules. Double Click on

PWM16 wait a few moments until the user module is

placed in the Interconnect Window - repeat

PWM16_1 Digital Blocks DBB00/DBB01

PWM16_2 Digital Blocks DBB10/DBB11

Recommend placing the PWMs in the Basic Digital Blocks to

Save the Digital Communication Blocks

44

Place User Modules

When you are done the screen should look like this

45

Configure Global Resources

Power Setting: 5.0V/24MHz

CPU_Clock: SysCLK/2 (12MHz)

32K_Select: Internal

Not using an external crystal

PLL_MODE: Disable

PLL can only be enabled when

32K_Select is External (crystal)

Sleep_Timer: 512_Hz. (Default)

VC1 = SysClk/N: Set to 16

This divides 24MHz by 16 =

1.5MHz

VC2 = VC1/N: Set to 16

This divides the 24V1 by 16

(1.5MHz/16=94kHz)

VC3 Source: SysClk/1

VC3 Divider: 1

46

Configure Global Resources

SysClk Source: Internal

SysClk*2 Disable: YES

Analog Power: SC On/Ref Low

This is required to power up any of the analog blocks,

depending on the number of analog functions. A Ref Med or

Ref High may be required (and will increase power

consumption)

Ref MUX: (V

dd

/2) Bandgap (default)

AGndBypass: Disabled

47

Configure Global Resources

Op-Amp Bias: Low (default)

This is not recommended as anything but low

A_Buff_Power: Low (default)

Adequate for most projects

This selects the power level of the analog output buffer

There is a tradeoff between drive output

power and power consumption.

SwitchModePump: OFF

Trip Voltage [LVD (SMP)]: 4.64V (5.0V)

48

Configure User Modules

PWM16_1: We want to generate a 1/5 duty cycle

User module parameters can be configured in two ways: through

the GUI or through the User Module Parameters window. In this

class we will use the User Module Parameters window in the left

bottom corner.

Set Clock to VC2 (94kHz)

Set Enable High to keep the PWM always running

Set CompareOut to Row_0_Output_0

Set TerminalCountOut to None

Set Period to 65535 (1.4Hz)

Set PulseWidth to 13107

Compare Type Less Then Or Equal

Interrupt Type Terminal Count

ClockSync to Sync to SysClk

InvertEnable set to Normal

49

Configure User Modules

PWM16_2: We want to generate a 2/5 duty cycle

Set Clock to VC2 (94kHz)

Set Enable High to keep the PWM always running

Set CompareOut to Row_1_Output_1

Set TerminaCountOut to None

Set Period to 65535 (1.4Hz)

Set PulseWidth to 26214

Compare Type Less Then Or Equal

Interrupt Type Terminal Count

ClockSync to Sync to SysClk

InvertEnable set to Normal

50

Interconnect Blocks to Resources

What interconnection possibilities are there?

Data Inputs

Data Outputs

Clocks

Block-to-block

When you specify a PSoC block connection to a

pin you are making a physical connection to the

hardware of the PSoC device.

51

Define the Pin-out

What pins need to be defined?

UM Inputs

UM Outputs

General Purpose IO

What happens as pins are defined?

Pin-out our project

LEDs

52

Interconnect Blocks to Resources

Route PWM16_1 to pin:

Connect PWM16_1 output to Row_0_Output_0

Connect Row_0_Output_0 to GlobalOutEven_0

Left Click

Left Click

53

Interconnect Blocks to Resources

Route PWM16_1 output to pin

Port 2 is connected to the LEDs on the Pup board

54

Interconnect Blocks Resources

Route PWM16_2 output to pin

55

Interconnect Blocks Resources

Route PWM16_2 output to pin

56

Configuration Complete!

Save project Go to File tab

Now what? Where are we?

Time to Generate Application

All settings used by PSoC Designer

to create the boot-up code to configure

the registers at reset

ISRs are created (but not updated)

APIs are created or updated

Device Data Sheet generated

You must Generate Application whenever changes are made

to the configuration

Now switch to the Application Editor view

57

Time to Create Application Code

PSoC Designer generates application code

based on the configurations you just

defined in the Device Editor.

Project File Tree, located to the left of the

application window, contains:

all interrupt routines

header files

include files

configuration tables

All APIs and ISRs can be modified by the

user.

58

Create Application Code

Open the main.c file

Type the PWM start commands for each PWM_1 and PWM_2

void main()

{

// Insert your main routine code here.

PWM16_1_Start () ;

PWM16_2_Start () ;

while (1);

}

59

Create Application Code

60

Build Project

Assembles code, links, and locates

Can individually assemble files as well

Explore Application Editor Features

Project file management (view/add/delete files)

Finding compilation errors

61

Program The Device

62

Program The Device

Select MINIProg in the

port window

Select Connect

Select Program

When Programming

is complete Toggle

Device Power

Congratulations, you

have just completed

your first PSoC

design!

63

Appendix

64

Bi-Directional Current Source

DiffAmp configured with gain of one.

C

F

=C

B

=C

A

=16

Sign = Pos

External Resistor and DAC value sets

current.

Independent of load.

SCBlock Amplifier Examples

DAC6

DiffAmp

Buf0

P0.3

P2.1

V

load

V

set

V

out

R

set

+A

-B

i = -V

set

/ R

set

R

load

x1

set load out

V V V =

set

set

set

load out

R

V

R

V V

i =

=

65

SCBlock Filters FilterCalc

Enter Following Parameters

Rolloff Frequency (f

0

)

Acceptable Tolerance

Damping Value

Acceptable Tolerance

Column Clock (f

s

*4)

FilterCalc generates all Capacitor values

that meet these requirements.

Output file readable with Excel.

43 different solutions for this particular

example.

66

SCBlock Low Pass Filter

Programmable

Roll off frequency (f

0

)

Damping ratio

Gain

300 Hz to 250 kHz

Scaled to clock

|

2

|

2

|

2

|

2

|

2

|

2

|

1

|

1

|

1

|

1

V

in

V

out

C

1

C

3

C

4

C

B

C

2

C

A

|

1

1

2

1

4

1

2

1

2

4

2

4

3 2

2

2

2

1

+ +

|

|

.

|

\

|

|

|

.

|

\

|

|

|

.

|

\

|

=

s s

B A

s

S

in

out

C

C

f

s

C

C

C C

C C

f

s

f

s

C

C

V

V

67

Two Cap Comparator

With feedback capacitor C

F

removed V

out

goes to either

the high or low rail.

V

out

goes high when

V

inA

C

A

> V

inB

C

B

V

out

goes low when

V

inA

C

A

< V

inB

C

B

V

inB

is the inverting input

input.

SCBlock as Comparator

|1

|2

C

A

|1

|1 |2

V

inA

V

out

C

B

V

inB

68

SCBlock Integrator

Uses standard gain stage with the

exception that the switch to

discharge C

F

has been disabled.

So:

SCBlock as Integrator

|1

|2

C

A

C

F

|1

|2

V

in

V

out

F

A

in out out

C

C

V V V

old

+ =

s C

C

f

V

V

F

A

s

in

out

1

|

|

.

|

\

|

=

1 2 = f s t

69

Dual Input SC Integrator

Feedback makes low pass filter

with gain.

Ratio of C

A

& C

B

determines

gain.

C

F

,C

B

, and f

s

determines rolloff

frequency.

Setting V

in

to V

ref

makes filter DAC.

Much higher f

s

than Conventional

DAC

SCBlock as Integrator

Single Pole LPF

|

|

.

|

\

|

+

|

|

.

|

\

|

=

2

1

1

1

B

F

s

B

A

in

out

C

C

f

s

C

C

V

V

|1

|2

C

A

C

F

|1

|2

V

in

V

out

|1

|2

C

B

buf

70

Dual Input SC Integrator

External Emitter follower

makes a high power output

driver.

Able to drive all the way to V

ss

rail

SCBlock as Integrator

Power Driver

|1

|2

C

A

C

F

|1

|2

V

in

V

out

|1

|2

C

B

buf

R

load

V

cc

71

Dual Input SC Integrator

Or a 4 Ohm Class B Speaker

Driver.

4 Ohm

|1

|2

C

A

C

F

|1

|2

V

in

V

out

|1

|2

C

B

buf

V

cc

SCBlock as Integrator

Speaker Driver

72

SCBlock as 2 Pole Filter

Two Pole Filters

Constructed with a BiQuad Circuit Topology

Continuous Time Implementation shown below

Requires Three Op Amps

Middle one only used to change polarity

V

in

V

out

R

2

R

1

C

4

C

B

R

3

C

A

R

R

C

PP

C

P

1

1

4 2 3 2

2

1 3 1

2

1

2

+ +

+ +

=

C sR C C R R s

C sR C C R R s

R

R

V

V

B A

p pp A

in

out

73

SCBlocks as 2 Pole Filter

Two Pole Filters

Switched Capacitor Implementation

Requires Only Two Op Amps

1

4

1

2

1

4

1

2

1

2

4

2

4

3 2

2

2

2

1

2 2 3 2

2

2

+

|

|

.

|

\

|

+

|

|

.

|

\

|

+

|

|

.

|

\

|

+

|

|

.

|

\

|

=

C

C

f

s

C

C

C C

C C

f

s

C

C

C

C

f

s

C

C

C C

C C

f

s

V

V

s

B A

s

p

s

p pp A

s

in

out

|

2

|

2

|

2

|

2

|

2

|

2

|

1

|

1

|

1

|

1

V

in

V

out

C

1

C

3

C

4

C

B

C

2

C

A

|

1

C

PP

C

P

High Pass

Band Pass

Low Pass

74

SCBlock Band Pass Filter

|

2

|

2

|

2

|

2

|

2

|

1

|

1

|

1

|

1

V

in

V

out

C

1

C

3

C

4

C

B

C

2

C

A

|

1

AnalogBus

CompBus

Programmable

Center frequency (f

c

)

Q

Gain

300 Hz to 250 kHz

Scaled to clock

1

2

1

4

1

2

1

2

4

2

4

3 2

2

3

2

1

+ +

|

|

.

|

\

|

|

|

.

|

\

|

+

=

C

C

f

s

C

C

C C

C C

f

s

f

s

C

C

f

s

C

C

V

V

s

B A

s

S

B

s

in

out

75

Elliptical Low Pass Filter

Combines High Pass

and Low Pass Filters

Produces two zeros.

Low pass filter when:

|

2

|

2

|

2

|

2

|

2

|

2

|

1

|

1

|

1

|

1

V

in

V

out

C

1

C

3

C

4

C

B

C

2

C

A

|

1

C

PP

1

2

1

4

1

4

1

1

2

4

2

4

3 2

2

3 1

2

2

1

+ +

|

|

.

|

\

|

|

|

.

|

\

|

|

|

.

|

\

|

|

|

.

|

\

|

+

=

C

C

f

s

C

C

C C

C C

f

s

C C

C C

f

s

C

C

V

V

s

B A

s

A PP

s

in

out

highpass lowpass

f f

0 0

<

76

SCBlock Notch Filter

Special Case of

Elliptical Low Pass

Filter where:

|

2

|

2

|

2

|

2

|

2

|

2

|

1

|

1

|

1

|

1

V

in

V

out

C1

C3

C4

CB

C2

CA

|

1

CPP

1

2

1

4

1

4

1

1

2

4

2

4

3 2

2

3 1

2

2

1

+ +

|

|

.

|

\

|

|

|

.

|

\

|

|

|

.

|

\

|

|

|

.

|

\

|

+

=

C

C

f

s

C

C

C C

C C

f

s

C C

C C

f

s

C

C

V

V

s

B A

s

A PP

s

in

out

highpass lowpass

f f

0 0

=

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Misubishi M720BM HandbookDocument366 pagesMisubishi M720BM HandbookNam Ngô PhươngNo ratings yet

- Darktrace Tech AppliancesDocument2 pagesDarktrace Tech AppliancesnoneNo ratings yet

- Coupled Mode Theory of WaveguidesDocument18 pagesCoupled Mode Theory of WaveguidesKartikay5No ratings yet

- PA0FBK Antenna DemystifiedDocument25 pagesPA0FBK Antenna DemystifiedEnero A. SaisNo ratings yet

- Wingspan ManualDocument9 pagesWingspan ManualalirioNo ratings yet

- DIAL's RequirementsDocument57 pagesDIAL's RequirementsShaikh Saeed AlamNo ratings yet

- USB 3.1 Specification Language Usage Guidelines From USB-IFDocument2 pagesUSB 3.1 Specification Language Usage Guidelines From USB-IFsorin-it100% (1)

- Spartan-6 LX9 MicroBoard Embedded Tutorial 1Document15 pagesSpartan-6 LX9 MicroBoard Embedded Tutorial 1Đinh LuậnNo ratings yet

- Time and Current Grading For Protection Relay Type MK1000 & MK2000 - Mohamad Naim Mohamad - TK2821.M63 2008Document27 pagesTime and Current Grading For Protection Relay Type MK1000 & MK2000 - Mohamad Naim Mohamad - TK2821.M63 2008wcchang8100% (1)

- Energizer Cr1220: Product DatasheetDocument1 pageEnergizer Cr1220: Product DatasheetZARCO_MX77No ratings yet

- Railway Bridge Monitoring During Construction and Sliding: IMAC - Stress Analysis LaboratoryDocument7 pagesRailway Bridge Monitoring During Construction and Sliding: IMAC - Stress Analysis LaboratoryMariusHazaparuNo ratings yet

- AppleDocument22 pagesApplePhuong Nhung100% (1)

- 15KW-18.5KW InverterDocument1 page15KW-18.5KW InverterMAROC INVESTISSEMENTNo ratings yet

- Problem Set 4 - EE19Document2 pagesProblem Set 4 - EE19Mark Anthony GarciaNo ratings yet

- AVIC-Z830DAB Quickstart Manual SVDocument16 pagesAVIC-Z830DAB Quickstart Manual SVYlle UntNo ratings yet

- Generator Protection Module GPM 500: Operation and Service ManualDocument108 pagesGenerator Protection Module GPM 500: Operation and Service ManualБогдан КендзерNo ratings yet

- Electric Products: Contactors / MPCB / MCCB / ACBDocument29 pagesElectric Products: Contactors / MPCB / MCCB / ACBZAHEER ABBASNo ratings yet

- DP LAN Others 13115 DriversDocument2,284 pagesDP LAN Others 13115 DriversSyed AliNo ratings yet

- An0046 Efm32 Usb Hardware Design GuidelinesDocument21 pagesAn0046 Efm32 Usb Hardware Design GuidelinesMohammad HBNo ratings yet

- Matlab DSPDocument0 pagesMatlab DSPNaim Maktumbi NesaragiNo ratings yet

- Datos D Emotor DC WGMDocument1 pageDatos D Emotor DC WGMjosue perezNo ratings yet

- Opamp 24Document111 pagesOpamp 24api-3750190No ratings yet

- CP4014 0 1Document3 pagesCP4014 0 1Jou PowerNo ratings yet

- Phy Ip For Pcie 3.0Document2 pagesPhy Ip For Pcie 3.0uparashar1No ratings yet

- Design Software 1Document2 pagesDesign Software 1anbarasuval84No ratings yet

- 727 Manual 1Document31 pages727 Manual 1Dadang Satyawan Padmanagara100% (2)

- Tuncuk Et Al., 2012 PDFDocument10 pagesTuncuk Et Al., 2012 PDFlaguna028No ratings yet

- 1977 Motorola M2900 TTL Processor Family 2edDocument70 pages1977 Motorola M2900 TTL Processor Family 2edLovely DilipNo ratings yet

- Complete Intro To Fire Detectors v2-1Document38 pagesComplete Intro To Fire Detectors v2-1Remus BobeNo ratings yet

- Datasheet Abb TrafoDocument3 pagesDatasheet Abb TrafoFernando Arnulfo G.No ratings yet