Professional Documents

Culture Documents

DFT Protocol

Uploaded by

noor_dcetOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DFT Protocol

Uploaded by

noor_dcetCopyright:

Available Formats

1 3-

Agenda

2006 Synopsys, Inc. All Rights Reserved Synopsys 30-I-011-SSG-009

Understanding Scan Testing

1

DFTC User Interfaces

2

DFT for Clocks and Resets

4

Creating Test Protocols

3

DAY

1

2 3-

Unit Objectives

After completing this unit, you should be able to:

List the 3 major steps in the Unmapped

DFT Flow

Create a test protocol and perform

RTL Test DRC

Name at least 3 elements of a test protocol

Identify the new graphical debugger utility for

XG mode.

3 3-

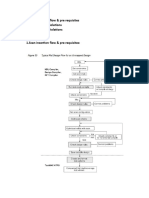

Step 2: Create Protocol and DFT Check

Test-Ready Compile

Read RTL Design

Create Test Protocol

Specify Scan Paths

Insert Scan Paths

Read Design and

Test Protocol

Handoff Design

Unmapped

DFT Flow

Violations?

DFT Check

Timing, Area

DFT Check

Preview

Coverage

End

Start

Mapped

DFT Flow

Violations?

Violations?

Constraints

Met?

4 3-

What is Unified Test DRC or UDRC?

The use of TetraMAX DRC engine within DFT

Compiler

Benefits:

Same Design Rule Checker from RTL through gates

Check for the same design rule violations between DFT

and ATPG tools

Same design rule violation messages between DFT and

ATPG tools

Enhanced debugging through GUI

5 3-

XG Mode Only Supports UDRC

One single command to perform DRC

Runs much quicker than prior check_test,

check_scan or check_dft

DFTC no longer infers a test protocol by default; a

test protocol must be in memory before DRC can

start:

DFTC no longer infers asynchronous set/reset signals by

default

DFTC no longer infers clock signals by default

Test protocol is now updated and available right

after insert_dft

6 3-

Define Resets, Clocks and Test Holds

pclk

prst_n

pci_rst_n

0

1

prst_ff pci_rst_n_buf

test_mode

PCI_RST

RESET_BLOCK

CLK

Q

CLK

Q

asynch

assertion

synchronous

deassertion

Synchronized

Reset Timing

0 15 30

pci_rst_n

# Declare test-clock waveforms

set_dft_signal -view existing_dft \

-type ScanClock \

-timing {45 55} -port pclk

set_dft_signal -view exist -type Reset \

-active_state 0 port prst_n

set_dft_signal -view e -type Constant \

-active_state 1 -port test_mode

. . .

Which pin(s) need to be held at

constant values to enable test mode?

Is Reset active-high or

active-low?

How many clocks

drive scan flip-flops

in test mode?

7 3-

Synchronous Resets are Not Part of Protocol

architecture Model of Moore_Machine is

signal Current_State, Next_State: std_logic_vector(3 downto 0);

begin

State_Elements:

process (Clock)

begin

if Clock'EVENT and Clock = '1' then

if Reset = 1 then

Current_State <= "0000";

else

Current_State <= Next_State;

end if;

end if;

end process;

8 3-

DFTC Script

or

Setup File

# SOC SCAN-TEST SETUP

# TetraMAX-Optimal Settings

# File: .synopsys_dc.setup

#

# Specify edge-set variables

set test_default_period 100

set test_default_delay 0

set test_default_bidir_delay 0

set test_default_strobe 40

# Declare test-clock waveforms

set_dft_signal -view exist -type ScanClock \

-timing {45 55} -port CLOCK

Specify default

ATE timing

DFTC

Variables

First Define Default Timing for All Pins

9 3-

Specify Clocks After Default Timing

# SOC SCAN-TEST SETUP

# TetraMAX-Optimal Settings

# File: .synopsys_dc.setup

#

# Specify edge-set variables

set test_default_period 100

set test_default_delay 0

set test_default_bidir_delay 0

set test_default_strobe 40

# Declare test-clock waveforms

set_dft_signal -view exist -type ScanClock \

-timing {45 55} -port CLOCK

Next define clocks and

rest of test protocol

Test Clock and

ATE Period

DFTC Script

or

Setup File

10 3-

Synopsys Test Tip

3.1 Package Timing Defaults

Test-clock definitions and timing defaults always work together. Think of

them as a timing package. This avoids inconsistencies like an active

test-clock edge occurring before a pre-clock strobe.

One way to package these specifications together is to put them all into

a setup script like the following:

# Company XYZ Setup Script

set test_default_period 100

. . .

set_dft_signal -view exist -type ScanClock \

-timing {60 40} -port CLK_RT1

11 3-

Specifying All Clocks and Resets is Best

# enable RTL source line tracking

set hdlin_enable_rtldrc_info true

# Step 1: Read RTL Design

read_verilog rtl/ORCA.v

current_design ORCA ; link

# Specify test clocks and other attributes

set_dft_signal -view exist -type ScanClock \

-timing {45 55} -port pclk

set_dft_signal -view exist -type Reset \

-active_state 0 port prst_n

set_dft_signal -view exist -type Constant \

-active_state 1 -port test_mode

# Step 2: Create the test protocol

create_test_protocol

# Run test design rule checking

dft_drc

# continue with rest of the flow

# Write out test protocol for later use

write_test_protocol o unmapped/ORCA.spf

# Step 3: Test-Ready Compile

set test_default_scan_style multiplexed_flip_flop

compile -scan

12 3-

Already Have a Test Protocol?

# Step 4: Read mapped design and test protocol

read_ddc mapped/ORCA.ddc

current_design ORCA ; link

# Clocks and test modes already in SPF

read_test_protocol unmapped/ORCA.spf

#define resets

set_dft_signal type Reset port resetn

# Run test design rule checking at the gate-level

dft_drc

# continue with rest of the flow

# ...

13 3-

Use Protocol Inference Only When No Choice

# Unfamiliar design!!

# Specify the clocks and resets

# that you do know...

set_dft_signal -view exist -type ScanClock \

-timing {45 55} -port clk1

set_dft_signal -view exist -type Reset \

-active_state 0 port rst1_n

set_dft_signal -view exist -type Constant \

-active_state 1 -port test_mode1

# ...and infer the remaining clocks and resets

# at the expense of additional runtime...

# and perhaps accuracy

create_test_protocol infer_clock infer_asynch

# run test design rule checking

dft_drc

# Iterate, if needed, in this discovery process

14 3-

Step 2: Create Protocol and DFT Check

Test-Ready Compile

Read RTL Design

Create Test Protocol

Specify Scan Paths

Insert Scan Paths

Read Design and

Test Protocol

Handoff Design

Unmapped

DFT Flow

Violations?

DFT Check

Timing, Area

DFT Check

Preview

Coverage

End

Start

Mapped

DFT Flow

Violations?

Violations?

Constraints

Met?

15 3-

Is Your Code DFT-Smart?

-----------------------------------------------

-- MULTIPLIER/CLIPPER CHIP

-----------------------------------------------

entity MULTICLIP is

. . .

end MULTICLIP;

architecture FUNCTIONAL of MULTICLIP is

signal CLIP_OUT:INTEGER range 0 to 50_000;

begin

ARITHMETIC:

process( MULT1,MULT2 )

variable PRE_CLIP:INTEGER range 0 to 65_025;

begin

PRE_CLIP:= MULT1 * MULT2;

if (PRE_CLIP < 50_000) then

CLIP_OUT <= PRE_CLIP;

CLIP_FLAG <= '0';

else

CLIP_OUT <= 50_000;

CLIP_FLAG <= '1';

end if;

end process ARITHMETIC;

. . .

Hidden

Testability

Problems?

Complex HDL

Architecture

16 3-

Test-Ready Compile

compile -scan

dft_drc

Define

Protocol

Set DC Variables

Read In HDL Code

(Re)code HDL

Analyze

Violations

Violations?

Checking the HDL Code

DFT Check

on RTL Code

An Optional Flow

D1

D3

D11

. . .

Common

Violations

Rest of Flow

17 3-

CLK

Q0

B0

B1

Ripple-Counter Violation

This kind of violation is caught as early as the coding phase

Enables DFT closure and reinforces your DFT guidelines

Flop cannot be

safely scanned.

D1: Uncontrollable

Clock Violation

Gate-Level

Representation

N 12

// Violating HDL Fragment

always @( posedge CLK )

Q0 <= D0;

always @( posedge Q0 )

Q1 <= D1;

18 3-

0

1

CLK

Q0

ASIC_TEST

D0

Ripple-Counter RTL DFT Solution

Another solution is to recode the HDL

to describe a synchronous counter.

Violation Corrected

in HDL Code

N 13

// Corrected HDL Fragment

always @( posedge CLK )

Q0 <= D0;

assign CLK_Q0 = ASIC_TEST ? CLK : Q0;

always @( posedge CLK_Q0 )

Q1 <= D1;

Flop now

scannable.

19 3-

dft_drc

Loading test protocol

Loading design 'RISC_CORE'

Pre-DFT DRC enabled

Information: Starting test design rule checking. (TEST-222)

...checking vector rules...

...checking pre-dft rules...

-----------------------------------------------------------------

Begin Pre-DFT violations...

Warning: Clock input clocked_on of DFF

I_ALU/Carry_Flag_reg(/RISC_CORE/ALU.vhd 40) was not controlled. (D1-1)

Information: There are 309 other cells with the same violation. (TEST-171)

Warning: Reset input clear of DFF

I_ALU/Carry_Flag_reg(/rtl/RISC_CORE/ALU.vhd 40) was not controlled. (D3-1)

Information: There are 89 other cells with the same violation. (TEST-171)

Pre-DFT violations completed...

-----------------------------------------------------------------

400 PRE-DFT VIOLATIONS

310 Uncontrollable clock input of flip-flop violations (D1)

90 DFF set/reset line not controlled violations (D3)

Source Code

File and Line

DRC on RTL? Use Text Reporting

Generic FF

Clock Pin

Generic FF

Async Clear

20 3-

Scripting for RTL UDRC (1/2)

p.1/2

# Enable HDL source file & line-number info.

set hdlin_enable_rtldrc_info true

# READ IN HDL SOURCE CODE:

# Must be register-transfer-level HDL code

# Could use analyze/elaborate

# or read_vhdl/read_verilog

set acs_hdl_source "../rtl/vhdl"

acs_read_hdl -f vhdl RISC_CORE

DFTC

Script

RTL HDL

Source Code

Enable Filename

and Line # tracking

21 3-

Scripting for RTL UDRC (2/2)

Defining

Protocol

# DEFINE TEST-PROTOCOL CLOCKS & CONTROLS:

# Specify existing inputs that control scan.

#

set_dft_signal -view exist -type ScanClock \

-timing {45 55} -port clk

set_dft_signal -view exist -type Reset \

-active_state 0 port rst_n

# DEFINE TEST-PROTOCOL HOLDS:

# Specify ASIC_TEST input held at constant 1.

set_dft_signal -view exist -type Constant \

-active_state 1 -port TEST_MODE

# Create the Test Protocol:

create_test_protocol

# RUN RTL DRC:

dft_drc

p.2/2

Invoking

RTL DRC

22 3-

Unified Test DRC: List of D rules

Rule Close To Description Affect

D1 ~C2 DFF clock input no controlled Prevents SCAN

D2 ~C2 DFF set input no controlled Prevents SCAN

D3 ~C2 DFF reset input no controlled Prevents SCAN

D4 (None) DLAT clock input no controlled Prevents SCAN

D5 (None) DLAT set input not controlled Prevents SCAN

D6 (None) DLAT reset input no controlled Prevents SCAN

D7 ~C20 RAM write input not controlled ATPG

D8 C4 {Clock/set/reset} unable to capture

D9 (New) Clock port not active when clocks set to on Prevents SCAN

D10 ~C26 Clock feeding data input ATPG

D11 ~C11,~C12,~C13 Clock feeding both clock and data input Possible ATPG race

D12 C14 Clock feeding multiple clock/set/reset inputs Possible ATPG race

D13 C5 Data for LS clock/write input affected by new capture Req. Seq. ATPG

D14 C6 Data for TE clock/write input affected by new capture Req. Seq. ATPG

D15 C8 LS clock/write/set/reset input affected by new capture Possible ATPG race

D16 C9 TE clock/write input affected by new capture Possible ATPG race

D17 C16 Clock port not capable of capturing data Prevents SCAN

D20 Z1 Bus gate capable of contention

D21 Z2 Bus capable of holding Z state

D22 Z3 Wire gate capable of contention

D23 X1 Sensitizable feedback path

23 3-

Step 3: Test-Ready Compile

Test-Ready Compile

Read RTL Design

Create Test Protocol

Specify Scan Paths

Insert Scan Paths

Read Design and

Test Protocol

Handoff Design

Unmapped

DFT Flow

Violations?

DFT Check

Timing, Area

DFT Check

Preview

Coverage

End

Start

Mapped

DFT Flow

Violations?

Violations?

Constraints

Met?

24 3-

Default Scan Style

Chip-Wide Scan Style:

set test_default_scan_style multiplexed_flip_flop

This is the factory default for the

system-wide .synopsys_dc.setup.

D

CP

D

CP

SI

SE

SI

SE

The scan style tells DFTC what

type of scan-equivalent flip-flop

to use during test-ready compile.

Your choice of style must be

supported by vendor library.

25 3-

Test-Ready Compile

D

CP

D

CP

SI

SE

SI

SE

D

CP

D

CP

SI

SE

SI

SE

TOP

U1

What Is It?

This DFTC option synthesizes all storage cells

out of scan flip-flops instead of regular flip-flops.

Why Do It?

Scan flip-flop area, timing, and output

loading are taken into account

during synthesis.

dc_shell-xg-t> compile -scan

HDL

Code

DFTC

technology

library

All unused pins are degenerated:

SE input pin is grounded.

SI input pin driven by Q.

Q output pin loaded by SI.

26 3-

GUI Debug of dft_drc violations

Debug features enabled in Design Vision platform

Provides GUI based debug environment for:

Pre DRC Violations

Post DRC Violations

CTL Models

Multiple TetraMAX Pin Data types available

No dependence on test_simulation_library variable

Supports CTL models for HSS flow

27 3-

GUI Components

Violation Browser

Launched after dft_drc finishes using:

Shell script command

Test pulldown menu Browse Violations

Allows selection of multiple violations of one type for

analysis

Violation Inspector

Schematic Viewer

Path schematic of violation and violation source

Allows selection of Pin Data types

Waveform Viewer

Debug test_setup procedures using simulation waveforms

Launched when Pin Data set to test_setup

28 3-

Usage Models

Run Design Vision in foreground

design_vision

Execute Script from the File pulldown menu to run dc_shell

script

Enter commands from design_vision command line

Browse Violations from the Violation Browser after

dft_drc

Launch Design Vision using a dc_shell-t script

design_vision f script.tcl | tee script.log

dft_drc

Design Vision top level launches after dft_drc, then use

Test Browse Violations to launch Violation Browser

NOTE: You must run your script in DesignVision

to use the GUI Debug features

29 3-

Design Vision: Top Level

Hierarchy Browser

Console

Window

Help

Test Pulldown Menu:

Browse Violations

to see all violations

Command

line

30 3-

Violation Browser: After Test Browse Violations

All

Violations

All D1

Violations

Selected

Violation

D1-13

Violation

Description

To Inspect a particular

violation click on the

Inspect Violation button

D1 Man

page

31 3-

D1 Analysis

Violation

D1 Violation

Source

CTL

Model

Feed Through

Clock

Pin Data

View

Tabs

To see Feedthru

click on input or

output pin

Forward/Back

History

32 3-

D2 Analysis

D2 Violation

Source

Pin Data

View Tabs

D1 and D2

D2 Violation

Source

Violation

To see fanin logic, double

click on input pin

33 3-

Lab 3: Creating Test Protocols

After completing this lab, you should be able to:

Use the design vision GUI for debugging

dft_drc problems related to test protocols

Write a script to create and verify a test

protocol

Explore a dc_shell-xg-t log file

60 minutes

You might also like

- VLSI Test Principles and Architectures: Design for TestabilityFrom EverandVLSI Test Principles and Architectures: Design for TestabilityRating: 4.5 out of 5 stars4.5/5 (4)

- Tips For Simulation Debug PDFDocument21 pagesTips For Simulation Debug PDFSaurin Shah100% (1)

- Scan Insertion FlowDocument9 pagesScan Insertion Flowsharath ANo ratings yet

- DFTDocument14 pagesDFTRahulNo ratings yet

- What Is DFT in VLSIDocument22 pagesWhat Is DFT in VLSINaga Nithesh100% (4)

- Assignment Section-1 1. What Is DFT?Document18 pagesAssignment Section-1 1. What Is DFT?PAVAN KUMAR TAVADABOINA100% (1)

- ATPG Methodology for Detecting Manufacturing DefectsDocument37 pagesATPG Methodology for Detecting Manufacturing DefectsaanbalanNo ratings yet

- Test Power Case Study: Transition Fault Testing (LOC, LOS) Power Analysis and Reduction TechniquesDocument22 pagesTest Power Case Study: Transition Fault Testing (LOC, LOS) Power Analysis and Reduction TechniqueseashwarNo ratings yet

- Post-Silicon SOC: Keywords: DFT (Design For Testability), ATPG (Automatic Test Pattern Generation)Document10 pagesPost-Silicon SOC: Keywords: DFT (Design For Testability), ATPG (Automatic Test Pattern Generation)Amena FarhatNo ratings yet

- DFT Interview Questions and AnswersDocument3 pagesDFT Interview Questions and AnswersJayesh PopatNo ratings yet

- Mahitha Scan Insertion Observation PDFDocument30 pagesMahitha Scan Insertion Observation PDFPrafulani Gajbhiye100% (1)

- QUALCOMM Interview Questions 1. Basic View of Compression?Document9 pagesQUALCOMM Interview Questions 1. Basic View of Compression?deepa100% (2)

- Scan Synthesis OverviewDocument149 pagesScan Synthesis OverviewNirmal Soni100% (6)

- 1 LOS and LOC in Vlsi Conference-ProceedingDocument9 pages1 LOS and LOC in Vlsi Conference-Proceedingbharghav saiNo ratings yet

- DFT Interview Questions & AnswersDocument22 pagesDFT Interview Questions & Answersdeepa100% (4)

- DFT Notes PrepDocument13 pagesDFT Notes PrepBrijesh S D100% (2)

- DFT QnsDocument6 pagesDFT QnsRajishaNo ratings yet

- Frequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimeDocument15 pagesFrequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimedeepaNo ratings yet

- DFT - CLK - Mux and DFT - CLK - Chain Data SheetDocument12 pagesDFT - CLK - Mux and DFT - CLK - Chain Data SheetRohit PatelNo ratings yet

- DFT Interview Questions1Document34 pagesDFT Interview Questions1rajkumar gunjaNo ratings yet

- DFT QuestionsDocument8 pagesDFT QuestionsNaga NitheshNo ratings yet

- IEEE 1500 Wrapper Architecture ModesDocument8 pagesIEEE 1500 Wrapper Architecture Modessrikanth100% (1)

- DFT Test Point InsertionDocument21 pagesDFT Test Point Insertionnoor_dcetNo ratings yet

- Timing SimulationDocument3 pagesTiming SimulationKarthik Sharma100% (1)

- DFTDocument21 pagesDFTMuhsin Nk100% (1)

- DFT VisionDocument18 pagesDFT VisionNaganithesh Ghattamaneni0% (1)

- Streaming Scan NetworkDocument51 pagesStreaming Scan NetworkVENKATRAMAN100% (1)

- DFT Interview QuestionsDocument2 pagesDFT Interview Questionsrupesh kumarNo ratings yet

- Q-A's On Atpg & ScanDocument33 pagesQ-A's On Atpg & ScanShankhadeep Das100% (2)

- Scan Insertion - Week2&3Document48 pagesScan Insertion - Week2&3VENKATRAMAN100% (1)

- DFT For Advanced UserDocument151 pagesDFT For Advanced UserAnonymous UeI6DVNo ratings yet

- DFT Interview QuestionsDocument9 pagesDFT Interview QuestionsNaga Nithesh100% (1)

- On DFTDocument16 pagesOn DFTAman TyagiNo ratings yet

- DFT Interview QsDocument4 pagesDFT Interview QsHARISH DAMARLANo ratings yet

- DFT Advantages Goals Types Cons Assignment 1Document12 pagesDFT Advantages Goals Types Cons Assignment 1senthilkumarNo ratings yet

- Atpg Answer Name: Meet ZankatDocument5 pagesAtpg Answer Name: Meet ZankatMeet ZankatNo ratings yet

- Atpg Coverage LossDocument4 pagesAtpg Coverage LossUmesh ParasharNo ratings yet

- ATPGDocument54 pagesATPGsrikanth100% (1)

- COMPRESSION PPT by HK - OdpDocument23 pagesCOMPRESSION PPT by HK - Odpsuneetha100% (5)

- MG580225 ATPG Clock Control Logic Appnote v2013 3 LPCT OCCDocument44 pagesMG580225 ATPG Clock Control Logic Appnote v2013 3 LPCT OCCchaitanyaNo ratings yet

- Scan and EDT IMP Questions SummaryDocument5 pagesScan and EDT IMP Questions SummaryMayur Mestry100% (1)

- Vasu DFTDocument28 pagesVasu DFTsenthilkumarNo ratings yet

- Some DFT Related QuestionsDocument5 pagesSome DFT Related QuestionsAdhi SuruliNo ratings yet

- DFT FlowDocument18 pagesDFT Flowsenthilkumar100% (1)

- Compression NotesDocument10 pagesCompression NotesSurendra Lovely Surendra50% (2)

- Segregated QuestionsDocument1 pageSegregated QuestionsdeepaNo ratings yet

- Training On EDT (1) - Copy (1) (3) 1Document52 pagesTraining On EDT (1) - Copy (1) (3) 1veena100% (1)

- Scan Insertion Lab Observation (K.S.K.S.sarma)Document33 pagesScan Insertion Lab Observation (K.S.K.S.sarma)Kittu Krishna100% (2)

- Scan PDFDocument49 pagesScan PDFferoz100% (1)

- DFT DocumentationDocument20 pagesDFT Documentationyamini100% (1)

- Edt Lab DocumentDocument12 pagesEdt Lab DocumentsenthilkumarNo ratings yet

- Edt Deterministic Test GuideDocument264 pagesEdt Deterministic Test GuideN Nanda Ganesh100% (4)

- DFT FaqDocument15 pagesDFT FaqBrijesh S D100% (1)

- DFT Rules - PPT 0Document18 pagesDFT Rules - PPT 0prakashthamankar50% (4)

- DFT (Design For Testability)Document21 pagesDFT (Design For Testability)lavanyaNo ratings yet

- NXP Interview QuestionsDocument29 pagesNXP Interview Questionsdeepa100% (1)

- Lab1 DC Tmax 2012 1217 v1Document43 pagesLab1 DC Tmax 2012 1217 v1jasonturfNo ratings yet

- Scan Chain Insertion and ATPG Using Design Compiler and TetraMAXDocument47 pagesScan Chain Insertion and ATPG Using Design Compiler and TetraMAXLakshmi PrasadNo ratings yet

- ASIC LabDocument75 pagesASIC LabMayur AgarwalNo ratings yet

- DFT 2006.06 SG 02 UiDocument34 pagesDFT 2006.06 SG 02 Uinoor_dcetNo ratings yet

- Sva QuickrefDocument31 pagesSva Quickrefnoor_dcetNo ratings yet

- Conversion From Boolean Logic To Layout DesignDocument31 pagesConversion From Boolean Logic To Layout Designnoor_dcetNo ratings yet

- An Introduction To LaTeXDocument46 pagesAn Introduction To LaTeXScribd_rkc100% (7)

- Data Structures in CDocument47 pagesData Structures in CRaghavendiran J M93% (15)

- VLSI Design - Design Rules and FabricationDocument28 pagesVLSI Design - Design Rules and Fabricationnoor_dcetNo ratings yet

- Basics of Operating Systems: What Is An Operating System?Document4 pagesBasics of Operating Systems: What Is An Operating System?Mamta VarmaNo ratings yet

- Design EconomicsDocument10 pagesDesign Economicsnoor_dcetNo ratings yet

- Layout and Stick DiagramDocument27 pagesLayout and Stick DiagramMGRNo ratings yet

- VLSI Design - Design Rules and FabricationDocument28 pagesVLSI Design - Design Rules and Fabricationnoor_dcetNo ratings yet

- Latex Instruction Sheet For Linux UsersDocument2 pagesLatex Instruction Sheet For Linux Usersnoor_dcetNo ratings yet

- Unfiled Notes 02 Feb 2011Document8 pagesUnfiled Notes 02 Feb 2011noor_dcetNo ratings yet

- Unfiled Notes 02 Feb 2011Document8 pagesUnfiled Notes 02 Feb 2011noor_dcetNo ratings yet

- MemoryDocument56 pagesMemorynoor_dcetNo ratings yet

- Virtual MemoryDocument28 pagesVirtual MemoryJainendra GautamNo ratings yet

- Circular QueuesDocument3 pagesCircular QueuesNoor E Mahaboob ShaikNo ratings yet

- Conversion From Infix To PostfixDocument2 pagesConversion From Infix To PostfixNoor E Mahaboob ShaikNo ratings yet

- FSM TutorialDocument4 pagesFSM Tutorialrajishkrishna88No ratings yet

- Arth CirDocument105 pagesArth Cirnoor_dcetNo ratings yet

- StackDocument2 pagesStackNoor E Mahaboob ShaikNo ratings yet

- Perl RegexDocument37 pagesPerl Regexnoor_dcetNo ratings yet

- Asic Design FlowDocument4 pagesAsic Design FlowBhatt JaydeepNo ratings yet

- Lex and YaacDocument41 pagesLex and YaacNoor E Mahaboob ShaikNo ratings yet

- Conversion From Infix To PostfixDocument2 pagesConversion From Infix To PostfixNoor E Mahaboob ShaikNo ratings yet

- LexDocument6 pagesLexwildgbirdNo ratings yet

- Application of StackDocument3 pagesApplication of Stacknoor_dcetNo ratings yet

- DFT Test Point InsertionDocument21 pagesDFT Test Point Insertionnoor_dcetNo ratings yet

- Dynamic Memory AllocationDocument2 pagesDynamic Memory Allocationnoor_dcetNo ratings yet

- Perl RegexDocument37 pagesPerl Regexnoor_dcetNo ratings yet

- FSM DesignDocument33 pagesFSM DesignNoor E Mahaboob ShaikNo ratings yet

- FSM TutorialDocument4 pagesFSM Tutorialrajishkrishna88No ratings yet

- ANALOG AND DIGITAL ELECTRONICS MCQDocument12 pagesANALOG AND DIGITAL ELECTRONICS MCQNoor AhmedNo ratings yet

- Asynchronous PipelinesDocument9 pagesAsynchronous PipelinesLakshman YandapalliNo ratings yet

- 74LVC1G74Document25 pages74LVC1G74lucas3No ratings yet

- Full Scan Vs Partial Scan EgDocument5 pagesFull Scan Vs Partial Scan Egsenthilkumar100% (1)

- BCA SyllabusDocument43 pagesBCA SyllabusamarkartuNo ratings yet

- QPSKDocument28 pagesQPSKgopiNo ratings yet

- ECE VHDL Verilog Lab Manual SemesterDocument133 pagesECE VHDL Verilog Lab Manual Semesterchiranjeevee02No ratings yet

- Mt8870, DTMF DecoderDocument20 pagesMt8870, DTMF DecoderMu IsNo ratings yet

- Digital Circuits and Microprocessors K-NotesDocument47 pagesDigital Circuits and Microprocessors K-NotesAyan SenguptaNo ratings yet

- SY - Synchronous Counter Using Flip FlopsDocument2 pagesSY - Synchronous Counter Using Flip FlopsAbhishek ParmarNo ratings yet

- DLC Lab QP Oct2019Document5 pagesDLC Lab QP Oct2019bnatarajNo ratings yet

- Icl 7135Document15 pagesIcl 7135santosh_babar_26No ratings yet

- HDL Compile For Verilog User GuideDocument208 pagesHDL Compile For Verilog User Guidebao wangNo ratings yet

- Design and Analysis of Dual Edge Triggered (DET) Flip-Flops Using Multiple C-ElementsDocument8 pagesDesign and Analysis of Dual Edge Triggered (DET) Flip-Flops Using Multiple C-ElementsArpita MukherjeeNo ratings yet

- Generate Pseudorandom Sequences with LFSRsDocument1 pageGenerate Pseudorandom Sequences with LFSRsSai KiranNo ratings yet

- Minor Project Report FormatDocument19 pagesMinor Project Report FormatPRATEEK SINGHNo ratings yet

- Code EEL204 Digital Electronics LAB Category L T P CreditDocument2 pagesCode EEL204 Digital Electronics LAB Category L T P CreditabhilashNo ratings yet

- P.A College VLSI Lab Record 2012-13Document50 pagesP.A College VLSI Lab Record 2012-13Sagar S Poojary100% (1)

- Cy37032p44 125acDocument62 pagesCy37032p44 125acWillian Santiago CardenasNo ratings yet

- Mtech Syllabus Jntu KDocument64 pagesMtech Syllabus Jntu KrppvchNo ratings yet

- Uc284xa Uc384xaDocument16 pagesUc284xa Uc384xayusufwpNo ratings yet

- Nirvana 5.5 - 11kW (7.5 - 15 HP) Variable Speed Drive: DangerDocument31 pagesNirvana 5.5 - 11kW (7.5 - 15 HP) Variable Speed Drive: Dangerseverino pepito100% (1)

- Digital IC Applications Lab Manual (R16Document36 pagesDigital IC Applications Lab Manual (R16usharaniNo ratings yet

- Hazards in Digital Logic and SwitchingDocument18 pagesHazards in Digital Logic and SwitchingAyush MukherjeeNo ratings yet

- CiscoDocument30 pagesCiscoAnurag MishraNo ratings yet

- P DIn Instruction ManualDocument52 pagesP DIn Instruction Manualcarbono980No ratings yet

- Question Bank of DMPDocument4 pagesQuestion Bank of DMPdarisbennisonNo ratings yet

- AL422B AverlogicTechnologiesDocument20 pagesAL422B AverlogicTechnologiescesareletNo ratings yet

- EN25F16 16 Megabit Serial Flash Memory With 4kbytes Uniform SectorDocument36 pagesEN25F16 16 Megabit Serial Flash Memory With 4kbytes Uniform SectorPeter FreimannNo ratings yet

- Syllabus Astu 3rd SemDocument12 pagesSyllabus Astu 3rd SemANKIT CHAKRABORTYNo ratings yet