Professional Documents

Culture Documents

766 10n

Uploaded by

SudhiStarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

766 10n

Uploaded by

SudhiStarCopyright:

Available Formats

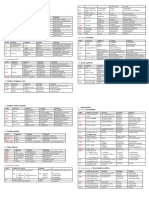

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

1

Error Detection

Data transmission can contain errors

Single-bit

Burst errors of length n

(n: distance between the first and last errors in data

block)

How to detect errors

If only data is transmitted, errors cannot be detected

Send more information with data that satisfies a

special relationship

Add redundancy

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

2

Error Detection Methods

Vertical Redundancy Check (VRC)

Append a single bit at the end of data block

such that the number of ones is even

Even Parity (odd parity is similar)

0110011 01100110

0110001 01100011

VRC is also known as Parity Check

Performance:

Detects all odd-number errors in a data block

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

3

Error Detection Methods

Longitudinal Redundancy Check (LRC)

Organize data into a table and create a parity

for each column

11100111 11011101 00111001 10101001

11100111

11011101

00111001

10101001

10101010

11100111 11011101 00111001 10101001 10101010

Original Data

LRC

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

4

Error Detection Methods

Performance:

Detects all burst errors up to length n

(number of columns)

Misses burst errors of length n+1 if there are n-1

uninverted bits between the first and last bit

If the block is badly garbled, the probability of

acceptance is

Checksum

Used by upper layer protocols

Similar to LRC, uses ones complement

arithmetic

n

2

1

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

5

Cyclic Redundancy Check

Powerful error detection scheme

Rather than addition, binary division is

used Finite Algebra Theory (Galois

Fields)

Can be easily implemented with small

amount of hardware

Shift registers

XOR (for addition and subtraction)

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

6

Cyclic Redundancy Check

Let us assume k message bits and

n bits of redundancy

Associate bits with coefficients of a

polynomial

1 0 1 1 0 1 1

1x

6

+0x

5

+1x

4

+1x

3

+0x

2

+1x+1

= x

6

+x

4

+x

3

+x+1

xxxxxxxxxx yyyy

k bits n bits

Block of length k+n

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

7

Cyclic Redundancy Check

Let M(x) be the message polynomial

Let P(x) be the generator polynomial

P(x) is fixed for a given CRC scheme

P(x) is known both by sender and receiver

Create a block polynomial F(x) based on

M(x) and P(x) such that F(x) is divisible by

P(x)

) (

0

) (

) (

) (

x P

x Q

x P

x F

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

8

Cyclic Redundancy Check

Sending

1. Multiply M(x) by x

n

2. Divide x

n

M(x) by P(x)

3. Ignore the quotient and keep the reminder C(x)

4. Form and send F(x) = x

n

M(x)+C(x)

Receiving

1. Receive F(x)

2. Divide F(x) by P(x)

3. Accept if remainder is 0, reject otherwise

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

9

Proof of CRC Generation

) (

) ( ) (

) (

) ( ) (

) (

) ( ) (

) ( ) ( ) ( ) (

) ( remainder ,

) (

) ( ) (

) ( by divisible is ) ( ) ( that Prove

x P

x C x C

x P

x Q x P

x P

x C x M x

x C x Q x P x M x

x C

x Q

x M x x P

x P x C x M x

n

n

n

n

Remainder 0 Remainder 0

Note: Binary modular addition is equivalent to

binary modular subtraction C(x)+C(x)=0

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

10

Example

Send

M(x) = 110011 x

5

+x

4

+x+1 (6 bits)

P(x) = 11001 x

4

+x

3

+1 (5 bits, n = 4)

4 bits of redundancy

Form x

n

M(x) 110011 0000

x

9

+x

8

+x

5

+x

4

Divide x

n

M(x) by P(x) to find C(x)

100001

1001

11001

10000

11001

1100110000 11001

= C(x)

Send the block 110011 1001

Receive

00000

11001

11001

11001

1100111001 11001

No remainder

Accept

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

11

Properties of CRC

Sent F(x), but received F(x) = F(x)+E(x)

When will E(x)/P(x) have no remainder,

i.e., when does CRC fail to catch an error?

1. Single Bit Error E(x) = x

i

If P(x) has two or more terms, P(x) will not divide E(x)

2. 2 Isolated Single Bit Errors (double errors)

E(x) = x

i

+x

j

, i>j

E(x) = x

j

(x

i-j

+1)

Provided that P(x) is not divisible by x, a sufficient

condition to detect all double errors is that P(x) does

not divide (x

t

+1) for any t up to i-j (i.e., block length)

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

12

Properties of CRC

3. Odd Number of Bit Errors

If x+1 is a factor of P(x), all odd number of bit errors

are detected

Proof:

Assume an odd number of errors has x+1 as a factor.

Then E(x) = (x+1)T(x).

Evaluate E(x) for x = 1

E(x) = E(1) = 1 since there are odd number of terms

(x+1) = (1+1) = 0

(x+1)T(x) = (1+1)T(1) = 0

E(x) (x+1)T(x)

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

13

Properties of CRC

4. Short Burst Errors

(Length t n, number of redundant bits)

E(x) = x

j

(x

t-1

++1) Length t, starting at bit position j

If P(x) has an x

0

term and t n, P(x) will not divide E(x)

All errors up to length n are detected

5. Long Burst Errors (Length t = n+1)

Undetectable only if burst error is the same as P(x)

P(x) = x

n

+ + 1 n-1 bits between x

n

and x

0

E(x) = 1 + + 1 must match

Probability of not detecting the error is 2

-(n-1)

6. Longer Burst Errors (Length t > n+1)

Probability of not detecting the error is 2

-n

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

14

Properties of CRC

Example:

CRC-12 = x

12

+x

11

+x

3

+x

2

+x+1

CRC-16 = x

16

+x

15

+x

2

+1

CRC-CCITT = x

16

+x

12

+x

5

+1

CRC-16 and CRC-CCITT catch all

Single and double errors

Odd number of bit errors

Bursts of length 16 or less

99.997% of 17-bit error bursts

99.998% of 18-bit and longer error bursts

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

15

Hardware Implementation

Usual practice:

After taking k data bits, n 0s are padded to the

stream, then divided by the generator

Aim:

Introduce the last n bits of 0s without requiring n extra

shifts

Eliminate the need to wait for all data to enter the

system to start generating CRC

Approach:

Guess the next n bits of message as all 0s

Correct the guess as the actual bits arrive

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

16

Hardware Implementation

Message = 1011011 k = 7

P(x) = 1101 = x

3

+x

2

+x

0

n = 3

1100101

01 0

1101

1100

0000

110 0

101 1

110 1

0000

0111

0000

0011

1101

1100

1101

000 1011011 1101

Conventional

Method:

1100101

01 0

1101

1100

0100

0000

010 0

010 1

101 1

00 10

000 1

0000

100 0

100 1

0000

0110

1110

1101

1010

1010

1101

1000

000 0000000 1101

Circuit:

1

0

1

1

0

1

1

M

e

s

s

a

g

e

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

17

Hardware Implementation

+

Data

Input

x

3

Serial Quotient (SQ)

+ 2 1 0

x

0

x

2

Transmit:

Data

1

0

1

1

0

1

1

SQ

1

1

0

0

1

0

1

Bit 2

0

1

1

1

1

1

0

0

Bit 1

0

0

1

1

0

0

1

0

Bit 0

0

1

1

0

0

1

0

1

M

e

s

s

a

g

e

LSB

MSB

CRC

Send MSB first

k shifts later, CRC is in register

Shift out (without any XOR) in n shifts

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

18

Hardware Implementation

+

Data

Input

x

3

Serial Quotient (SQ)

+ 2 1 0

x

0

x

2

Receive:

Data

1

0

1

1

0

1

1

0

0

1

SQ

1

1

0

0

1

0

1

0

0

0

Bit 2

0

1

1

1

1

1

0

0

0

1

0

Bit 1

0

0

1

1

0

0

1

0

1

0

0

Bit 0

0

1

1

0

0

1

0

1

0

0

0

M

e

s

s

a

g

e

LSB

MSB

n+k shifts later, remainder is 0

Data accepted

C

R

C

LSB

MSB

10 - Winter 2005

ECE

ECE 766

Computer Interfacing and Protocols

19

Hardware Implementation

Data Out

A

A

Data In

+

2

A

A

+

x

2

1 0

x

0

Data OK

Control Line A:

1: Make/Test CRC

0: Shift Out CRC

For Transmitting:

Assert A true while feeding k bits of message

Assert A false for n clock cycles to output CRC

For Receiving:

Assert A true while feeding k+n bits of message and CRC

Ignore Data Out, check Data OK for correctness

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Solutions To Irodov's Problems - Volume IIDocument442 pagesSolutions To Irodov's Problems - Volume IIZequinha de Abreu100% (2)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Cold Backup and Recovery From Archivelog - OrACLE-HELPDocument4 pagesCold Backup and Recovery From Archivelog - OrACLE-HELPadelarduarteNo ratings yet

- Water Reducing - Retarding AdmixturesDocument17 pagesWater Reducing - Retarding AdmixturesAbdullah PathanNo ratings yet

- A320 CBT Test 1 PDFDocument107 pagesA320 CBT Test 1 PDFCesarNo ratings yet

- SDH TechnologyDocument26 pagesSDH TechnologyJayesh SinghalNo ratings yet

- Vtol Design PDFDocument25 pagesVtol Design PDFElner CrystianNo ratings yet

- Nādatanumanisham Shankaram Namami Me Manasa ShirasaDocument12 pagesNādatanumanisham Shankaram Namami Me Manasa Shirasaveena murthyNo ratings yet

- Dynamic Modeling of GE 1.5 andDocument31 pagesDynamic Modeling of GE 1.5 andErtuğrul ÇamNo ratings yet

- ANSYS ACT Developers GuideDocument506 pagesANSYS ACT Developers GuideEDIZONNo ratings yet

- Curtis CatalogDocument9 pagesCurtis CatalogtharngalNo ratings yet

- Digital 101: Your Document Was Successfully Uploaded!Document2 pagesDigital 101: Your Document Was Successfully Uploaded!SudhiStarNo ratings yet

- Upload 5 Documents To Download: Digital 101Document3 pagesUpload 5 Documents To Download: Digital 101SudhiStarNo ratings yet

- Digital 101: Your Document Was Successfully Uploaded!Document2 pagesDigital 101: Your Document Was Successfully Uploaded!SudhiStarNo ratings yet

- Digital 101: Your Document Was Successfully Uploaded!Document2 pagesDigital 101: Your Document Was Successfully Uploaded!SudhiStarNo ratings yet

- Digital 101: Your Document Was Successfully Uploaded!Document2 pagesDigital 101: Your Document Was Successfully Uploaded!SudhiStarNo ratings yet

- Delete PleaseDocument1 pageDelete PleaseSudhiStarNo ratings yet

- Digital 101: Your Document Was Successfully Uploaded!Document2 pagesDigital 101: Your Document Was Successfully Uploaded!SudhiStarNo ratings yet

- Digital 101: Your Document Was Successfully Uploaded!Document2 pagesDigital 101: Your Document Was Successfully Uploaded!SudhiStarNo ratings yet

- Upload 4 Documents To Download: Redhawk PDFDocument3 pagesUpload 4 Documents To Download: Redhawk PDFSudhiStarNo ratings yet

- Digital 101: Your Document Was Successfully Uploaded!Document2 pagesDigital 101: Your Document Was Successfully Uploaded!SudhiStarNo ratings yet

- Upload 5 Documents To Download: Digital 101Document3 pagesUpload 5 Documents To Download: Digital 101SudhiStarNo ratings yet

- Digital 101: Your Document Was Successfully Uploaded!Document2 pagesDigital 101: Your Document Was Successfully Uploaded!SudhiStarNo ratings yet

- With Free Trial: in A Hurry? One-Click Set UpDocument1 pageWith Free Trial: in A Hurry? One-Click Set UpSudhiStarNo ratings yet

- Get Unlimited Downloads With A Free Scribd Trial!Document2 pagesGet Unlimited Downloads With A Free Scribd Trial!SudhiStarNo ratings yet

- Get Unlimited Downloads With A Free Scribd Trial!Document1 pageGet Unlimited Downloads With A Free Scribd Trial!SudhiStarNo ratings yet

- Upload 1 Document To Download: Mbist - WKBDocument2 pagesUpload 1 Document To Download: Mbist - WKBSudhiStarNo ratings yet

- Get Unlimited Downloads With A Free Scribd Trial!Document2 pagesGet Unlimited Downloads With A Free Scribd Trial!SudhiStarNo ratings yet

- Get Unlimited Downloads With A Free Scribd Trial!Document2 pagesGet Unlimited Downloads With A Free Scribd Trial!SudhiStarNo ratings yet

- Upload 4 Documents To Download: Samsung MBISTDocument2 pagesUpload 4 Documents To Download: Samsung MBISTSudhiStarNo ratings yet

- About Support: Home SavedDocument1 pageAbout Support: Home SavedSudhiStarNo ratings yet

- Samsung MBIST: Your Document Was Successfully Uploaded!Document1 pageSamsung MBIST: Your Document Was Successfully Uploaded!SudhiStarNo ratings yet

- Get Unlimited Downloads With A Free Scribd Trial!Document2 pagesGet Unlimited Downloads With A Free Scribd Trial!SudhiStarNo ratings yet

- Get Unlimited Downloads With A Free Scribd Trial!Document2 pagesGet Unlimited Downloads With A Free Scribd Trial!SudhiStarNo ratings yet

- Samsung MBIST: Your Document Was Successfully Uploaded!Document1 pageSamsung MBIST: Your Document Was Successfully Uploaded!SudhiStarNo ratings yet

- Upload 4 Documents To Download: Samsung MBISTDocument2 pagesUpload 4 Documents To Download: Samsung MBISTSudhiStarNo ratings yet

- Get Unlimited Downloads With A Free Scribd Trial!Document2 pagesGet Unlimited Downloads With A Free Scribd Trial!SudhiStarNo ratings yet

- Get Unlimited Downloads With A Free Scribd Trial!Document2 pagesGet Unlimited Downloads With A Free Scribd Trial!SudhiStarNo ratings yet

- Scribd: Get Unlimited Downloads With A 30 Day Free TrialDocument3 pagesScribd: Get Unlimited Downloads With A 30 Day Free TrialSudhiStarNo ratings yet

- Publish To The World: Presentations, Research Papers, Legal Documents, and MoreDocument7 pagesPublish To The World: Presentations, Research Papers, Legal Documents, and MoreSudhiStarNo ratings yet

- 123Document3 pages123SudhiStarNo ratings yet

- Scoop Atlas Wagner ST1810Document4 pagesScoop Atlas Wagner ST1810Juan Manuel PerezNo ratings yet

- XS Power Batteries D Series InstructionsDocument2 pagesXS Power Batteries D Series InstructionsAutopiezas PanaNo ratings yet

- ITTC Validation of ManoeuvringDocument11 pagesITTC Validation of ManoeuvringFelipe IlhaNo ratings yet

- Canalis KDP-KBA-KBB-KNA-KSA-20-1000A-2014Document324 pagesCanalis KDP-KBA-KBB-KNA-KSA-20-1000A-2014Rubén González CabreraNo ratings yet

- Recommended Procedures For Internet-Based Connections Between Rths and Nmcs (VPN, Ipsec)Document38 pagesRecommended Procedures For Internet-Based Connections Between Rths and Nmcs (VPN, Ipsec)Crismaruc Maria-madalinaNo ratings yet

- Advu en PDFDocument65 pagesAdvu en PDFGustavo Rodrigues de SouzaNo ratings yet

- Ze500 4 Parts Catalog en UsDocument9 pagesZe500 4 Parts Catalog en UsClaudia LopezNo ratings yet

- Leveling Limits For Stationary Reciprocating Compressors: Engineering ReferenceDocument2 pagesLeveling Limits For Stationary Reciprocating Compressors: Engineering ReferencealtruismNo ratings yet

- dp0 PDFDocument4 pagesdp0 PDFSimonNo ratings yet

- ABC-S Plus Web Info '08Document4 pagesABC-S Plus Web Info '08anon-331232No ratings yet

- Bottazzini RiemannDocument36 pagesBottazzini RiemanncedillaNo ratings yet

- RelativedensityipgDocument2 pagesRelativedensityipgapi-310625232No ratings yet

- Velocity profiles and incompressible flow field equationsDocument2 pagesVelocity profiles and incompressible flow field equationsAbdul ArifNo ratings yet

- Affixation (Landscape)Document4 pagesAffixation (Landscape)difafalahudinNo ratings yet

- Midterm Exam Result Ce199-1l 2Q1920Document3 pagesMidterm Exam Result Ce199-1l 2Q1920RA CarpioNo ratings yet

- Ibrahim Zeid: RsrecialDocument96 pagesIbrahim Zeid: RsrecialengrodeNo ratings yet

- Home Automation Iot Bca Up (2ND SEMINAR PPT) RTDocument30 pagesHome Automation Iot Bca Up (2ND SEMINAR PPT) RTTejaswiniNo ratings yet

- Huawei Mediapad m5 10.8inch Ръководство За Потребителя (Cmr-Al09, 01, Neu)Document6 pagesHuawei Mediapad m5 10.8inch Ръководство За Потребителя (Cmr-Al09, 01, Neu)Галина ЦеноваNo ratings yet

- Chapter 11 revision notes on budgeting and planningDocument5 pagesChapter 11 revision notes on budgeting and planningRoli YonoNo ratings yet

- 2N3866 Datasheet Rev BDocument5 pages2N3866 Datasheet Rev Bardier34No ratings yet