Professional Documents

Culture Documents

cs2100 14 Datapath

Uploaded by

thanhvnptOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

cs2100 14 Datapath

Uploaded by

thanhvnptCopyright:

Available Formats

CS2100 Computer Organisation

http://www.comp.nus.edu.sg/~cs2100/

The Processor: Datapath

(AY2013/2014) Semester 2

Road Map: Part II

Performance

Assembly

Language

Processor:

Datapath

Processor:

Control

Processor Datapath

Generic Execution

Stages

MIPS Execution Stages

Constructing Datapath

Pipelining

Cache

Processor: Datapath

Building a Processor: Datapath & Control

Two major components for a processor:

Datapath

Collection of components that process data

Performs the arithmetic, logical and memory

operations

Control

Tells the datapath, memory, and I/O devices what to

do according to program instructions

Processor: Datapath

MIPS Processor: Implementation

Simplest possible implementation of a subset of

the core MIPS ISA:

Arithmetic and Logical operations

Data transfer instructions

lw, sw

Branches

add, sub, and, or, addi, andi, ori, slt

beq, bne

Shift instructions (sll, srl) and J-type

instructions (j) will not be discussed:

Left as exercises

Processor: Datapath

Recap: Instruction Execution Cycle

Next Instruction

Instruction

Fetch

Instruction

Decode

Fetch:

Decode:

Operand

Fetch

Result

Write

Get operand(s) needed for operation

Execute:

Find out the operation required

Operand Fetch:

Execute

Get instruction from memory

Address is in Program Counter (PC)

Register

Perform the required operation

Result Write (Store):

Store the result of the operation

Processor: Datapath

MIPS Instruction Executions

Show the actual steps for 3 representative MIPS instructions

Fetch and Decode stages not shown:

The standard steps are performed

Fetch &

Decode

Operand

Fetch

Execute

Result

Write

add $3, $1, $2

lw $3, 20( $1 )

beq $1, $2, label

standard

standard

standard

oRead [$1] as opr1

oRead [$2] as opr2

oRead [$1] as opr1

oUse 20 as opr2

oRead [$1] as opr1

oRead [$2] as opr2

Result = opr1 + opr2

oMemAddr = opr1 + opr2

oUse MemAddr to read

from memory

Taken = (opr1 == opr2 )?

Target = PC + Label*

Result stored in $3

Memory data stored in $3

if (Taken)

PC = Target

opr = Operand

MemAddr = Memory Address

* = simplification, not exact

Processor: Datapath

5-STAGE MIPS EXECUTION

Design changes:

Merge Decode and Operand Fetch Decode is simple for MIPS

Split Execute into ALU (Calculation) and Memory Access

Fetch

add $3, $1, $2

lw $3, 20( $1 )

beq $1, $2, label

Read inst. at [PC]

Read inst. at [PC]

Read inst. at [PC]

Decode &

oRead [$1] as opr1

Operand

oRead [$2] as opr2

Fetch

ALU

Result = opr1 + opr2

Memory

Access

Result

Write

oRead [$1] as opr1

oUse 20 as opr2

oRead [$1] as opr1

oRead [$2] as opr2

MemAddr = opr1 + opr2

Taken = (opr1 == opr2 )?

Target = PC + Label*

Use MemAddr to read

from memory

Result stored in $3

Memory data stored in $3

Processor: Datapath

if (Taken)

PC = Target

Let's Build a MIPS Processor

What we are going to do:

Look at each stage closely, figure out the

requirements and processes

Sketch a high level block diagram, then zoom in

for each elements

With the simple starting design, check whether

different type of instructions can be handled:

Add modifications when needed

Study the design from the viewpoint of a

designer, instead of a "tourist"

Processor: Datapath

Fetch Stage: Requirements

Instruction Fetch Stage:

1. Use the Program Counter (PC) to fetch the

instruction from memory

PC is implemented as a special register in the processor

2. Increment the PC by 4 to get the address of the next

instruction:

How do we know the next instruction is at PC+4?

Note the exception when branch/jump instruction is executed

Output to the next stage (Decode):

The instruction to be executed

Processor: Datapath

Fetch Stage: Block Diagram

A simple

adder

Add

PC

Read

address

Instruction

Instruction

Instruction

memory

Decode Stage

A register

Memory which

stores program

instructions

Processor: Datapath

10

Element: Instruction Memory

Storage element for the instructions

Recall: sequential circuit

Has an internal state that stores

information

Clock signal is assumed and not shown

Instruction

Address

Instruction

Instruction

Memory

Supply instructions given the address

Given instruction address M as input, the

memory outputs the content at address M

Memory

2048

..

add $3, $1, $2

2052 sll $4, $3, 2

Conceptual diagram of the memory layout

is given on the right

Processor: Datapath

2056

andi $1, $4, 0xF

..

11

Element: Adder

Combinational logic to implement the

addition of two numbers

A

Inputs:

Add

Two 32-bit numbers A, B

Sum

Output:

A+B

Sum of the input numbers, A + B

Just a 32-bit version of the adder

discussed in first part of the course

Processor: Datapath

12

The Idea of Clocking

It seems that we are reading and updating the PC at

the same time:

How can it works properly?

Magic of clock:

PC is read during the first half of the clock period and it is

updated with PC+4 at the next rising clock edge

Add

4

In

PC

Time

Read

address

Clk

Instruction

Instruction

memory

PC

In

100

104

Processor: Datapath

104

108

108

112

112

116

13

Decode Stage: Requirement

Instruction Decode Stage:

1.

2.

Gather data from the instruction fields:

Read the opcode to determine instruction type and

field lengths

Read data from all necessary registers

Input from previous stage (Fetch):

Can be two (e.g. add), one (e.g. addi) or zero (e.g. j)

Instruction to be executed

Output to the next stage (Execute):

Operation and the necessary operands

Processor: Datapath

14

Decode Stage: Block Diagram

Fetch Stage

Inst.

Read

register 1

Read

register 2

Write

register

Read

data 1

Register

File

Data

Operands

Read

data 2

Execute Stage

Register

Number

Collection of

registers, known

as register file

Processor: Datapath

15

Element: Register File

A collection of 32 registers:

Each 32-bit wide and can be read/written by specifying register

number

Read at most two registers per instruction

Write at most one register per instruction

RegWrite is a control signal to indicate:

Writing of register

1(True) = Write, 0 (False) = No Write

Register

Number

Read

register 1

Read

register 2

Data

Write

register

Write

data

Read

data 1

Register

File

Data

Read

data 2

RegWrite

Processor: Datapath

16

Decode Stage: R-Type Instruction

add $8, $9, $10

opcode

31:26

000000

rs

25:21

01001

Inst [25:21]

01010

rt

20:16

Read

register 1

Read

register 2

Write

register

Read

data 1

content of

register $9

Register

File

rd

15:11

01000

shamt

10:6

00000

Write

data

Read

data 2

content of

register $10

RegWrite

100000

funct

5:0

Result to be

stored

(produced by later

stage)

Notation:

Inst [Y:X]

= bits X to Y in Instruction

Processor: Datapath

17

Decode Stage: I-Type Instruction

addi $21, $22, -50

opcode

31:26

001000

rs

25:21

10110

Inst [25:21]

10101

rt

20:16

Read

register 1

Read

register 2

Write

register

Read

data 1

Content of

register $22

Register

File

Immediate

15:0

1111 1111 1100 1110

Write

data

Read

data 2

RegWrite

Problems:

- Destination $21 is in the "wrong position"

- Read Data 2 is an immediate value, not from register

Processor: Datapath

18

Decode Stage: Choice in Destination

addi $21, $22, -50

opcode

31:26

001000

rs

25:21

10110

Inst [25:21]

10101

rt

20:16

Read

register 1

Read

register 2

1111 1111 1100 1110

Immediate

15:0

Inst [15:11]

M

U

X

Write

register

Write

data

RegDst

RegDst:

A control signal to choose

either Inst[20:16] or Inst[15:11]

as the write register number

Read

data 1

Register

File

Read

data 2

Solution (Wr. Reg. No.):

Use a multiplexer to choose the

correct write register number

based on instruction type

Processor: Datapath

19

Recap: Multiplexer

Function:

Selects one input from multiple input lines

Control

m

Inputs:

n lines of same width

.

.

.

inn-1

Control:

in0

out

m bits where n = 2m

Control=0 select in0

Control=3 select in3

Output:

M

U

X

Select ith input line if control=i

Processor: Datapath

20

Decode Stage: Choice in Data 2

opcode

31:26

001000

rs

25:21

10110

addi $21, $22, -50

Inst [25:21]

10101

rt

20:16

Read

register 1

Read

register 2

Immediate

15:0

1111 1111 1100 1110

Inst [15:11]

M

U

X

Write

register

Read

data 1

Register

File

Read

data 2

Write

data

RegWrite

M

U

X

RegDst

Inst [15:0]

16

Sign

Extend

32

ALUSrc

Solution (Rd. Data 2):

Use a multiplexer to choose the correct operand 2.

Sign extend the 16-bit immediate value to 32-bit

Processor: Datapath

ALUSrc:

A control signal to

choose either

"Read data 2" or

the sign extended

Inst[15:0] as the

second operand

21

Decode Stage: Load Word Instruction

Try it out: "lw $21, -50($22)"

opcode

31:26

100011

rs

25:21

10110

Do we need any modification?

Inst [25:21]

10101

rt

20:16

Read

register 1

Read

register 2

Immediate

15:0

1111 1111 1100 1110

Inst [15:11]

M

U

X

Write

register

Read

data 1

Register

File

Read

data 2

Write

data

RegWrite

M

U

X

RegDst

Inst [15:0]

16

Sign

Extend

32

Processor: Datapath

ALUSrc

22

Decode Stage: Branch Instruction

Example: "beq $9, $0, 3"

opcode

31:26

000100

rs

25:21

01001

Need to calculate branch outcome and target at the same

time!

We will tackle this problem in the ALU Stage

Inst [25:21]

00000

rt

20:16

Read

register 1

Read

register 2

Immediate

15:0

0000 0000 0000 0011

Inst [15:11]

M

U

X

Write

register

Read

data 1

Register

File

Read

data 2

Write

data

RegWrite

RegDst

Inst [15:0]

16

Sign

Extend

32

Processor: Datapath

M

U

X

ALUSrc

23

Decode Stage: Summary

Inst [25:21]

Inst[31:0]

Inst [15:11]

Read

register 1

Read

register 2

Write

register

M

U

X

Read

data 1

Registers

Write

data

Read

data 2

RegWrite

RegDst

Inst [15:0]

16

Operand 1

Sign

Extend

32

Processor: Datapath

M

U

X

Operand 2

ALUSrc

24

ALU Stage: Requirement

Instruction ALU Stage:

ALU = Arithmetic-Logic Unit

Perform the real work for most instructions here

Input from previous stage (Decode):

Arithmetic (e.g. add, sub), Shifting (e.g. sll), Logical

(e.g. and, or)

Memory operation (e.g. lw, sw): Address calculation

Branch operation (e.g. bne, beq): Perform register

comparison and target address calculation

Operation and Operand(s)

Output to the next stage (Memory):

Calculation result

Processor: Datapath

25

ALU Stage: Block Diagram

ALU

Memory Stage

Decode Stage

Operands

ALU

result

Logic to perform

arithmetic and

logical operations

Processor: Datapath

26

Element: Arithmetic Logical Unit

ALU (Arithmetic-logical unit)

isZero?

ALU

result

A op B

Control:

(A op B) == 0?

ALU

Two 32-bit numbers

ALUcontrol

Inputs:

Combinational logic to implement

arithmetic and logical operations

4-bit to decide the particular

operation

Outputs:

Result of arithmetic/logical operation

A 1-bit signal to indicate whether

result is zero

Processor: Datapath

ALUcontrol

Function

0000

AND

0001

OR

0010

add

0110

subtract

0111

slt

1100

NOR

27

ALU Stage: Non-Branch Instructions

We can handle non-branch instructions easily:

add $8, $9, $10

opcode

31:26

000000

rs

25:21

01001

Inst [25:21]

01010

rt

20:16

rd

15:11

01000

shamt

10:6

00000

Inst [15:11]

Read

register 1

Read

register 2

Write

register

M

U

X

Write

data

ALUcontrol

Read

data 1

isZero?

Register

File

Read

data 2

RegWrite

RegDst

100000

funct

5:0

Inst [15:0]

ALU

ALU

result

M

U

X

ALUSrc

16

Sign

Extend

32

Processor: Datapath

ALUcontrol:

Set using opcode + funct

field (more in next lecture)

28

ALU Stage: Brach Instructions

Branch instruction is harder as we need to

perform two calculations:

Example: "beq $9, $0, 3"

1. Branch Outcome:

Use ALU unit to compare the register

The 1-bit "isZero?" signal is enough to handle equal / not

equal check (how?)

2. Branch Target Address:

Introduce additional logic to calculate the address

Need PC (from Fetch Stage)

Need Offset (from Decode Stage)

Processor: Datapath

29

Complete ALU Stage

PC

Add

M

U

X

Add

opcode

31:26

000100

rs

25:21

01001

Left Shift

2-bit

ALUcontrol

Inst [25:21]

00000

rt

20:16

Immediate

15:0

0000 0000 0000 0011

Inst [15:11]

Read

register 1

Read

register 2

Write

register

M

U

X

Write

data

Read

data 1

Read

data 2

RegDst

16

Sign

Extend

Register

File

RegWrite

Inst [15:0]

PCSrc

32

PCSrc:

Control Signal

to select

between

(PC+4) or

Branch Target

isZero?

ALU

ALU

result

M

U

X

ALUSrc

E.g. "beq $9, $0, 3"

Processor: Datapath

30

Memory Stage: Requirement

Instruction Memory Access Stage:

Only the load and store instructions need to perform

operation in this stage:

All other instructions remain idle

Result from ALU Stage will pass through to be used in Result

Store stage if applicable

Input from previous stage (ALU):

Use memory address calculated by ALU Stage

Read from or write to data memory

Computation result to be used as memory address (if

applicable)

Output to the next stage (Result Write):

Result to be stored (if applicable)

Processor: Datapath

31

Memory Stage: Block Diagram

MemWrite

Result

Write

Data

Read

Data

Data

Memory

Result Store

Stage

ALU Stage

Address

MemRead

Memory which

stores data

values

Processor: Datapath

32

Element: Data Memory

Storage element for the data of a program

Inputs:

Memory Address

Data to be written (Write Data) for store

instructions

Read and Write controls; only one can be

asserted at any point of time

Read

Data

Data

Memory

MemRead

Output:

Address

Write

Data

Control:

MemWrite

Data read from memory (Read Data) for load

instructions

Processor: Datapath

33

Memory Stage: Load Instructions

Only relevant parts of Decode & ALU Stage are shown

lw $21, -50($22)

opcode

31:26

100011

000100

rs

25:21

10110

01001

ALUcontrol

Inst [25:21]

10101

00000

rt

20:16

5

5

Immediate

15:0

1111

0000 1111

0000 1100

0000 1110

0011

Inst [15:11]

M

U

X

4

RR1

RD1

MemWrite

RR2

Registers

ALU

WR

RD2

M

U

X

WD

RegWrite

RegDst

Inst [15:0]

16

Sign

Extend

32

ALUSrc

Processor: Datapath

ALU

result

Address

Data

Memory

Write

Data

Read

Data

MemRead

34

Memory Stage: Store Instructions

Need Read Data 2 (Decode) as the Write Data

sw $21, -50($22)

opcode

31:26

101011

000100

rs

25:21

10110

01001

ALUcontrol

Inst [25:21]

10101

00000

rt

20:16

5

5

Immediate

15:0

1111

0000 1111

0000 1100

0000 1110

0011

Inst [15:11]

M

U

X

4

RR1

RD1

MemWrite

RR2

Registers

ALU

WR

RD2

M

U

X

WD

RegWrite

16

Address

Data

Memory

Write

Data

RegDst

Inst [15:0]

ALU

result

Sign

Extend

32

Processor: Datapath

Read

Data

MemRead

35

Memory Stage: Non-Memory Instructions

Add a multiplexer to choose the result to be stored

add $8, $9, $10

opcode

31:26

000000

rs

25:21

01001

ALUcontrol

Inst [25:21]

01010

rt

20:16

5

5

01000

rd

15:11

Inst [15:11]

M

U

X

4

RR1

RD1

MemWrite

RR2

Registers

ALU

WR

RD2

00000

shamt

10:6

M

U

X

WD

RegWrite

100000

funct

5:0

16

Address

Data

Memory

Write

Data

RegDst

Inst [15:0]

ALU

result

Sign

Extend

Read

Data

32

MemToReg:

Processor: Datapath

A control signal to indicate

whether result came from

memory or ALU unit

M

U

X

MemToReg

36

Result Write Stage: Requirement

Instruction Register Write Stage:

Most instructions write the result of some

computation into a register

Exceptions are stores, branches, jumps:

Examples: arithmetic, logical, shifts, loads, set-less-than

Need destination register number and computation

result

There are no result to be written

These instructions remain idle in this stage

Input from previous stage (Memory):

Computation result either from memory or ALU

Processor: Datapath

37

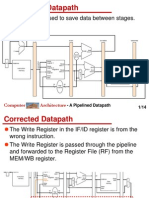

Result Write Stage: Block Diagram

Memory Stage

Result

Read

register 1

Read

register 2

Write

register

Write

data

Read

data 1

Registers

Read

data 2

Result Write stage has no additional element:

Basically just route the correct result into register

file

The Write Register number is generated way

back in the Decode Stage

Processor: Datapath

38

Result Write Stage: Routing

add $8, $9, $10

opcode

31:26

000000

rs

25:21

01001

ALUcontrol

Inst [25:21]

01010

rt

20:16

5

5

01000

rd

15:11

Inst [15:11]

M

U

X

4

RR1

RD1

MemWrite

RR2

Registers

ALU

WR

RD2

WD

00000

shamt

10:6

RegWrite

M

U

X

ALU

result

Address

Data

Memory

Write

Data

100000

funct

5:0

Inst [15:0]

Sign

Extend

Processor: Datapath

Read

Data

MemToReg

M

U

X

39

The Complete Datapath!

We have just finished "designing" the datapath

for a subset of MIPS instructions:

Shifting and Jumping are not supported

Check your understanding:

Take the complete datapath and play the role of

controller:

See how supported instructions are executed

Figure out the correct control signals for the datapath

elements

Coming up next: Control (Lecture #15)

Processor: Datapath

40

Complete Datapath

Instruction

Memory

PC

Instruction

Add

Add

Left Shift

2-bit

Address

M

U

X

opcode

31:26

000000

rs

25:21

01001

PCSrc

ALUcontrol

Inst [25:21]

01010

rt

20:16

5

5

rd

15:11

01000

shamt

10:6

00000

Inst [15:11]

M

U

X

RegDst

100000

funct

5:0

Inst [15:0]

4

RR1

RD1

is0?

RR2

Registers

WR

RD2

WD

RegWrite

ALUSrc

M

U

X

MemWrite

ALU

ALU

result

Address

Data

Memory

Write

Data

Sign

Extend

Read

Data

MemToReg

M

U

X

MemRead

Processor: Datapath

41

Reading Assignment

The Processor: Datapath and Control

3rd edition: Chapter 5 Sections 5.1 5.3

4th edition: Chapter 4 Sections 4.1 4.3

Processor: Datapath

42

End

Processor: Datapath

43

You might also like

- Controlling A Pipelined DatapathDocument17 pagesControlling A Pipelined DatapathAlexander TaylorNo ratings yet

- COE301 Lab 12 Single Cycle CPU DesignDocument10 pagesCOE301 Lab 12 Single Cycle CPU DesignItz Sami UddinNo ratings yet

- The Processor: (Datapath and Pipelining)Document144 pagesThe Processor: (Datapath and Pipelining)paranoid486No ratings yet

- Datapath For The MIPS Architecture (A Single-Cycle Implementation)Document22 pagesDatapath For The MIPS Architecture (A Single-Cycle Implementation)Alexander TaylorNo ratings yet

- Computer Architecture MIPS Processor DescriptionDocument41 pagesComputer Architecture MIPS Processor DescriptionAsif HussainNo ratings yet

- CS M151B / EE M116C: Computer Systems ArchitectureDocument38 pagesCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacNo ratings yet

- CENG 331 Course Slides Chapter 5Document73 pagesCENG 331 Course Slides Chapter 5Odunayo KusoroNo ratings yet

- Instructions: Language of The Computer PDocument92 pagesInstructions: Language of The Computer PAdip ChyNo ratings yet

- 4 29 03 ImplementingMIPS 0429Document45 pages4 29 03 ImplementingMIPS 0429wraith324No ratings yet

- Cs/Coe 1541: Single and Multi-Cycle ImplementationsDocument93 pagesCs/Coe 1541: Single and Multi-Cycle ImplementationsBobo JooNo ratings yet

- A Pipelined Datapath: Resisters Are Used To Save Data Between StagesDocument14 pagesA Pipelined Datapath: Resisters Are Used To Save Data Between StagesJohnDaGRTNo ratings yet

- Instructions: Language of the ComputerDocument49 pagesInstructions: Language of the ComputershobhitNo ratings yet

- Chap. 5 Basic Computer Org. and Design: 5-1 Instruction CodesDocument21 pagesChap. 5 Basic Computer Org. and Design: 5-1 Instruction CodesSisay ADNo ratings yet

- Chapter 2:instructions: Language of The ComputerDocument81 pagesChapter 2:instructions: Language of The ComputerGreen ChiquitaNo ratings yet

- Chapter 2 Instructions Language of The ComputerDocument93 pagesChapter 2 Instructions Language of The ComputersonygabrielNo ratings yet

- Single Cycle Datapath PDFDocument30 pagesSingle Cycle Datapath PDFShivam KhandelwalNo ratings yet

- EE361 SingleMIPSDocument19 pagesEE361 SingleMIPSThùyVũNo ratings yet

- Endsem PDFDocument16 pagesEndsem PDFAnujNagpalNo ratings yet

- 1,2,3Document43 pages1,2,3SoumyajitNo ratings yet

- Mips DatapathDocument23 pagesMips DatapathKaran KampaniNo ratings yet

- Bcs Lab Manual 2018 19Document113 pagesBcs Lab Manual 2018 19Manasa MvNo ratings yet

- CP Notes (BDPS) PDFDocument332 pagesCP Notes (BDPS) PDFYesudas100% (2)

- Chapter 1 Introduction To Microprocessor and MicrocontrollerDocument21 pagesChapter 1 Introduction To Microprocessor and MicrocontrollernikmatenaNo ratings yet

- Multicycle Datapath PDFDocument22 pagesMulticycle Datapath PDFShivam KhandelwalNo ratings yet

- Operation of DatapathDocument13 pagesOperation of Datapathsas21-d01-s6-cs15No ratings yet

- Advanced Advanced Computer Computer Architecture ArchitectureDocument34 pagesAdvanced Advanced Computer Computer Architecture ArchitectureSam Thui Sam ThuiNo ratings yet

- Processing Unit & I/O Organization: Chapter OneDocument10 pagesProcessing Unit & I/O Organization: Chapter OneKarthik RoshanNo ratings yet

- Chapter 02 Computer Organization and Design, Fifth Edition: The Hardware/Software Interface (The Morgan Kaufmann Series in Computer Architecture and Design) 5th EditionDocument93 pagesChapter 02 Computer Organization and Design, Fifth Edition: The Hardware/Software Interface (The Morgan Kaufmann Series in Computer Architecture and Design) 5th EditionPriyanka Meena75% (4)

- 440 Datapath Control 1Document25 pages440 Datapath Control 1Srilatha PradeepNo ratings yet

- Datapaths II & Control IDocument41 pagesDatapaths II & Control IAndrea AquinoNo ratings yet

- COP3402 Lecture11Document31 pagesCOP3402 Lecture11abhirbhandaryNo ratings yet

- Basic SAP-1 Computer Architecture ExplainedDocument9 pagesBasic SAP-1 Computer Architecture ExplainedAshna100% (1)

- CpuDocument51 pagesCpujunaidalighouriNo ratings yet

- Lectures 02, 03 Introduction To Stored Programs": Suggested Reading:" HP Chapters 1.1-1.3"Document30 pagesLectures 02, 03 Introduction To Stored Programs": Suggested Reading:" HP Chapters 1.1-1.3"SandipChowdhuryNo ratings yet

- Creating IPCore Loi 11may2013Document20 pagesCreating IPCore Loi 11may2013LinkyNo ratings yet

- Programming 8-Bit Pic Microcontrollers Inc: Martin Bates Elsevier 2008Document30 pagesProgramming 8-Bit Pic Microcontrollers Inc: Martin Bates Elsevier 2008SonyKurupNo ratings yet

- Computer Architecture Computer SystemsDocument27 pagesComputer Architecture Computer SystemsRudolfNo ratings yet

- Chapter 4Document71 pagesChapter 4Yididiya TilahunNo ratings yet

- Part 1Document30 pagesPart 1ady63100% (1)

- Lec12 Basic Computer OrganizationDocument75 pagesLec12 Basic Computer OrganizationAya AbdAllah AmmarNo ratings yet

- Fundamentals of Processor Design: Using Figures From by Hamblen and FurmanDocument35 pagesFundamentals of Processor Design: Using Figures From by Hamblen and Furmanwilliamjamir2295No ratings yet

- Examen Co PartialDocument7 pagesExamen Co PartialGuillermo SánchezNo ratings yet

- Components of Computer and Data Representation: Saima JabeenDocument18 pagesComponents of Computer and Data Representation: Saima JabeenAnas AsifNo ratings yet

- TASK 1 - Integer Multiplication in The MIPS Assembly LanguageDocument6 pagesTASK 1 - Integer Multiplication in The MIPS Assembly LanguageSidra MalikNo ratings yet

- CS M151B / EE M116C: Computer Systems ArchitectureDocument34 pagesCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacNo ratings yet

- BME 438 Digital Logic Design and Computer Architecture LabDocument73 pagesBME 438 Digital Logic Design and Computer Architecture LabHafiz Muhammad Ahmad RazaNo ratings yet

- Chapter 5 - The Processor: Datapath and ControlDocument101 pagesChapter 5 - The Processor: Datapath and Controlapi-26072581No ratings yet

- Ch01 Basic Concepts and Computer EvolutionDocument36 pagesCh01 Basic Concepts and Computer EvolutionMark ShanNo ratings yet

- Milestone 2-UpdatedDocument13 pagesMilestone 2-UpdatedHưng Nguyễn ThànhNo ratings yet

- Computer Architecture and OrganizationDocument46 pagesComputer Architecture and OrganizationAdeeti Chopra SNo ratings yet

- L24 PipelineDocument40 pagesL24 PipelineES SENo ratings yet

- SsDocument60 pagesSsponns100% (1)

- Lec19 PDFDocument39 pagesLec19 PDFMustafa Rashik HasnainNo ratings yet

- Chapter 5: The Processor: Datapath and Control: I. MIPS ImplementationDocument6 pagesChapter 5: The Processor: Datapath and Control: I. MIPS ImplementationNguyễn Quốc VũNo ratings yet

- Hardwired ControlDocument6 pagesHardwired Controlapi-19967001No ratings yet

- PIC - New - Part 1 PIC Microcontroller Systems PDFDocument5 pagesPIC - New - Part 1 PIC Microcontroller Systems PDFLam Nguyen100% (1)

- Exploring Arduino: Tools and Techniques for Engineering WizardryFrom EverandExploring Arduino: Tools and Techniques for Engineering WizardryRating: 4.5 out of 5 stars4.5/5 (5)

- Implementing Image Processing Algorithms On FPGAsDocument7 pagesImplementing Image Processing Algorithms On FPGAsthanhvnptNo ratings yet

- Senzations14 Networking NodejsDocument30 pagesSenzations14 Networking NodejsthanhvnptNo ratings yet

- CodeDocument1 pageCodeGaby Esquivel RojasNo ratings yet

- Operation of Keyboard and Mouse Via PS2 ProtocolDocument16 pagesOperation of Keyboard and Mouse Via PS2 ProtocolthanhvnptNo ratings yet

- Quick StartDocument33 pagesQuick StartthanhvnptNo ratings yet

- Universal Asynchronous Receiver/Transmitter (UART) On The LM3S8962Document12 pagesUniversal Asynchronous Receiver/Transmitter (UART) On The LM3S8962thanhvnptNo ratings yet

- H264 TutorialDocument75 pagesH264 TutorialthanhvnptNo ratings yet

- Gabor Wavelet Transform and Its Application PDFDocument16 pagesGabor Wavelet Transform and Its Application PDFTien DatNo ratings yet

- Vivado TutorialDocument25 pagesVivado TutorialthanhvnptNo ratings yet

- Gabor Filter Analysis For Texture SegmentationDocument58 pagesGabor Filter Analysis For Texture SegmentationthanhvnptNo ratings yet

- EW GettingStarted - EnuDocument58 pagesEW GettingStarted - EnuthanhvnptNo ratings yet

- Vivado Design Suite User GuideDocument85 pagesVivado Design Suite User GuidethanhvnptNo ratings yet

- Esp 8266 at Commands SetDocument1 pageEsp 8266 at Commands Setthanhvnpt100% (1)

- Gab orDocument29 pagesGab orBhavik VachhaniNo ratings yet

- Use Case DiagramsDocument42 pagesUse Case Diagramssrikanthkg100% (3)

- Design A Fast ALU For The MIPS ISA - Requirements ?Document71 pagesDesign A Fast ALU For The MIPS ISA - Requirements ?thanhvnptNo ratings yet

- 2012 12 IEEE HEVC PerformanceDocument16 pages2012 12 IEEE HEVC PerformancethanhvnptNo ratings yet

- Vivado High Level Synthesis TutorialDocument264 pagesVivado High Level Synthesis TutorialthanhvnptNo ratings yet

- Data SheetDocument10 pagesData SheetthanhvnptNo ratings yet

- SRF05 - Ultra-Sonic Ranger: Technical SpecificationDocument4 pagesSRF05 - Ultra-Sonic Ranger: Technical SpecificationRizki WahyuNo ratings yet

- Vivado TutorialDocument25 pagesVivado TutorialthanhvnptNo ratings yet

- TFT LCD Display-Camera - 1Document40 pagesTFT LCD Display-Camera - 1thanhvnptNo ratings yet

- Camera Controller Project Report - EDA385Document18 pagesCamera Controller Project Report - EDA385thanhvnptNo ratings yet

- Automatic Analysis of Fish Behaviors and Abnormality DetectionDocument5 pagesAutomatic Analysis of Fish Behaviors and Abnormality DetectionthanhvnptNo ratings yet

- Timequest CookbookDocument34 pagesTimequest CookbookthanhvnptNo ratings yet

- EE471 Lab4 DiffractionDocument4 pagesEE471 Lab4 DiffractionthanhvnptNo ratings yet

- Wireshark Lab: Getting Started: Approach, 7 Ed., J.F. Kurose and K.W. RossDocument10 pagesWireshark Lab: Getting Started: Approach, 7 Ed., J.F. Kurose and K.W. RossJhon TrianaNo ratings yet

- Behavioral Modeling LabDocument11 pagesBehavioral Modeling LabthanhvnptNo ratings yet

- BL M07C881Document5 pagesBL M07C881thanhvnptNo ratings yet

- 150Mbps Wireless N Router WF2411-EUDocument1 page150Mbps Wireless N Router WF2411-EUh1238709mNo ratings yet

- ME6703 CIM Important Questions Unit 1Document2 pagesME6703 CIM Important Questions Unit 1raja30gNo ratings yet

- ERPSCM MM SRVServiceEntrySheet 180915 0417 1152Document7 pagesERPSCM MM SRVServiceEntrySheet 180915 0417 1152ronnzaaNo ratings yet

- M702 21C e ST 2Document5 pagesM702 21C e ST 2amirul ashraf abd azizNo ratings yet

- Exercise Sheet 2 PDFDocument2 pagesExercise Sheet 2 PDFMariem BoussaadiaNo ratings yet

- Decreto 9204 JoinvilleDocument68 pagesDecreto 9204 JoinvilleVitor OgliariNo ratings yet

- Rockwell Automation OverviewDocument13 pagesRockwell Automation OverviewVivek ThotaNo ratings yet

- Analyzing The Potential Benefits and Use Cases o - 2023 - BenchCouncil TransactiDocument10 pagesAnalyzing The Potential Benefits and Use Cases o - 2023 - BenchCouncil TransactiRiddhesh PatelNo ratings yet

- Kotlin Coroutines Cheat Sheet PDFDocument1 pageKotlin Coroutines Cheat Sheet PDFgeiledeutscheNo ratings yet

- Resonant Inverter OrCADDocument13 pagesResonant Inverter OrCADCh ChristianNo ratings yet

- Theory of Interactive FictionDocument438 pagesTheory of Interactive Fictionscpedicini1199100% (1)

- Affidavit of Non-SignatureDocument2 pagesAffidavit of Non-SignatureABAABA75% (4)

- RC4 Basics PresentationDocument14 pagesRC4 Basics PresentationKiruthikaBalasubramanianNo ratings yet

- M&a Product SummaryDocument34 pagesM&a Product SummaryMartinez Mauricio Martinez GomezNo ratings yet

- FullDocument35 pagesFullsumanth100% (1)

- University Question Bank PDFDocument16 pagesUniversity Question Bank PDFlathavenkyNo ratings yet

- Rony Das CV New E-MailDocument3 pagesRony Das CV New E-Mailrony_27No ratings yet

- CEO Transformation BrochureDocument5 pagesCEO Transformation BrochureAnonymous 6KiAQNm100% (1)

- M.E. EdDocument101 pagesM.E. EdLoot KingNo ratings yet

- Making a Python list of namesDocument14 pagesMaking a Python list of namesSoniaNo ratings yet

- Andromax Product Defect RatesDocument12 pagesAndromax Product Defect Ratesanat17No ratings yet

- HP Superdome 2 Partitioning Administrator Guide (5900-2540, December 2012) PDFDocument126 pagesHP Superdome 2 Partitioning Administrator Guide (5900-2540, December 2012) PDFSladur BgNo ratings yet

- State of Michigan: (Insert System or Project Name Here) (Inset Phase or Product Increment)Document5 pagesState of Michigan: (Insert System or Project Name Here) (Inset Phase or Product Increment)SamNo ratings yet

- Interface Trip StopDocument3 pagesInterface Trip StopRamesh Garikapati100% (1)

- Technic Error CodesDocument1 pageTechnic Error CodesprajwalNo ratings yet

- DJVUDocument2 pagesDJVUEric FansiNo ratings yet

- DigiKeyboard 6keysDocument7 pagesDigiKeyboard 6keysHarald DasselNo ratings yet

- Whats NewDocument12 pagesWhats Newmerrysun22No ratings yet

- Engineering Seminar TopicsDocument4 pagesEngineering Seminar Topicsmahek19579328No ratings yet