Professional Documents

Culture Documents

MOS Transistor: Prof. Niknejad

Uploaded by

WalidOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

MOS Transistor: Prof. Niknejad

Uploaded by

WalidCopyright:

Available Formats

EECS 105 Fall 2003, Lecture 11

Lecture 11:

MOS Transistor

Prof. Niknejad

Department of EECS

University of California, Berkeley

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

Lecture Outline

Review: MOS Capacitors Regions

MOS Capacitors (3.8 3.9)

CV Curve

Threshold Voltage

MOS Transistors (4.1 4.3):

Overview

Cross-section and layout

I-V Curve

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

MOS Capacitor

Oxide (SiO2)

ox 3.9 0

Gate (n+ poly)

0

Body (p-type substrate)

Very Thin!

tox ~ 1nm

s 11.7 0

MOS = Metal Oxide Silicon

Sandwich of conductors separated by an insulator

Metal is more commonly a heavily doped polysilicon

layer n+ or p+ layer

NMOS p-type substrate, PMOS n-type substrate

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

Accumulation: VGB < VFB

QG Cox (VGB VFB )

VGB VFB

QB QG

++++++++++++++++++

Body (p-type substrate)

( x)

( x)

Essentially a parallel plate capacitor

Capacitance is determined by oxide thickness:

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

Depletion: VFB<VGB < VT

QG (VGB ) QB

VGB VFB +

( x)

tox

++ + + + + + + ++

Body (p-type substrate)

( x)

QB qN a X d (VGB )

Positive charge on gate terminates on negative charges in

depletion region

Potential drop across the oxide and depletion region

Charge has a square-root dependence on applied bias

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

Inversion

s

VGB VT

ns ni e

tox

xdep

++ + + + + + + ++

Body (p-type substrate)

( x)

qs

kT

( x)

Na

The surface potential increases to a point where the electron

density at the surface equals the background ion density

At this point, the depletion region stops growing and the

extra charge is provided by the inversion charge at surface

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

Threshold Voltage

The threshold voltage is defined as the gate-body voltage

that causes the surface to change from p-type to n-type

For this condition, the surface potential has to equal the

negative of the p-type potential

Apply KCL around loop:

Gate (n poly)

V V

VGS VFB Vox VBS

GB

VBS

s VBS 2 p

s

Vox Eox tox

tox Es

ox

qN a xdep qN a 2 s

2qN a (2 p )

Es

s

s

s qN a

s

1

VTn VFB 2 p

2q s N a (2 p )

Cox

Vox

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

Inversion Stops Depletion

A simple approximation is to assume that once

inversion happens, the depletion region stops

growing

This is a good assumption since the inversion

charge is an exponential function of the surface

potential

Under this condition:

QG (VTn ) QB ,max

QG (VGB ) Cox (VGB VTn ) QB ,max

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

Q-V Curve for MOS Capacitor

QG

er

v

in

dep

ac

m

cu

io

at

l

u

l et i o

on

i

s

QN (VGB )

QB ,max

VFB

VTn

VGB (V )

In accumulation, the charge is simply proportional

to the applies gate-body bias

In inversion, the same is true

In depletion, the charge grows slower since the

voltage is applied over a depletion region

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

Numerical Example

MOS Capacitor with p-type substrate:

tox 20nm

N a 5 1016 cm 3

Calculate flat-band:

VFB (n p ) (550 (402)) 0.95V

Calculate threshold voltage:

ox 3.45 1013 F/cm

Cox

tox

2 10-6 cm

1

VTn VFB 2 p

2q s N a (2 p )

Cox

2 1.6 1019 1.04 1012 5 1016 2 0.4

VTn .95 2(0.4)

0.52V

Cox

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

Num Example: Electric Field in Oxide

Apply a gate-to-body voltage:

VGB 2.5 VFB

Device is in accumulation

The entire voltage drop is across the oxide:

Vox VGB n p 2.5 0.55 (0.4)

5 V

Eox

10

tox

tox

2 106

cm

The charge in the substrate (body) consist of holes:

QB Cox (VGB VFB ) 2.67 107 C/cm 2

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

Numerical Example: Depletion Region

In inversion, whats the depletion region width and

charge?

VB ,max s p p p 2 p 0.8V

VB ,max

X d ,max

1 qN a

2

X

d ,max

2 s

2 sVB ,max

qN a

144nm

QB ,max qN a X d ,max 1.15 107 C/cm 2

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

MOS CV Curve

QG

Cox

Cox

QN (VGB )

QB ,max

VFB

VTn

VGB (V )

VFB

VTn

VGB

Small-signal capacitance is slope of Q-V curve

Capacitance is linear in accumulation and inversion

Capacitance is depletion region is smallest

Capacitance is non-linear in depletion

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

C-V Curve Equivalent Circuits

Cox

Cdep

Cox

Cdep Cox

Cox

Cox

Ctot

Cdep

s tox

Cdep Cox

1

1

ox xdep

Cox

In accumulation mode the capacitance is just due to the

voltage drop across tox

Cdep

xdep

Cox

In inversion the incremental charge comes from the

inversion layer (depletion region stops growing).

In depletion region, the voltage drop is across the oxide and

the depletion region

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

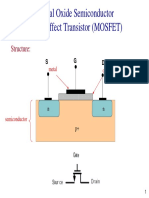

MOSFET Cross Section

gate

body

source

drain

diffusion regions

p+

n+

n+

p-type substrate

Add two junctions around MOS capacitor

The regions forms PN junctions with substrate

MOSFET is a four terminal device

The body is usually grounded (or at a DC potential)

For ICs, the body contact is at surface

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

MOSFET Layout

poly gate

contact

G

B

p+

n+

n+

xj

p-type substrate

L

Planar process: complete structure can be specified

by a 2D layout

Design engineer can control the transistor width W

and L

Process engineer controls tox, Na, xj, etc.

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

PMOS & NMOS

G

B

p+

n+

G

B

n+

p+

n+

xj

p-type substrate

NMOS

p+

xj

n-type substrate

PMOS

A MOSFET by any other name is still a MOSFET:

NMOS, PMOS, nMOS, pMOS

NFET, PFET

IGFET

Other flavors: JFET, MESFET

CMOS technology: The ability to fabricated NMOS

and PMOS devices simultaneously

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

CMOS

G

p+

n+

n+

xj

n+

p+

p+

xj

n-type well

PMOS

NMOS

p-type substrate

Complementary MOS: Both P and N type devices

Create a n-type body in a p-type substrate through

compensation. This new region is called a well.

To isolate the PMOS from the NMOS, the well must be

reverse biased (pn junction)

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

Circuit Symbols

The symbols with the arrows are typically used in

analog applications

The body contact is often not shown

The source/drain can switch depending on how the

device is biased (the device has inherent symmetry)

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

Observed Behavior: ID-VGS

I DS

I DS

VDS

VGS

VT

VGS

Current zero for negative gate voltage

Current in transistor is very low until the gate

voltage crosses the threshold voltage of device

(same threshold voltage as MOS capacitor)

Current increases rapidly at first and then it finally

reaches a point where it simply increases linearly

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

Observed Behavior: ID-VDS

VGS 4V

I DS / k

non-linear resistor region

resistor region

I DS

constant current

VDS

VGS 3V

VGS

VGS 2V

VDS

For low values of drain voltage, the device is like a resistor

As the voltage is increases, the resistance behaves non-linearly

and the rate of increase of current slows

Eventually the current stops growing and remains essentially

constant (current source)

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

Linear Region Current

VGS VTn

S

p+

G

D

n+

n+

p-type

NMOS

VDS 100mV

x

Inversion layer

channel

If the gate is biased above threshold, the surface is

inverted

This inverted region forms a channel that connects

the drain and gate

If a drain voltage is applied positive, electrons will

flow from source to drain

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

MOSFET Linear Region

The current in this channel is given by

I DS Wv y QN

The charge proportional to the voltage applied

across the oxide over threshold

QN Cox (VGS VTn )

I DS Wv y Cox (VGS VTn )

If the channel is uniform density, only drift current

flows

VDS

v y n E y

I DS

W

nCox (VGS VTn )VDS

L

Ey

VGS VTn VDS 100mV

EECS 105 Fall 2003, Lecture 11

Prof. A. Niknejad

MOSFET: Variable Resistor

Notice that in the linear region, the current is

proportional to the voltage

I DS

W

nCox (VGS VTn )VDS

L

Can define a voltage-dependent resistor

VDS

1

L

L

Req

RW(VGS )

I DS n Cox (VGS VTn ) W

W

This is a nice variable resistor, electronically

tunable!

You might also like

- EE230 - Fall 2014 Chapter 5: The MOS Capacitor Chapter 6: The MOS TransistorDocument14 pagesEE230 - Fall 2014 Chapter 5: The MOS Capacitor Chapter 6: The MOS TransistorSaied Aly SalamahNo ratings yet

- Mosfet OperationDocument70 pagesMosfet OperationTanmayBangaloreNo ratings yet

- Short Channel EffectsDocument15 pagesShort Channel Effectsgene_palencia100% (1)

- Chapter 3 Metal Oxide Semiconductor (MOS)Document64 pagesChapter 3 Metal Oxide Semiconductor (MOS)Jay Chandra DharNo ratings yet

- 15 MOSFET Threshold VoltageDocument25 pages15 MOSFET Threshold VoltagetweleNo ratings yet

- Threshold VoltageDocument33 pagesThreshold Voltagemjmanish100% (1)

- MOSFETs - An introduction to metal oxide semiconductor field effect transistorsDocument25 pagesMOSFETs - An introduction to metal oxide semiconductor field effect transistorsZZZZZ5No ratings yet

- Lect13 MosfetDocument8 pagesLect13 MosfetAbhay ChaudharyNo ratings yet

- MOSFET Device Operation: AccumulationDocument8 pagesMOSFET Device Operation: AccumulationMohit SoodNo ratings yet

- Ee3 Mosfet ReviewDocument58 pagesEe3 Mosfet ReviewkaaashuNo ratings yet

- Lecture 15: MOS Transistor Models: Body Effects, SPICE ModelsDocument18 pagesLecture 15: MOS Transistor Models: Body Effects, SPICE Modelsسهيل اصغرNo ratings yet

- Mos Operating Modes & Regions: By-Bhushan MDocument23 pagesMos Operating Modes & Regions: By-Bhushan MbgskkNo ratings yet

- Mos ModelsDocument39 pagesMos Modelsch0071No ratings yet

- MOS Rabaey PDFDocument32 pagesMOS Rabaey PDFalamgirNo ratings yet

- MIT Subthreshold OperationDocument29 pagesMIT Subthreshold Operationsanjeevsoni64No ratings yet

- Ch. 5 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsDocument42 pagesCh. 5 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsChenming HuNo ratings yet

- Mosfet TheoreticalexerciseDocument3 pagesMosfet TheoreticalexercisebrettyNo ratings yet

- Metal Oxide Semiconductor TransistorsDocument39 pagesMetal Oxide Semiconductor TransistorsK MukundNo ratings yet

- MOS TransistorDocument21 pagesMOS TransistorAbhishek Singh100% (1)

- The MOS Capacitor: N Polysilicon Gate Gate Oxide 3.9 0Document10 pagesThe MOS Capacitor: N Polysilicon Gate Gate Oxide 3.9 0VLSI_IITRNo ratings yet

- VLSI DESIGN: MOS TRANSISTORDocument162 pagesVLSI DESIGN: MOS TRANSISTORBasheer V.PNo ratings yet

- VLSI Notes 1 PDFDocument305 pagesVLSI Notes 1 PDFKishore KumarNo ratings yet

- MOS Transistor Principles and Digital Integrated CircuitsDocument371 pagesMOS Transistor Principles and Digital Integrated CircuitsyeswanthNo ratings yet

- 01chapter 5-1Document55 pages01chapter 5-1AhmNo ratings yet

- Mos Transistor Review: 3D Band Diagram of A Long Channel Enhancement Mode NMOS TransistorDocument14 pagesMos Transistor Review: 3D Band Diagram of A Long Channel Enhancement Mode NMOS TransistorKumar Amit VermaNo ratings yet

- Bakir Chapter5Document91 pagesBakir Chapter5mehtajay1993No ratings yet

- MOS Transistor Operation: S/D GateDocument10 pagesMOS Transistor Operation: S/D GateConcetto CantoneNo ratings yet

- 2 Threshold Voltage PDFDocument8 pages2 Threshold Voltage PDFTolias EgwNo ratings yet

- Analog Cmos Ic Design Unit-1Document50 pagesAnalog Cmos Ic Design Unit-1anil kumarNo ratings yet

- Electronics Ch5Document30 pagesElectronics Ch5Santi Navarro MoralNo ratings yet

- MOSFET Physical Operation (Cont'd) MOSFET Current/Voltage CharacteristicsDocument16 pagesMOSFET Physical Operation (Cont'd) MOSFET Current/Voltage CharacteristicsSuleman KhanNo ratings yet

- NMOS & PMOS Transistor CharacteristicsDocument59 pagesNMOS & PMOS Transistor CharacteristicsNaty Dasilva Jr.No ratings yet

- MOS PPTDocument13 pagesMOS PPTRenju TjNo ratings yet

- ELL 740 Compact Modeling of Semiconductor Devices: Dr. Abhisek DixitDocument38 pagesELL 740 Compact Modeling of Semiconductor Devices: Dr. Abhisek DixitChandan JhaNo ratings yet

- MOS TheoryDocument8 pagesMOS TheoryPrathamesh ChawanNo ratings yet

- MOS Capacitor - Ideal: ECSE 2210, Microelectronics Technology, Prof. E. F. SchubertDocument12 pagesMOS Capacitor - Ideal: ECSE 2210, Microelectronics Technology, Prof. E. F. Schubertilg1No ratings yet

- DiodeDocument19 pagesDiodekeshavkthakurNo ratings yet

- DSM Lecture 1Document57 pagesDSM Lecture 1dmv4mgsNo ratings yet

- Lecture 12Document34 pagesLecture 12sridharmtechNo ratings yet

- Analog & Digital Electronics: Course No: Ph-218 Lec-26: Metal Oxide Field Effect Transistors (Mosfets)Document16 pagesAnalog & Digital Electronics: Course No: Ph-218 Lec-26: Metal Oxide Field Effect Transistors (Mosfets)Udai SinghNo ratings yet

- Dr. Navneet Gupta's Lectures on MOSFET FundamentalsDocument51 pagesDr. Navneet Gupta's Lectures on MOSFET FundamentalsKapilAgrawalNo ratings yet

- Lecture Note 1Document120 pagesLecture Note 1LinhHoàngTrươngNo ratings yet

- Slimming World, Jun 2011Document5 pagesSlimming World, Jun 2011emediageNo ratings yet

- ARUSlecture7 fm5-1 PDFDocument14 pagesARUSlecture7 fm5-1 PDFEmmaMaemunahNo ratings yet

- Solns 6Document13 pagesSolns 6api-3750190No ratings yet

- Mos Transistor TheoryDocument144 pagesMos Transistor TheorymailtolokiNo ratings yet

- HighVoltageEngineering PDFDocument46 pagesHighVoltageEngineering PDFBruno LopesNo ratings yet

- Ee560 Mos Theory p101Document22 pagesEe560 Mos Theory p101kunjanb11No ratings yet

- CMOS Inverter Process Flow and PMOS DerivationDocument7 pagesCMOS Inverter Process Flow and PMOS DerivationHammad SattiNo ratings yet

- Theory of Microwave Valves: International Series of Monographs on Electronics and InstrumentationFrom EverandTheory of Microwave Valves: International Series of Monographs on Electronics and InstrumentationNo ratings yet

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterFrom EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterNo ratings yet

- Electronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1From EverandElectronic Devices and Circuits: The Commonwealth and International Library: Electrical Engineering Division, Volume 1No ratings yet

- Maxwell's Equations and Their Consequences: Elementary Electromagnetic TheoryFrom EverandMaxwell's Equations and Their Consequences: Elementary Electromagnetic TheoryNo ratings yet

- Geophysical Field Theory and Method, Part C: Electromagnetic Fields IIFrom EverandGeophysical Field Theory and Method, Part C: Electromagnetic Fields IINo ratings yet

- Feynman Lectures Simplified 2B: Magnetism & ElectrodynamicsFrom EverandFeynman Lectures Simplified 2B: Magnetism & ElectrodynamicsNo ratings yet

- Construct Stick Diagrams in Two StepsDocument5 pagesConstruct Stick Diagrams in Two StepsDebalina PandaNo ratings yet

- EEE 5321 Sp24 HW1 Ver2 020524Document4 pagesEEE 5321 Sp24 HW1 Ver2 020524Towsif Muhtadi KhanNo ratings yet

- SNM of SramDocument6 pagesSNM of SramhaianhlhpNo ratings yet

- Taiwan Semiconductor Manufacturing Co., LTDDocument99 pagesTaiwan Semiconductor Manufacturing Co., LTDLiang CrowNo ratings yet

- A 32 KB 10T Sub-Threshold Sram Array With Bit-Interleaving and DiDocument10 pagesA 32 KB 10T Sub-Threshold Sram Array With Bit-Interleaving and DiSreyas MohanNo ratings yet

- NMOS - Inverter - PDF Version 1Document50 pagesNMOS - Inverter - PDF Version 1Al AminNo ratings yet

- Department of Electronics & Communication Engineering: Mini ProjectDocument12 pagesDepartment of Electronics & Communication Engineering: Mini ProjectNagarajNo ratings yet

- A Logic-Compatible EDRAM Compute-In-Memory With Embedded ADCs For Processing Neural NetworksDocument13 pagesA Logic-Compatible EDRAM Compute-In-Memory With Embedded ADCs For Processing Neural NetworksHelloNo ratings yet

- Isscc2018 31 DigestDocument17 pagesIsscc2018 31 DigestJiaxiang LiuNo ratings yet

- Chap 2 Threshold VoltageDocument20 pagesChap 2 Threshold VoltageratnavaliNo ratings yet

- With Help From David Szmyd, Silicon LabsDocument38 pagesWith Help From David Szmyd, Silicon LabsYidnekachwe MekuriaNo ratings yet

- A 1-Gbs, 0.7 Um CMOS Optical Receiver With Full Rail-to-Rail Output SwingDocument7 pagesA 1-Gbs, 0.7 Um CMOS Optical Receiver With Full Rail-to-Rail Output SwingGrigNo ratings yet

- EC8661 VLSI Design Lab ManualDocument76 pagesEC8661 VLSI Design Lab ManualN.S.Priyanga 33100% (3)

- ECEN474: (Analog) VLSI Circuit Design Fall 2012: Lecture 2: MOS Transistor ModelingDocument25 pagesECEN474: (Analog) VLSI Circuit Design Fall 2012: Lecture 2: MOS Transistor Modelingohenri100No ratings yet

- Unit # 5 Dynamic Cmos and ClockingDocument15 pagesUnit # 5 Dynamic Cmos and ClockingKiran KumariNo ratings yet

- ICT Exp 1 - CMOS Inverter Layout & SimulationDocument2 pagesICT Exp 1 - CMOS Inverter Layout & SimulationShameem ShaikNo ratings yet

- PSET 3 MOS Logic Gates - QDocument4 pagesPSET 3 MOS Logic Gates - QramchanduriNo ratings yet

- Silv ProgrammingDocument85 pagesSilv ProgrammingAadil ShNo ratings yet

- Voltage Buffer: Source Follower (Common-Drain AmplifierDocument40 pagesVoltage Buffer: Source Follower (Common-Drain AmplifierBenj MendozaNo ratings yet

- Basic VLSI SlidesDocument91 pagesBasic VLSI SlidesDivya AhujaNo ratings yet

- U2 U3 Xbox OneDocument14 pagesU2 U3 Xbox OneCheckpoint Game CenterNo ratings yet

- Tinkercad Circuits Components (ALL)Document3 pagesTinkercad Circuits Components (ALL)bob100% (1)

- Design and Implementation of Sychronous 4-Bit Up Counter Using Cmos 90Nm TechnologyDocument46 pagesDesign and Implementation of Sychronous 4-Bit Up Counter Using Cmos 90Nm TechnologyManojkumar KalyanapuNo ratings yet

- ECE 126 - 2 Input NAND Gate Schematic + Test Benches (40chDocument20 pagesECE 126 - 2 Input NAND Gate Schematic + Test Benches (40chraghuippiliNo ratings yet

- Circuit Layout EulerDocument72 pagesCircuit Layout Eulerជើងកាង ភូមិNo ratings yet

- (Power Systems) Wen-Wei Chen, Jiann-Fuh Chen (Auth.) - Control Techniques For Power Converters With Integrated Circuit-Springer Singapore (2018)Document195 pages(Power Systems) Wen-Wei Chen, Jiann-Fuh Chen (Auth.) - Control Techniques For Power Converters With Integrated Circuit-Springer Singapore (2018)archssiNo ratings yet

- Design of CMOS Circuit Based On NAND Function at 150nm Channel Length For Low-Power and High-Speed IC FabricationDocument6 pagesDesign of CMOS Circuit Based On NAND Function at 150nm Channel Length For Low-Power and High-Speed IC FabricationIJRASETPublicationsNo ratings yet

- SRM Valliammai Engineering College: Department of Electronics and Communication EngineeringDocument11 pagesSRM Valliammai Engineering College: Department of Electronics and Communication EngineeringRamaNo ratings yet

- 1-VLCI ItrodutionDocument15 pages1-VLCI Itrodutionbhieestudents100% (1)